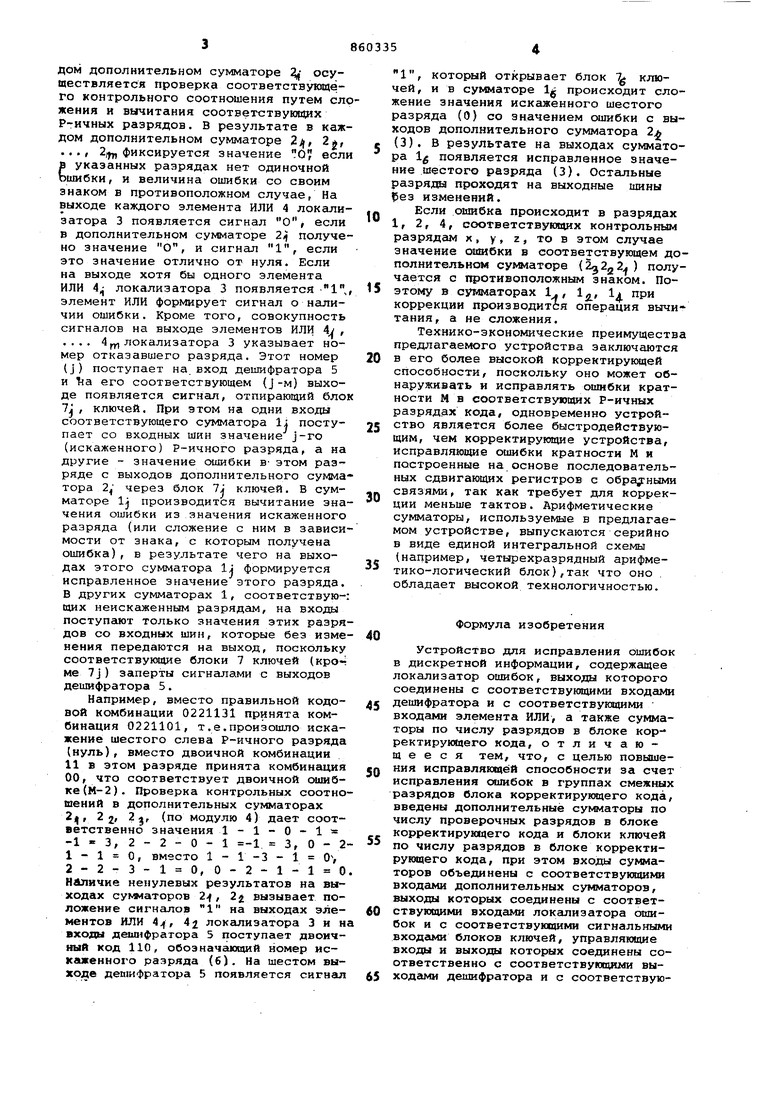

(54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В ДИСКРЕТНОЙ ИНФОРМАЦИИ Изобретение относится к электросвязи и может использоваться в много.канальных системах передачи информации . Известно устройство для исправления ошибок в дискретной информации, содержащее локалиэатор ошибок, выходы которого соединены с соответств гацими входами дешифратора и с соответствующими входами элемента ИЛИ, а также сумматоры по числу разрядов в блоке корректирующего кода .l. Однако известное устройство обеспечивает исправление только одной ошибки и не Лоэволяет обнаруживать и исправлять ошибки в М смежных двоичных разрядах. Цель изобретения - повышение исправляющей способности за счет испра Ленин ошибок в группах смежных разря дов блока корректирующего кода, Для достижения цели в устройство для исправления ошибок в дискретной информации, содержащее локализатор оьшбок,выходы которого соединены с соответствукхцими входами д гшифратор Н с соответствукицими входами элемента ИЛИ, а также сумматоры по числу {разрядов в блоке корректирукщего ко|даг введены дополнительные сумматоры о числу проверочных разрядов в блоке корректирующего кода и блоки ключей по числу разрядов в блоке корректирующего кода, при этом входы сумматоров объединены с соответствующими входами дополнительных сумматоров, выходы которых соединены с соответствующими входами локализатора оишбок и с соответствуквдими сигнальными входами блоков ключей, управляющие входы и выходы которых соединены соответственно с соответствующими выходами дешифратора и с соответствукицими входами сумматоров , а локалиэатор ошибок состоит из элементов ИЛИ по числу проверочных разрядов в блоке корректирукадего кода. На чертеже приведена структурная электрическая схема предложенного устройства. ,-, Устройство содержит сумматоры l-.-l, дополнительные сумматоры 2 , 22,..., 2|,, локализатор 3 ошибок, состоящий из элементов ИЛИ 4jj, 42/..., 4 дешифратор5, элемент ИЛИ 6, блоки 7, Tji.. 7 ключей. Устройство работает следующим Ьбразом. При поступлении по .входным шинам входнс),го корректирующего кода в кажДОМ дополнительном сумматоре 7 осуществляется проверка соответствующего контрольного соотношения путем сложения и вычитания соответствуювшх Р-ичных разрядов. В результате в каждом дополнительном сумматоре 2jj, 2л, ..., 2,1 фиксируется значение ОУ если в указанных разрядах нет одиночной ошибки, и величина ошибки со своим знаком в противоположном случае, На выходе каждого элемента ИЛИ 4 локализатора 3 появляется сигнал О, если в дополнительном сумматоре 2ij получено значение О, и сигнал 1, если это значение отлично от нуля. Если на выходе хотя бы одного элемента ИЛИ 4 локализатора 3 появляется , элемент ИЛИ формирует сигнал о наличии ошибки. Кроме того, совокупность сигналов на выходе элементов ИЛИ 4 , .... 4 локализатора 3 указывает номер отказавшего разряда. Этот номер (J) поступает на вход дешифратора 5 и Tia его соответствующем {J -м) выходе появляется сигнал, отпирающий блок 7j , ключей. При этом на одни входы соответствующего сумматора li поступает со входных шин значение j-ro (искаженного) Р-ичного разряда, а на другие - значение ошибки в- этом разряде с выходов дополнительного сумматора 2| через блок 7; ключей. В сумматоре Ij производится вычитание значения ошибки из значения искаженного разряда (или сложение с ним в зависимости от знака, с которым получена ошибка), в результате чего на выходах этого сумматора Ij формируется исправленное значение этого разряда. В других сумматорах 1, соответствую-: щих неискс1женным разрядам, на входы поступают только значения этих разрядов со входных шин, которые без изменения передаются на выход, поскольку соответствуквдие блоки 7 ключей (кроме 7j) заперты сигналами с выходов дешифратора 5.

Например, вместо правильной кодовой комбинации 02211Э1 принята комбинация 0221101, т.е.произошло искажение шестого слева Р-ичного разряда (нуль), вместо двоичной комбинации 11 в этом разряде принята комбинация 00, что соответствует двоичной ошибке (М-2). Проверка контрольных соотношений в дополнительных сумматорах 2ц, 2 J, (по модулю 4) дает соответственно значения 1-1-0-1 -1-3,2-2-0-1 -1 3,0- , вместо 1 - 1 -3 - 1 0 2-2-3-1 0, 0-2-1-1 0 Н&личие ненулевых результатов на выходах cyNwaTOpoB 2, 2 вызывает пона выходах элеложение сигналов

ментов ИЛИ 4jf, 42 локализатора 3 и на входы дешифратора 5 поступает двоичный код 110, обозначающий номер исх&женного разряда (6). На шестом выходе дешифратора 5 появляется сигнал

1, который открывает блок ключей, и в сумматоре Ig происходит сложение значения искаженного шестого разряда (0) со значением ошибки с выходов дополнительного сумматора 2 е (3). В результате на выходах сумматора 1 появляется исправленное значение шестого разряда (3). Остальные разряды проходят на выходные шины Рез изменений.

Если ошибка происходит в разрядах 1,2,4, соответствующих контрольным разрядам х, у, z, то в этом случае значение ошибки в соответствующем дополнительном сумматоре (,2 ) получается с тфотивоположным знаком. Поэтому в сумматорах 1., 1, 1 при

коррекции производится операция вычитания, а не сложения.

Технико-экономические преимущества предлагаемого устройства заключаются 0 в его более высокой корректирующей способности, поскольку оно может обнаруживать и исправлять ошибки кратности М в соответствующих Р-ичных разрядах кода, одновременно устройство является более быстродействующим, чем корректирующие устройства, исправляющие ошибки кратности М и построенные на основе последовательных сдвигающих регистров с обра гными

связями, так как требует для коррекции меньше тактов. Арифметические сумматоры, используемые в предлагаемом устройстве, выпускаются серийно в виде единой интегральной схемы (например, четырехразрядный арифметико-логический блок),так что оно . обладает высокой технологичностью.

Формула изобретения

Устройство для исправления ошибок в дискретной информации, содержащее локализатор ошибок, выходы которого соединены с соответствующими входами

дешифратора и с соответствующими

входами элемента ИЛИ, а также сумматоры по числу разрядов в блоке кор- ректирующего кода, отличающееся тем, что, с целью повышекия исправляющей способности за счет исправления ошибок в группах смежных разрядов блока корректирующего кода, введены дополнительные сумматоры по числу проверочных разрядов в блоке корректирующего кода и блоки ключей

по числу разрядов в блоке корректирующего кода, при этом входы сумматоров объединены с соответствующими входами дополнительных сумматоров, выходы которых соединены с соответствующими входами локализатора ошибок и с соответствующими сигнальными входами блоков ключей, управляющие входы и выходы которых соединены соответственно с соответствующими выходами дешифратора и с соответствующими входами сумматоров, а локализатор опшбок состоит из элементов ИЛИ по числу проверочных разрядов в блоке корректирующего кода.

14

Источники ИНфОрМсЩИИ,

принятые во внимание при экспертизе

1. Патент США I 3623155,кл.340146.1, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок в дискретной информации | 1980 |

|

SU951740A2 |

| Устройство для исправления ошибок в дискретной информации | 1980 |

|

SU932645A1 |

| Устройство для исправления ошибок | 1986 |

|

SU1383509A1 |

| Устройство для коррекции ошибок в блоках памяти | 1982 |

|

SU1086460A1 |

| Мажоритарный декодер | 1980 |

|

SU890397A1 |

| Устройство для исправления ошибок | 1982 |

|

SU1120335A1 |

| Устройство для исправления ошибок | 1978 |

|

SU721817A1 |

| СПОСОБ ПЕРЕДАЧИ И КОМПЛЕКСНОЙ ЗАЩИТЫ ИНФОРМАЦИИ | 2007 |

|

RU2367007C2 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

ф-- ф ф Ф Ф Ф

Авторы

Даты

1981-08-30—Публикация

1978-06-22—Подача