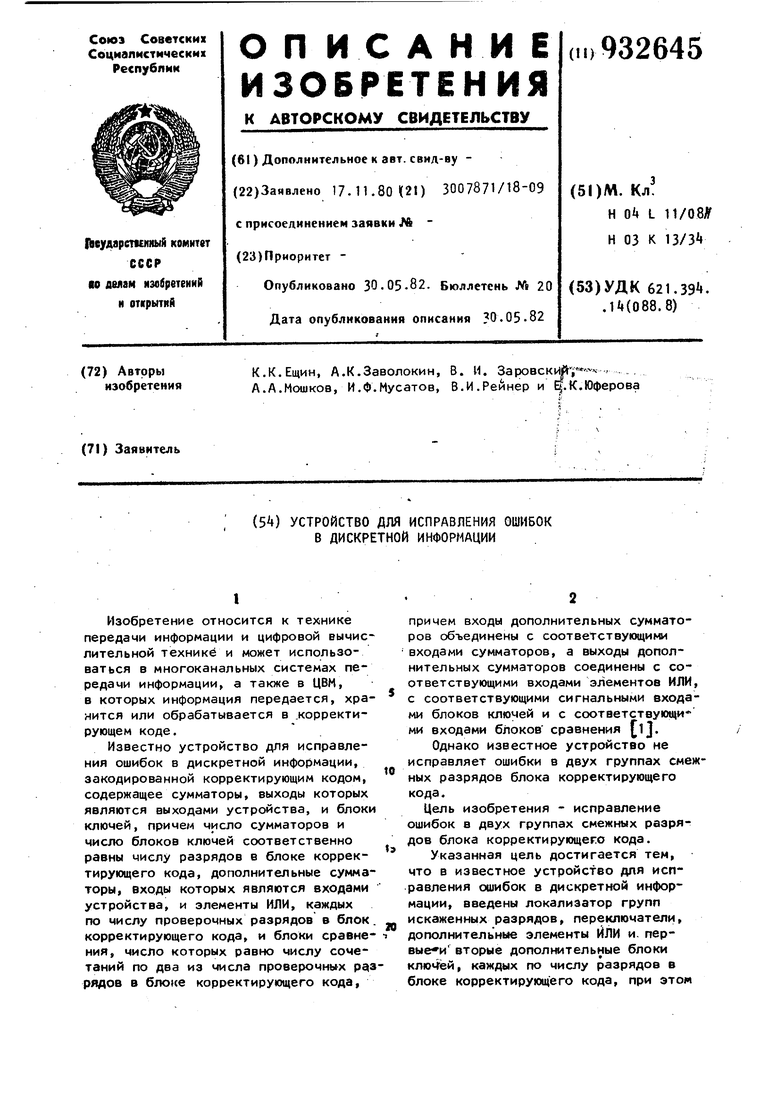

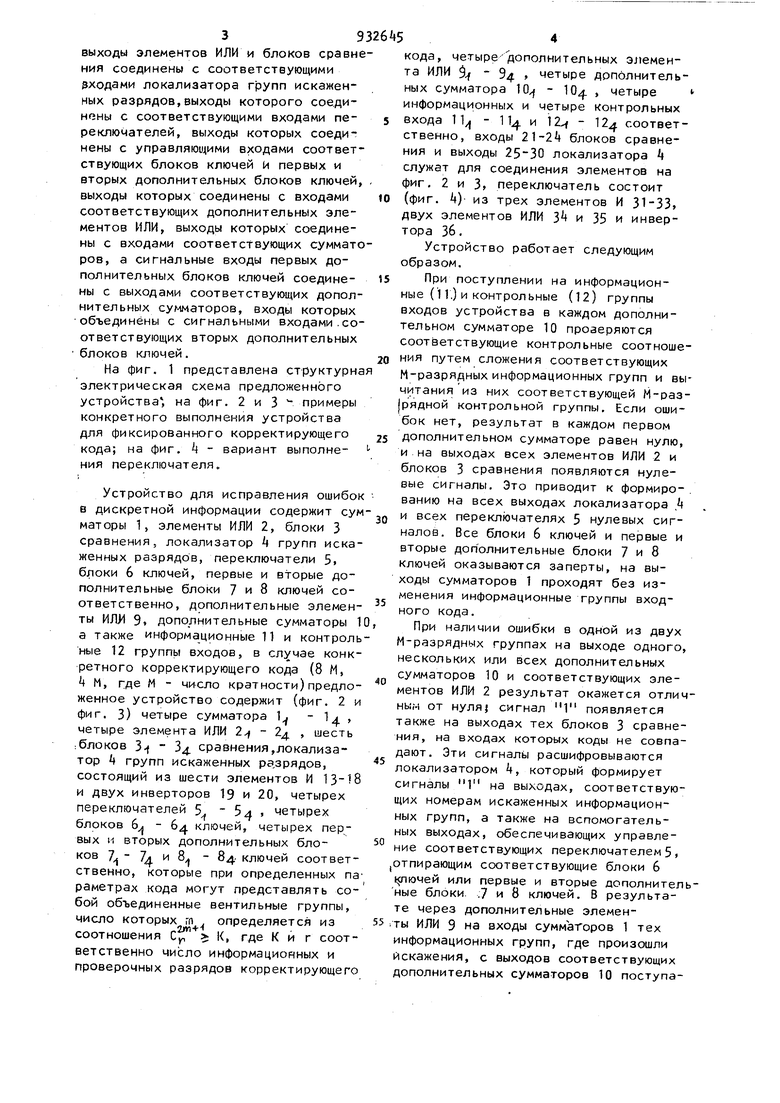

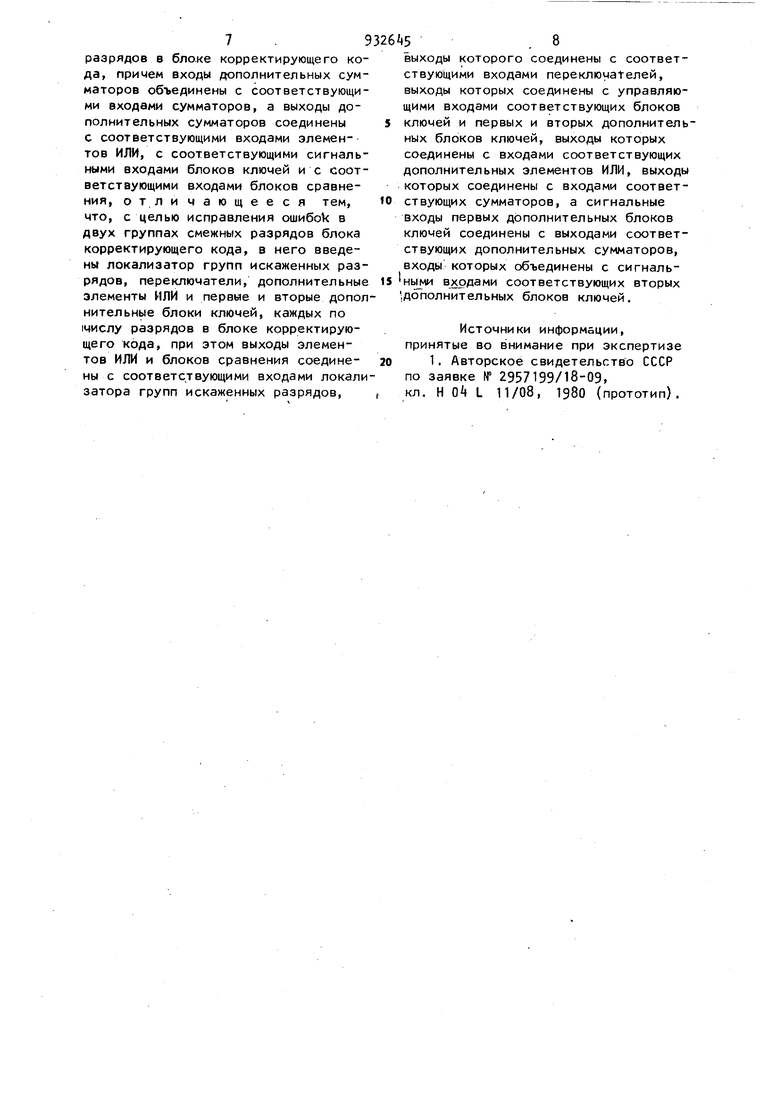

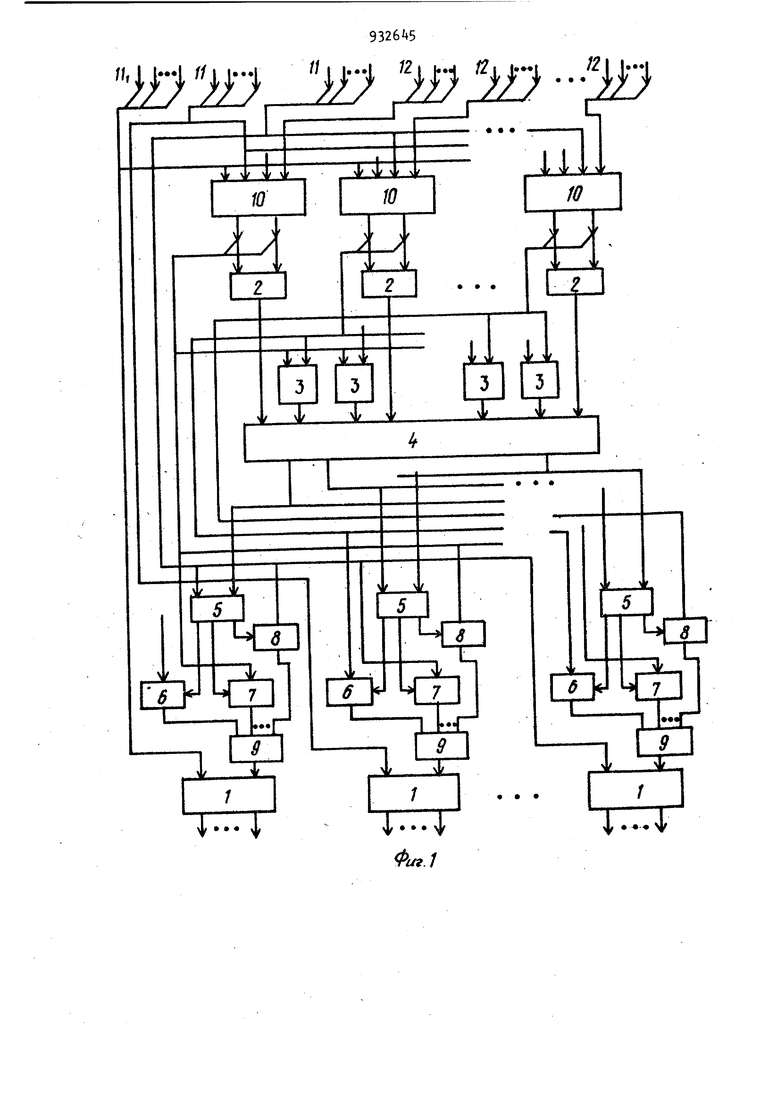

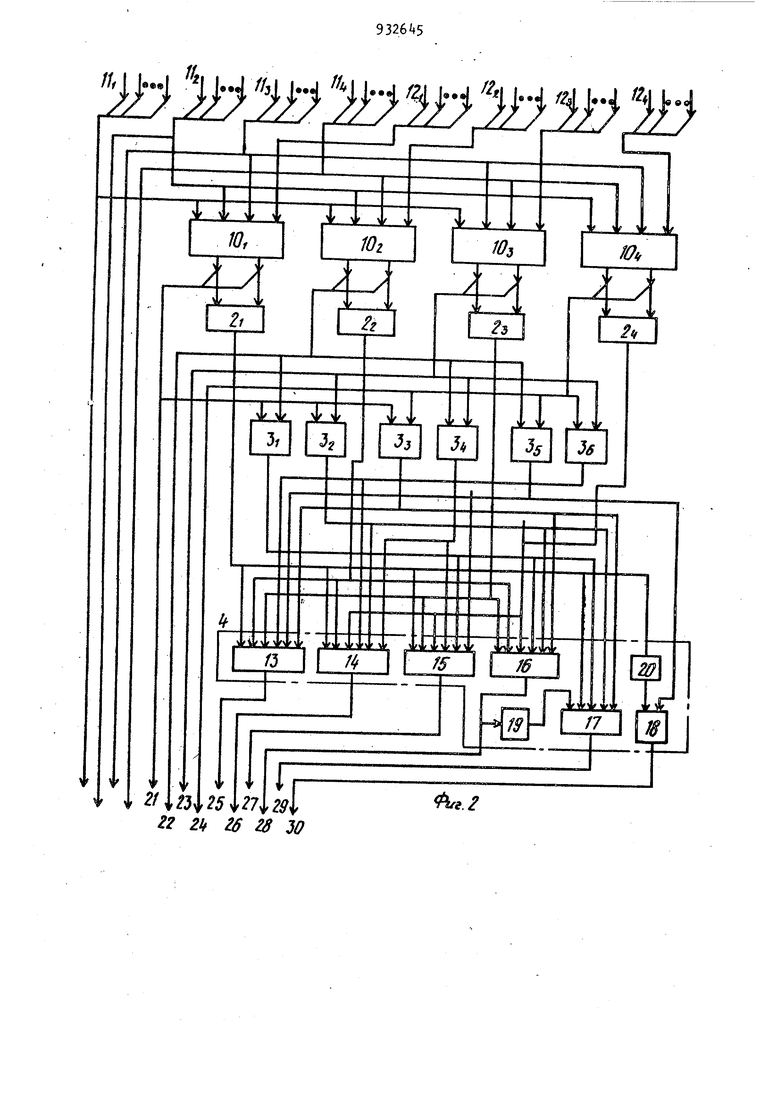

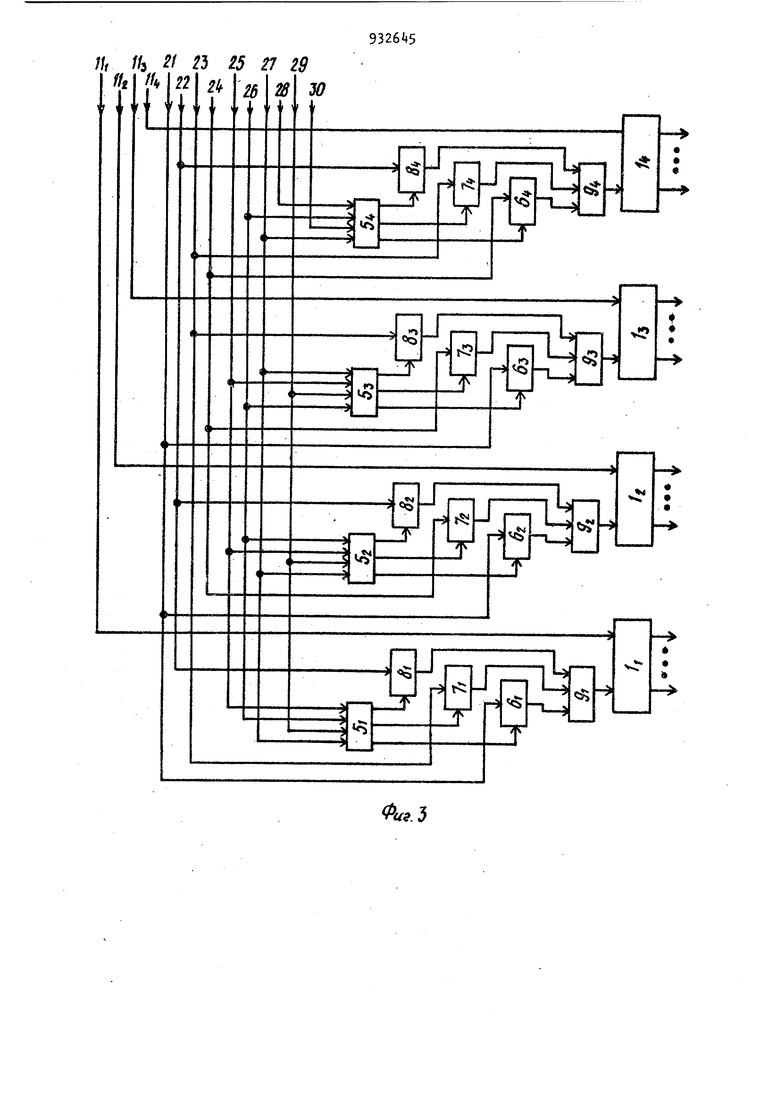

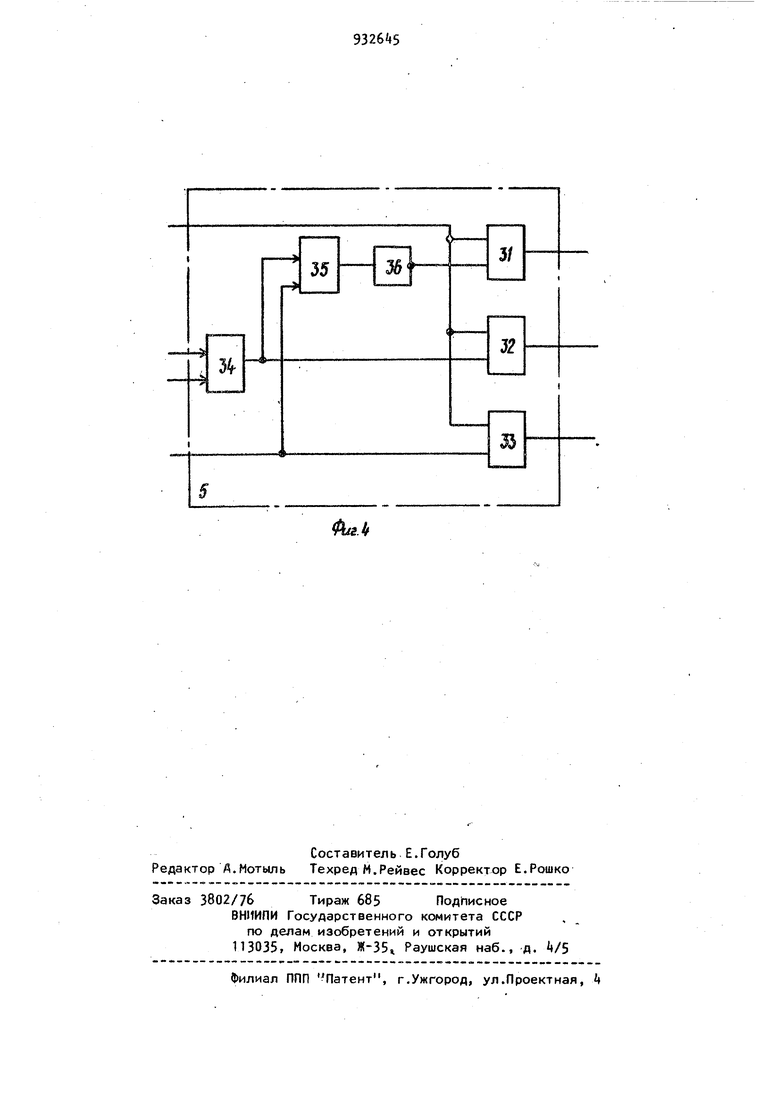

Изобретение относится к технике передачи информации и цифровой вычислительной технике и может использоваться в многоканальных системах передачи информации, а также в ЦВМ, в которых информация передается, хранится или обрабатывается в .корректирующем коде. Известно устройство для исправления ошибок в дискретной информации, закодированной корректирующим кодом, содержащее сумматоры, выходы которых являются выходами устройства, и блоки ключей, причем число сумматоров и число блоков ключей соответственно равны числу разрядов в блоке корректирующего кода, дополнительные сумматоры, входы которых являются входами устройства, и элементы ИЛИ, каждых по числу проверочных разрядов в блок корректирующего кода, и блоки сравнения, число которых равно числу сочетаний по два из числа проверочных рэз рядов в блоке корректирующего кода, причем входы дополнительных сумматоров объединены с соответствующими входами сумматоров, а выходы дополнительных сумматоров соединены с соответствующими входами элементов ИЛИ, с соответствующими сигнальными входами блоков ключей и с соответствующими входами блоков сравнения lj. Однако известное устройство не исправляет ошибки в двух группах смежных разрядов блока корректирующего кода. Цель изобретения - исправление ошибок в двух группах смежных разрядов блока корректирующего кода. Указанная цель достигается тем, что в известное устройство для исправления ошибок в дискретной информации, введены локализатор групп искаженных разрядов, переключатели, дополнительные элементы ИЛИ и. первые и вторые дополнительные блоки ключей, каждых по числу разрядов в блоке корректирующего кода, при этом 39 выходы элементов ИЛИ и блоков сравне ния соединены с соответствующими эходами локализатора групп искаженных разрядов,выходы которого соединены с соответствующими входами переключателей, выходы которых соединены с управляющими входами соответствующих блоков ключей И первых и вторых дополнительных блоков ключей, выходы которых соединены с входами соответствующих дополнительных элементов ИЛИ, выходы которых соединены с входами соответствующих суммато ров, а сигнальные входы первых дополнительных блоков ключей соединены с выходами соответствующих дополнительных сумматоров, входы которых объединены с сигнальными входами.соответствующих вторых дополнительных блоков ключей. На фиг. 1 представлена структурна электрическая схема предложенного устройства , на фиг. 2 и 3 примеры конкретного выполнения устройства для фиксированного корректирующего кода; на фиг. k - вариант выполнения переключателя. Устройство для исправления ошибо в дискретной информации содержит сум маторы 1, элементы ИЛИ 2, блоки 3 сравнения, локализатор групп иска женных разрядов, переключатели 5 блоки 6 ключей, первые и вторые дополнительные блоки 7 и 8 ключей соответственно, дополнительные элемен ты ИЛИ 9 дополнительные сумматоры а также информационные 11 и контрол ные 12 группь входов, в случае конк ретного корректирующего кода (8 М, 4 М, где М - число кратности) предло женное устройство содержит (фиг, 2 и фиг. 3) четыре сумматора 1 - 1 четыре элемента ИЛИ :блоков 3 34 сравнения,локализатор Ц групп искаженных ра,зрядов, состоящий из шести элементов И 13-1 и двух инверторов 19 и 20, четырех переключателей 5. 5л , четырех блоков 6. - 64 ключей, четырех первых и вторых дополнительных блоков 7 - 7л. и 8 - 84- ключей соответ ственно, которые при определенных п раметрах кода могут представлять со бой объединенные вентильные группы, число которых г(1 . определяется из соотношения С К, где К и г соот ветственно число информационных и проверочных разрядов корректирующего кода, четыредополнительных элемента ИЛИ 5 - 94 четыре дополнительных сумматора 10 - Ю. четыре информационных и четыре контрольных входа 11 - 114 и 12-Y - 12 соответственно, входы 21-2 блоков сравнения и выходы 25-30 локализатора Ц служат для соединения элементов на фиг. 2 и 3 переключатель состоит (фиг. k) из трех элементов И 31-33, двух элементов ИЛИ 3 и 35 и инвертора 36. Устройство работает следующим образом. При поступлении на информационные (11.) и контрольные (12) группы входов устройства в каждом дополнительном сумматоре 10 проаеряются соответствующие контрольные соотношения путем сложения соответствующих М-разрядных информационных групп и вычитания из них соответствующей М-раз|рядной контрольной группы. Если ошибок нет, результат в каждом первом дополнительном сумматоре равен нулю, и на выходах всех элементов ИЛИ 2 и блоков 3 сравнения появляются нулевые сигналы. Это приводит к формиро- . ванию на всех выходах локализатора Л и всех переключателях 5 нулевых сигналов. Все блоки 6 ключей и первые и вторые дополнительные блоки 7 и 8 ключей оказываются заперты, на выходы сумматоров 1 проходят без изменения информационные группы входного кода. При наличии ошибки в одной из двух М-разрядных группах на выходе одного, нескольких или всех дополнительных сумматоров 10 и соответствующих элементов ИЛИ 2 результат окажется отличным от нуля} сигнал 1 появляется также на выходах тех блоков 3 сравнения, на входах которых коды не совпадают. Эти сигналы расшифровываются локализатором 4, который формирует сигналы 1 на выходах, соответствующих номерам искаженных информационных групп, а также на вспомогательных выходах, обеспечивающих управление соответствующих переключателем 5, отпирающим соответствующие блоки 6 или первые и вторые дополнительные блоки. .7 и В ключей. В результате через дополнительные элеменгты ИЛИ 9 на входы сумматоров 1 тех информационных групп, где произошли искажения, с выходов соответствующих дополнительных сумматоров 10 поступа59ют коды, соответствующие ошибке, воз никшей в этих группах. Эти коды вычитаются из входных кодов групп и таким образом осуществляется их коррекция. Работа устройства в случае конкретного корректирующего кода (фиг.2, 3 и 4) происходит аналогично. На информационные входы устройства поступают информационные группы разрядов входного кода, на контрольные входы - контрольные группы, сформированные по указанному выше правилу. В дополнительных сумматорах 10 -10 проверяются контрольные соотношения, В которых участвуют контрольные входы 12 - 12. При отсутствии искажения кода на выходах всех дополнитель ных сумматоров 10 - 164 , элементов или 2i - 2я, блоки 3-1 - 3 сравне ния, элементов И , локализатора 4, элементов .И переключателей 5-1 54 всех вентильных групп (6 - 6 . 7 - 74 . 8 - 84) и дополнительных элементов ИЛИ Э. 94-будут нулевые сигналы, и на выход сумматоров 1 - Ц ,эходные информа ционные группы с информационных входов 1 tj 114пройдут без изменения. При наличии искажений в одной или двух контрольных группах разрядов на выходах одного или двух дополнительных сумматоров 10 - 10 появляются результаты, отличные от нуля. На выходах соответствующих элементов ИЛИ и блоков сравнения появляются сигналы 1, однако;5 если ошибки в двух контрольных группах не совпадают, на выходах элементов И 13 - 16 локализатора k сохранятся нулевые сигналы, а состояние всех переключате лей 5 и вентильных групп и дополнительных вентильных групп не изменится, В результате на выходы всех сумматоров 1 - л информационные rpyhrw разрядов пройдут без изменения. При наличии искажений в одной или двух информационных группах (или одной информационной и одной контрольной) на выходах соответствующих элементов ИЛИ и блоков сравнения воз

никает такая комбинация сигналов, чтс появляются сигналы 1 на выходах тех одного или двух элементов И 13 16 локализатора k, которые соответствуют камерам искаженных групп (соот- ветственно первой, второй, третьей и четвертой), а также элемента И 17 лока/1изатора k, если произошло йеначислу разрядов в блоке корректрирующего кода, доп.олнительные сумматоры, входы которых являются входами устройства, и элементы ИЛИ, каждых по числу проверочных разрядов в блоке корректирурощего кода, и блоки сравнения, число которых равКо числу сочетаний по два из числа проверочных 5 жение в первой контрольной группе и нет искажений в четвертой информационной группе, и элемента И 18 локализатора Ц в ряде ситуаций, в томчисле, когда произошло искажение во второй или четвертой контрольной группе. Сигналы с выходов элементов И локализатора открывают один из элементов И соответствующих переключателей 5 5 зависимости от комбинации сигналов на всех выходах локализатора k, В результате для соответствующих групп разрядов открыты соотвётствующие группы вентилей и в сумматорах 1 этих групп разрядов будет осуществлена коррекция. Технико-экономические преимущества предложенного устройства по сравнению с известным заключаются в том, что оно обеспечивает более высокую достоверность выходной информации, так как исправляет не только все ошибки в одной группе, но и подавляющее большинство ошибок в двух М-разрядных группах кода. Не исправляются только такие ошибки в двух группах, сумма которых (для двух информационных групп) или разность (для информационной и контрольной групп) равны нулю, или которые равны между собой Х для двух контрольных группУ. |Это составляет 1/2 ч.всех двойных ошибок (для М число неисправляемых двойных ошибок около 6). По сравнению с устройствами для коррекции ошибок последовательного действия (со сдвигающими регистрами) предложенное устройство обладает более высоким быстродействием. Формула изобретения , Устройство для исправления ошибок в дискретной информации, закодированной корректирующим кодом, содержащее сумматоры, выходы которых являются выходами устройства, и блоки ключей, причем число сумматоров и число блоков ключей соответственно равны

разрядов 8 6ло.ке корректирующего кода, причем входы дополнительных сумматоров объединены с соответствующими входами сумматоров, а выходы дополнительных сумматоров соединены с соответствующими входами элементов ИЛИ, с соответствующими сигнальными входами блоков ключей и с соответствующими входами блоков сравнения, о тли чающееся тем, что, с целью исправления ошибоК в двух группах смежных разрядов блока корректирующего кода, в него введены локализатор групп искаженных разрядов, переключатели, дополнительные элементы ИЛИ и первые и вторые дополнительные блоки ключей, каждых по 1ЧИСЛУ разрядов в блоке корректирующего кода, при этом выходы элементов ИЛИ и блоков сравнения соединены с соответствующими входами локализатора групп искаженных разрядов,

1выходы которого соединены с соответствующими входами переключателей, выходы которых соединены с управляющими входами соответствующих блоков ключей и первых и вторых дополнительных блоков ключей, выходы которых соединены с входами соответствующих дополнительных элементов ИЛИ, выходы которых соединены с входами соответствующих сумматоров, а сигнальные входы первых дополнительных блоков ключей соединены с выходами соответствующих дополнительных сумматоров, входы которых объединены с сигнальнь1ми в хрдами соответствующих вторых дополнительных блоков ключей.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР по заявке № 2957199/18-09, кл. Н ОА L 11/08, 1980 (прототип). /fj I ti i««M h i«« 21 |..j 77 / JD /:, i.t /21 t..,| JU ayiyiw iwittiHiH

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок в дискретной информации | 1978 |

|

SU860335A1 |

| Устройство для исправления ошибок в дискретной информации | 1980 |

|

SU951740A2 |

| Устройство для исправления ошибок | 1986 |

|

SU1383509A1 |

| Устройство для обнаружения и коррекции ошибок памяти | 1986 |

|

SU1377918A1 |

| Устройство для исправления ошибок | 1982 |

|

SU1120335A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Устройство для контроля информации на четность | 1985 |

|

SU1339898A1 |

| Устройство для обнаружения ошибок | 1983 |

|

SU1100746A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1989 |

|

SU1649615A1 |

| Запоминающее устройство с коррекцией однократных ошибок | 1982 |

|

SU1073799A1 |

Z2 2lf 2S 30

Яг //3 21 ;3 25 27 29

f

0W.3

Авторы

Даты

1982-05-30—Публикация

1980-11-17—Подача