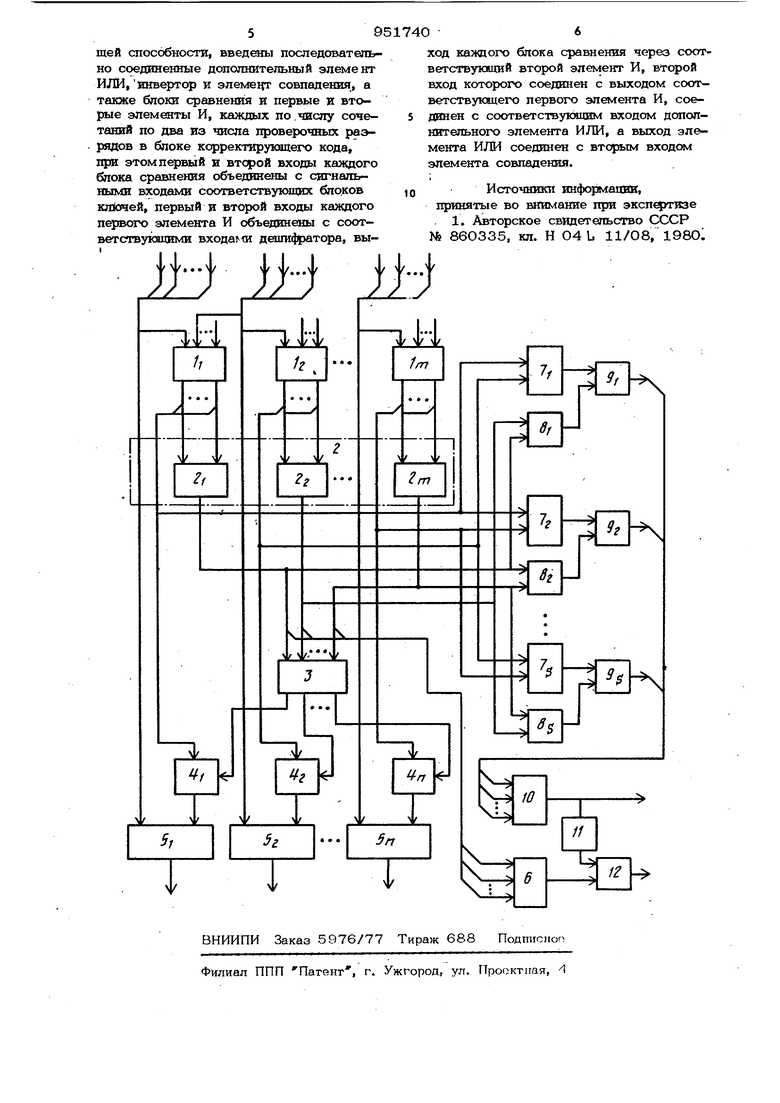

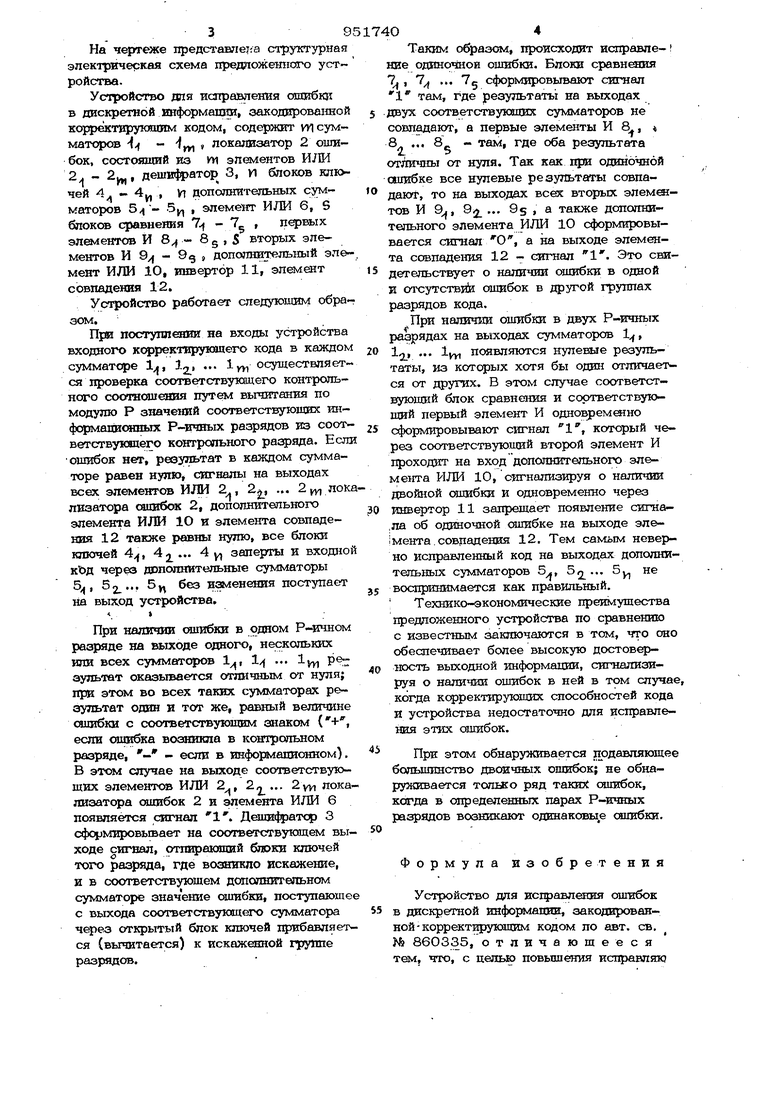

На чертеже предс1 аБ 1е7;а структурная электрическая схема предложешгого устройства.

Устройство для исофйвления сишбкя в дискретной информашш, оакодирова1щой корректирукицим кодом, содержит vtl сумматоров i - -1 , локализатор 2 ошибок, состоящий из И1 элементов ИЛИ 2. - 2, деши йратор 3, К1 блоков ключей 4 - 4 , VI дополнительных сум маторов 5/|- 5 , элемент ИЛИ 6, 6 блоков сравнения 7 - 7 , первых элементов И 8 - 85 S вторых элементов И 9( - 9д , допо шительный эле мент ИЛИ 10, инвертор 11, элемент совпадения 12.

Устройство работает следующим обра эом.

При поступлении на входы устройства входного корректирующего кода в каждом сумматоре 1., 1, ... 1у осуществляется проверка соответствующего контрольного соопгасшения путем вычитания по модулю Р значений соответствующих инфррмадисяшых Р-ичных разрядов из соответствующего контрольного разряда. Если ошибок нет, результат в каждом сумматоре равен нулю, сигналы на выходах всех элементов ИЛИ 2 , 2ff, ... 2, локализатора ошибок 2, дополнительного элемента ИЛИ 10 и элемента совпадения 12 также равны нутпо, все блоки ключей 4, 42... 4 у, заперты и входной кЪд через дополнительные сумматоры 52.... 5ц без изменения поступает на выход устройства. .

При наличии сшибки в одном Р-ичном разряде на выходе одного, нескольких или всех сумматоров 1, 1/ ... Ij реаультат оказывается отличным от нуля; при этом во всех таких сумматорах результат один и тот же, равный величине сшибки с соответствующим знаком {+, если ошибка возникла в контрольном разряде, - - если в информационном). В этом случае на выходе соответствующих элементов ИЛИ 2 , 2.... 2ум локализатора сшшбок 2 и элемента ИЛИ 6 появляется сигнал . Дeшиt|paтqp 3 сфо1 мировьтает на соответствующем выходе сигнал, отпирающий блоки ключей того разряда, где возникло искажение, и в соответствующем дополнительном сумматоре значение ощибки, поступаюиюе с выхода соответствующего сумматора через открытый блок ключей прибавляется (вычитается) к искаженной rpyime разрядов.

Таким образом, происходит исправлеНЕе одиночной ощибки. Блоки сравнения

7. 7,

7д сформировывают сигнал там, где результать на выходах двух соответствующих сумматоров не совпадают, а первые элементы И 8 ,

8.

8 - там, где оба результата

отЛичны от нуля. Так как при одиночной сшибке все нулевые результаты совпадают, то на выходах всех вторых элементов И 9, 9,2 ... 9s , а также дополнительного элемента ИЛИ 1О сформировывается сигнал О, а на выходе элемента с0впаде1Шя 12 - сигнал 1. Это свидетельствует о наличии ощибки в одной И отсутствии ощибок в другой группах разрядов кода.

При наличии ощибки в двух Р-ичных разрядах на выходах сумматоров 1,

1,, ... Ij появляются нулевые результаты, из которых хотя бы один отличается от других. В этом случае соответствующий блок сравнения и соответствующий первый элемент И одновременно

сформировывают сигнал 1, который через соответствую,11ШЙ второй элемент И проходит на вход дополнительного элемента ИЛИ 10, сигнализируя о наличии двойной ошибки и одновременно через

готертор 11 запрещает появление сигна,ла об одиночной сшибке на выходе элеiмента.совпадения 12. Тем самым неверно исправленный код на выходах дополнительных сумматоров 5ж, 52... 5у не

воспринимается как правильный.

Технико-экономические преимущества предложенного устройства по сравнению с известным заключаются в том, что оно обеспечивает более высокую достовер1юсть выходной информации, сигнализируя о наличии ошибок в ней в том случае, когда корректирующих способностей кода И устройства недостаточно для исправления этих ошибок.

При этом обнаруживается пюдавляющее бопзьщинство двоичных ощибок; не обнаруживается только ряд такю4 ощлбок, когда в определенных парах Р-ичных

разрядов возникают одинаковые сшибки.

Формула изобретения

Устройство для исгравления ощвбок в дискретной информации, закодированной - корректирующим кодом по авт. св. № 860335, отличающееся тем, что, с целью повьш1ения исправляю

щей способности введены последовательно соединенные дополнительный элемент ИЛИ, инвертор и элемецт совпадения, а также блоки сравнения и первые и вторые элементы И, каждых по.числу сочетаний по два из числа проверочных разрядов в блоке корректирующего кода, при этом первый и второй входы каждого блока сравнения объединены с сигнальными входами соответствующих блоков ключей, первый и второй входы каждого первого элемента И объединены с соответствующими вxoдa tи дешифратора, выjy -АУ 11::)

ход каядаого блока сравнения через соответствующий второй элемент И, второй вход которого соединен с выходом соответствующего первого элемента И, соединен с соответствующим входом дополнительного элемента ИЛИ, а выход элемента ИЛИ соединен с вторым входом элемента совпадения.

Источники информации, принятые во внимание при экспертизе . 1. Авторское свидетельство NJ 860335, кл. Н 04Ь 11/О8, 19801

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок в дискретной информации | 1978 |

|

SU860335A1 |

| Устройство для исправления ошибок в дискретной информации | 1980 |

|

SU932645A1 |

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1982 |

|

SU1061275A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1081669A1 |

| Устройство для исправления ошибок | 1978 |

|

SU721817A1 |

| Декодирующее устройство двоичныхКОдОВ C КОРРЕКциЕй ОдиНОчНыХ ОшибОК | 1979 |

|

SU815908A1 |

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1982 |

|

SU1115055A1 |

| Устройство для коррекции ошибок в дискретной информации,передаваемой кодом Хемминга | 1980 |

|

SU1040610A1 |

| Устройство для исправления ошибок | 1986 |

|

SU1383509A1 |

| Мажоритарный декодер | 1980 |

|

SU890397A1 |

Авторы

Даты

1982-08-15—Публикация

1980-07-11—Подача