(54) УСТРОЙСТВО ДЛЯ СДВИГА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сдвига информации | 1978 |

|

SU894700A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Устройство для сдвига информации | 1983 |

|

SU1117632A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Устройство для упорядочения слов | 1975 |

|

SU608153A1 |

| Устройство для сдвига информации | 1982 |

|

SU1053101A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1730628A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Цифровой масштабный преобразователь | 1982 |

|

SU1086428A1 |

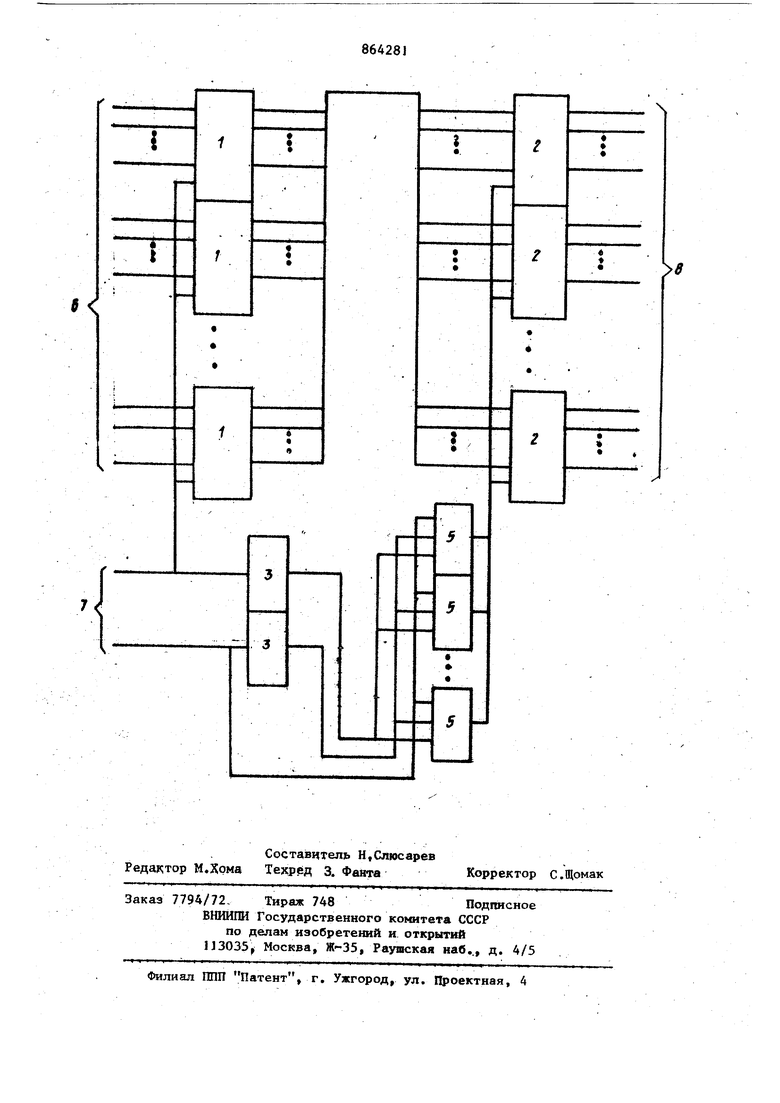

Изобретение относится к вычислительной технике,в частности к устрой ствам коммутации и сдвигали может быть применено в быстродействующих цифровых вычислительных машинах. Известны устройства для циклич1еского сдвига информации, содержащие п входных шин, п выходных шин, 1og«n управляющих шин для подачи кода сдви га и элементы И, ИЛИ 1 . Недостатком таких устройств являе ся большой объем оборудования. Наиболее близким к предлагаемому по технической сущности является устройство для сдвига информации, со- держащее п входных шин, выходных шин, управляющих шин для по дачи кода сдвига и сдвигатели, распо ложенные последовательно/ соединенным ярусами J :причем выход каждого 3J eMeHтарного сдвигателя соединен с л/И входами сдвигателей следующего яруса ((к число сдвиговых ярусов в устрой стве) t2l. Однако данное устройство обладает меньшим объемом оборудования. Недостатком его является большое число связей между сдвигателями, что особенно резко проявляется при большей разрядности устройства ) Это не позволяет оптимапьш 1м обра-я; зом разрезать сдвиговую сеть и реализовать ее в типовых конструктивных современп 1х ЭВМ (ячейках, блоках. Цель изобретения - упрощение устройства. Для достижения поставленной цели, устройство для сдвига, содержащее вГкоммутаторов (п - количество разрядов операвдов), узел прибавления единицы и узел маски, причем входы {п УП-ВХОДОВЫХ сдвигателей первого яруса соедннепл со входными шинами устройства, J-й выход 1-го сдвигателя (I, ,..., Vn) первого яруса , соединен с f-м входом j-ro сдвигателя второго яруса, управляющие входы сдвигателей первого яруса соединены с управляюи нми шинами младших разрядов кода сдвига устройства и входами узла маски, управляющие входы сдвигателей второго яруса соединены с выходами соответствующих коммутаторов, информационные входы первых групп коммутаторов подключены к управляющим шинам старших разрядов кода сдвига устройства, информационные входы вторых групп коммутаторов соединены с выходами узла прибавления единицы, управляющие йходы коммутаторов соединены с выходами узла маски, j-й выход 1-го сдвигателя второго яруса соединен с ((J-1))-й выходной шиной устройства.На чертеже изображена структурная схема устройства (). Устройство содержит сдвигателй 1 первого яруса, сдвигателй 2 второго яруса, узел 3 маски, узел 4 прибавления единицы, коммутй/рры 5, входные шины 6, управляющие шины 7 кода сдвига, выходные щинь 8, . Выходы сдвигателей 1 соединены со входными шинами 6, Выходы сдвигателей 1 соединены со входами 2 причём j-й выход i-ro сдвигателя 1 соед ненс 1-м входом J-ro сдвигателя 2. Вьрсод .сдвигателей 2 соединень} с вьщрдными шинами 8, причем выход Игр сдвигателя 2 соединен с ,((j-1 )Vnti )-й выходной шиной 8, управляющие входы сдвигателей 1 соединены с управляюш;ими шинами 7 младших разрядов кода сдвига, Входь первых, KOMNfyTaTo ров 5 и входы узла 4 прибавления единицы .соединены с шинами 7 старших разрядов к да сдвига. Входы вторых групп коммута торов 5 соединены с выходами узла 4, Входы узла 3 маски соединень с .щинами 7 младших разрядов кода сдвига, а выходы узла 7 - с управляющими взводами коммутаторов 5. Выходы коммутаторов ,5 соединеныуправляющими входами , сдвигателей 2 второго яруса. Каждый сдвигатель 1, 2 обеспечивает кольцевой сдвиг кода длиной тГп разрядов. Узел маски представляет со бой преобразователь двоичного кода в код с соответствующим количеством единиц в младших разрядах. Устройство работает следуюпщм об разом пусть на входные шины 6 подается 64-разрядный код А-Г +8Р1+8, имею-, щий вид матрицы 8v8, на управляющие 1Ш1НЫ 7-6-разрядный код сдвига определяющий величину кольцевого 14 сдвига. На управляющие входы всех сдвигателей 1 подаются младшие разряды кода сдвига Д-Р4+6. Каждый сдвигатель 1 производит одинаковый кольцевой сдвиг (по строкам), С выходов сдвигателей 1 информация поступает на входы сдвигателей 2 второго яруса, которые производят кольцевой сдвиг (по столбцам), причем величина сдвига определяется в одних столбцах кодом Д-Р}+3, в остальных кодом (д-Р1+3)+1, Узел подготавливает код ()+, узел 3 формирует маску, которая определяет код сдвига в сдвигателях 2, При этом разряды маски, равные О, определяет сдвиг Д-Р1+3, разряды маски, равные J, определяют сдвиг (Д-Р)+3)+, Пример, Пусть исходный код равен А-Г1Р1+8 0001 Jill А-Г2Р 8 000 0001 А-ГЗР1+8 0101 1010 А-Г4Р1+8 ООП . ООП А-Г5Р)+8 1000 0100 А-Г7Р1+8 1100 1111 А-Г7РИ-8 0110 ОНО А-Г2Р1+8 1000 1001 Код управления Д-Р1+6 001 д-р , Д-Р4+6 101 5, На выходе слвигателей 1 т.е, реализован сдвиг на 13. Принципы построения устройства легко обобщаются на случай прямоу гольной матрицы , а также на случай к мерной (к-ярусной струк1уры.

Упрощение устройства связано с улучшением его технологичности и сое тоит в том, что сдвигающая сеть выполнена однородной, состоящей из одинаковых сдвигателей 1, 2, вьтолненных в виде одинаковых блоков или БИС, с ограниченным чиcлo контактов (8 входов, 3 управляющих входа и 8 выходов) ...Количество связей между ярусами невелико - всего 64,

В прототипе для количество связей между ярусами составляет . 2п(1одАП 1)640, т.е. в 10 раз вьше, При этом количество оборудования и быстродействие в данном устройстве оптимальны.

Формула изобретения

Устройство для сдвига, содержащее сдвигатели, отличающееся тем, что, с целью упрощения устройства, оно содержит V коммутаторов (п - количество разрядов операндов), узел прибавления единицы и узел маски, причем входы-Vn л/п входовых сдвигателей первого яруса соединены со входными шинами устройства, j-й вы642816

, ход |то сдвигателя (|«, J 1,,,,,-fn) первого яруса соединен с 1-м вхбдом j-ro сдвигателя второго яруса, управляющие входы сдвигателей пер-. , вого яруса соединены с управ- . ляющими шинами младших разрядов кода.) сдвига устройства и входами узла маеки, управляющие входы сдвигателей вто- рого яруса соединены с выхода о1 соответствующих коммутаторов, информационные входы первьщ групп крммутаторов подключены к управляющим шинам старших разрядов кода сдвига устройства, информационные входы вторых;

5 групп коммутаторов соединены с выхода-. ми узла прибавления единицы, упрсшляющие входы коммутаторов соединены с выходами узла маски, j-й выход j-го сдвигателя второго яруса соединен с

20 (( ) )й выходной щиной устройства.

Источники информации, принятые во внимание при экспертизе 1.Самофалов К,Г. и др, Электрйнйые

2J цифровые вычислительные машины, Киев, Высшая школа р 1976, с. 166, рис.110

t

3

t

«

в

{

5

Авторы

Даты

1981-09-15—Публикация

1979-12-21—Подача