(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1580368A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1730628A1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297116A1 |

| Устройство для сдвига информации | 1986 |

|

SU1363310A1 |

| Устройство для формирования сигналов четности | 1988 |

|

SU1571591A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ | 1992 |

|

RU2045772C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Устройство для формирования сигнала четности при сдвигах двоичных кодов | 1987 |

|

SU1481770A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в высокопроизводительных системах сдвига информации. Цель изобретения - сокращение аппаратурных затрат устройства. Уст ройство содержит дешифратор 1 вида сдвига, формирователи 2, 3 кода маски, блоки 4, 5 элементов И, узел 6 формирования обратного кода, коммутаторы 7, 8, элемент И 9, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10. Сокращение оборудования устройства достигается за счет изменения структуры дерифратора 1, формирователей и изменения связей между этими узлами. 1 з.п.ф-лы, 3 ил., 3 табл.

Ј

СО

сп

Изобретение относится к автоматике и вычислительной технике и монет, быть использовано в высокопроизводительных системах сдвига информации.

Цель изобретения - сокращение аппа ратурных затрат устройства.

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема дешифратора вида сдвига; на фиг. 3 - функциональная схема формирователя кода маски.

Устройство (фиг. 1) содеркит дешифратор 1 вида сдвига, формирователи 2 и 3 кода маски, блоки 4 и 5 элементов И, узел 6 формирования обратного кода, коммутаторы 7 и 8, элемент И 9, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, входы 11 и 12 типа и направления сдвига устройства соответственно, вход 13 кода направления сдвига (13 - группа старших разрядов, 13 - группа младших разрядов, 13j - младший разряд), информационный вход 14 устройства, вход 15 контрольных разрядов устройства и выход 16 контрольного разряда устройства.

Дешифратор 1 вида сдвига (фиг.2) включает выходы 17-19 дешифратора, элемент НЕ 20 и элементы И 21-23.

Формирователь 3 кода маски (фиг. 3 образуют элементы И 24-37 и элементы ИЛИ 38-45.

Рассмотрим функциональное назначение и реализацию основных блоков и узлов устройства для предсказания .четности результата сдвиг ателя. Предположим, что на вход сдвигателя и, следовательно, на информационный вход устройства для предсказания четности результата сдвигателя поступает входная информация разрядностью 64 бита, причем каждый байт входной информации сопровождается своим контрольным разрядом четности.

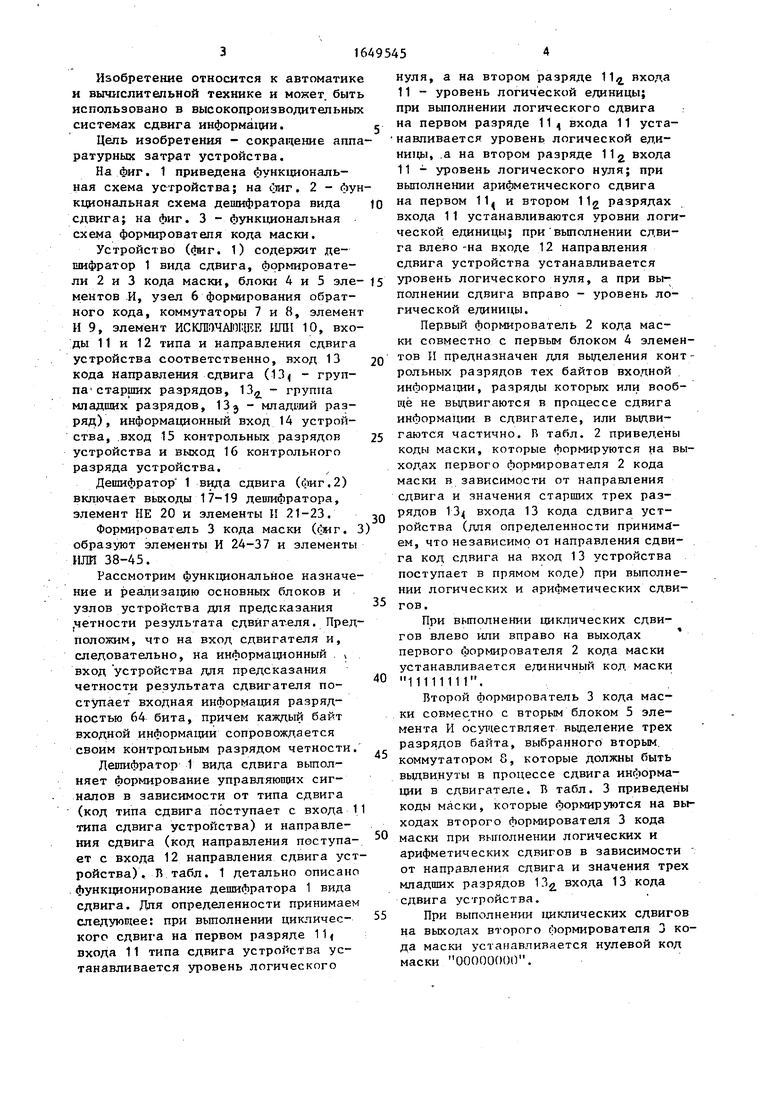

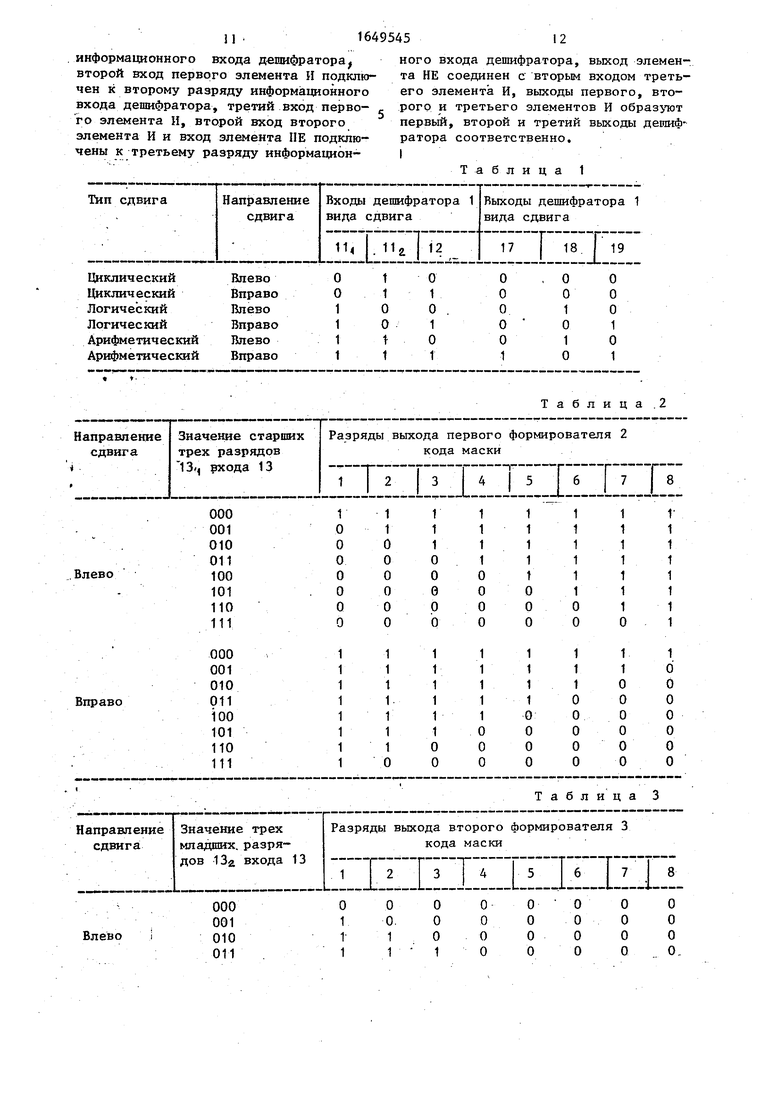

Дешифратор 1 вида сдвига выполняет формирование управляющих сигналов в зависимости от типа сдвига (код типа сдвига поступает с входа 11 типа сдвига устройства) и направления сдвига (код направления поступает с входа 12 направления сдвига устройства). В табл. 1 детально описано функционирование дешифратора 1 вида сдвига. Для определенности принимаем следующее: при выполнении циклического сдвига на первом разряде 11« входа 11 типа сдвига устройства устанавливается уровень логического

0

нуля, а на втором разряде 114 входа 11 - уровень логической единицы; при выполнении логического сдвига

на первом разряде 11 ) входа 11 уста- навливается уровень логической единицы, а на втором разряде 112 входа 11 - уровень логического нуля; при выполнении арифметического сдвига

0 на первом 11 и втором 11g разрядах входа 11 устанавливаются уровни логической единицы; при выполнении сдвига влево -на входе 12 направления сдвига устройства устанавливается

5 уровень логического нуля, а при выполнении сдвига вправо - уровень логической единицы.

Первый формирователь 2 кода маски совместно с первым блоком 4 элементов И предназначен для выделения контрольных разрядов тех байтов входной информации, разряды которых или вообще не выдвигаются в процессе сдвига информации в сдвигателе, или выдви5 гаются частично. Р табл. 2 приведены коды маски, которые формируются на выходах первого формирователя 2 кода маски в зависимости от направления сдвига и значения старших трех разрядов 134 входа 13 кода сдвига устройства (для определенности принимаем, что независимо от направления сдвига код сдвига на вход 13 устройства поступает в прямом коде) при выполнении логических и арифметических сдвигов.

При выполнении циклических сдвигов влево или вправо на выходах первого формирователя 2 кода маски устанавливается единичный код маски

0 11111111.

Второй формирователь 3 кода маски совместно с вторым блоком 5 элемента И осуществляет выделение трех разрядов байта, выбранного вторым коммутатором 8, которые должны быть выдвинуты в процессе сдвига информации в сдвигателе. В табл. 3 приведены коды маски, которые формируются на выходах второго формирователя 3 кода

0 маски при выполнении логических и

арифметических сдвигов в зависимости - от направления сдвига и значения трех младших разрядов 13 входа 13 кода сдвига устройства.

5 При выполнении циклических сдвигов на выходах второго формирователя 3 кода маски устанавливается нулевой код маски 00000000.

0

5

5

516

Формирователи 2 и 3 кода маски мож ,но выполнить, например, на ППЗУ 500РЕ149 (управляющие и информационные входы формирователей 2 и 3 в этом случае являются адресными входами ППЗУ), на восьмивходовых мультиплексорах 500ИД164, на элементах И, ИЛИ, НЕ.

На фиг. 3 приведена функциональная схема формирователя 3 кода маски, реализованного на элементах И и ИЛИ, при этом разряды выхода второго формирователя 3 кода маски определяются следующими выражениями:

где х и у - значения сигналов на выходах 18 и 19 дешифратора 1 вида сдвига соответственно;

а,, а аз

г

соответствующих входа 13 кода

- значения разрядов сдвига.

Первый формирователь 2 кода маски может быть выполнен аналогично, только элементы ОДШ 38-45 должны быть заменены на элементы ШШ-ИЕ.

Узел б формирования обратного кода и первый коммутатор 7 предназначен для формирования номера того байта входной информации, разряды которого могут быть частично выдвинуты в процессе сдвига информации в сдвигателе (нумерация байтов идет от 000 для самого левого байта до

вдвигаемых единиц при выполнении в сдвигателе арифметического сдвига впра во. Этот сигнал равен единице только в том случае, когда выполняется в сдвигателе арифметический сдвиг впра во (в этом случае устанавливается уровень логической единицы на выходе 17 дешифратора 1 вида сдвига) на нечетное число разрядов (значение младшего разряда 13j входа 13 кода

30 сдвига равно единице) отрицательного числа (значение старшего разряда 14{ входа 14 данных устройства равно еди нице) .

На элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 10

-.- формируется предсказываемая четность результата сдвигателя, для чего выполняется суммирование по модулю два следующих трех групп слагаемых; конт рольных разрядов тех байтов входной

4Q информации, разряды которых вообще не выдвигаются в процессе сдвига информации в сдвигателе или выдвигаютс частично (эти контрольные разряды поступают на вход элемента 10 с выходо

111 для самого правого байта). В уз- 45 первого блока 4 элементов И); выдвиле 6 формирования обратного кода формируется обратный код от значения трех старших-разрядов 13 входа 13 кода сдвига устройства. Первый коммутатор 7 пропускает на выход значения трех старших разрядов 13 входа 13 кода сдвига устройства, если в сдви- сателе осуществляется сдвиг информации влево. В противном случае (при сдвиге вправо) на его выход подается обратный код значения трех старших разрядов 131 входа 13, полученный в узле 6 формирования обратного кода.

гаемых разрядов того байта входной информации, разряды которого только частично теряются в процессе сдвига информации в сдвигателе (эти разряды 50 поступают на вход элемента 10 с вы- ходов второго блока 5 элементов И); сигнала, учитывающего четность вдвигаемых единиц при арифметическом сдвиге вправо отрицатепьного числа (значение этого сигнала подается на вход элемента 10 с выхода элемента И 9).

В результате этого на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 10 формируется пред55

Пторой коммутатор 8 осуществляет выборку с входа 14 данных устройства того байта входной информации, разряды которого могут быть частично выдвинуты в процессе сдвига информации в сдвигателе, т.е. граничного байта. Коммутатор 8 может быть реализован на восьмивходовых мультиплексорах 500 ИД 164, на адресные входы которых поступает значение номера байта с выходов первого коммутатора 7 а на информационные входы - соответствующие разряды байтов входной ин- 5 формации информационного входа 14 устройства.

Элемент И 9 предназначен для форми

вдвигаемых единиц при выполнении в сдвигателе арифметического сдвига вправо. Этот сигнал равен единице только в том случае, когда выполняется в сдвигателе арифметический сдвиг вправо (в этом случае устанавливается уровень логической единицы на выходе 17 дешифратора 1 вида сдвига) на нечетное число разрядов (значение младшего разряда 13j входа 13 кода

сдвига равно единице) отрицательного числа (значение старшего разряда 14{ входа 14 данных устройства равно единице) .

На элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 10

формируется предсказываемая четность результата сдвигателя, для чего выполняется суммирование по модулю два следующих трех групп слагаемых; контрольных разрядов тех байтов входной

информации, разряды которых вообще не выдвигаются в процессе сдвига информации в сдвигателе или выдвигаются частично (эти контрольные разряды поступают на вход элемента 10 с выходов

первого блока 4 элементов И); выдвигаемых разрядов того байта входной информации, разряды которого только частично теряются в процессе сдвига информации в сдвигателе (эти разряды 0 поступают на вход элемента 10 с вы- ходов второго блока 5 элементов И); сигнала, учитывающего четность вдвигаемых единиц при арифметическом сдвиге вправо отрицатепьного числа (значение этого сигнала подается на вход элемента 10 с выхода элемента И 9).

В результате этого на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 10 формируется пред5

сказанная четность результата сдви- гателя.

Работа устройства рассматривается в различных режимах на примере слвига в нем восьми байтов входной информации а0а(3Ј1.,а$зна 53 двоичных разряда (на вход 13 устройства подается прямой двоичный код величины сдвига 100101).

Устройство работает следующим образом.

Пусть самый левый байт ава,аа,.,. ... ау входной, информации является самым старшим (нулевым) байтом и сопровождается контрольным разрядом К0, а самый правый байт а. „.. а6Ъ является самым младшим (седьмым) байтом и сопровождается контрольным разрядом К7.

Сдвиг вправо логический.

На первый 11 и второй 11д разряды вход а 11 типа сдвига устройства поступает код сдвига логического 10, а на вход 12 направления сдвига устройства поступает уровень логической единицы, соответствующий сдвигу вправо. В .соответствии с функционированием дешифратора 1 вида сдвига (табл. 1) на его выходах 17-19 формируется код 001. На информационные входы первого формирователя 2 кода каски поступает значение прямого кода трех старших разрядов 13f кода сдвига (для данного примера 110), а на информационные входы второго фор мирователя 3 поступает значение прямого кода трех младших разрядов 13g кода сдвига (для данного примера 101.).

На выходах первого формирователя

2кода маски образуется код 11000000 а на выходах второго формирователя

3- код маски 00011111 (табл. 3). Так как в устройстве осуществляется сдвиг вправо, то на выходы первого коммутатора 7 подается значение обратного кода трех старших разрядов сдвига 110, т.е. код 001. В соответствии с этим с помощью второго коммутатора 8 с информационного входа 14 устройства выбирается первый байт ag ... a ffвходной информации.

По сформированным в устройстве маскирующим кодам на выходах первого блока 4 элементов И получается зна- ченне К0К,000000, а на выходах второго блока 5 элементов И - значение 000 а ((а4га,за14af Эти значения,

5

Я14®

суммируясь на элементе 10 ИСКЛЮЧАЮЩЕЕ

ИЛИ по модулю два, образуют значение

предсказанной четности результата

сдвигателя

Р,б К0@ К, © а„© а,г©а„

Сдвиг вправо арифметический, В этом режиме устройство работает аналогично предыдущему. Отличие состоит только в том, что-на выходе 17 дешифратора 1 вида сднига формируется потенциал логической единицы. Для тех же данных в этом случае формируется следующее значение предсказания четности

,©ам

12v

а,3©г

,4t

4S

©П,

20

25

30

35

40

45

50

55

где П - признак, учитывающий четность вдвигаемых единиц при сдвиге отрицательного числа (значение признака П формируется на выходе элемента И 9).

П 1 только тогда, когда выполняется арифметический сдвиг вправо отрицательного числа на нечетное количество разрядов.

Сдвиг влево логический.

На первый 11 и второй 11 разряды входа 11 типа сдвига устройства поступает код сдвига логического 10, а на вход 12 направления сдвига устройства поступает уровень логического нуля, соответствующий-сдвигу влево . В соответствии с функционированием дешифратора 1 вида сдвига (табл.1) на его выходах 17-19 формируется код 010.

На информационные входы первого формирователя 2 кода маски поступает значение прямого кода трех старших разрядов 13( кода сдвига (для данного примера 110), а на информационные входы второго формирователя 3 поступает значение прямого кода трех младших разрядов 1Зл. кода сдвига (для данного примера 101). Па выходах первого формирователя 2 образуется код маски 00000011, а на выходах второго формирователя 3 - код маски 11111000 (табл., 1)« Так как в устройстве осуществляется сдвиг влево, то на выходы первого коммутатора 7 поступает значение прямого кода трех старших разрядов 13 кода сдвига 110, в соответствии с чем на втором коммутаторе 8 с информационного входа 14 устройства выбирается шестой байт ... а увходной информации. По сформированным в устройстве маскирующим кодам на выходах первого блока 4 элем- ментов И получается значение ООООООК6К7, а на выходах второго бло-ка 5 элементов И - значение а,,в а .000. Эти значения, суммируясь по модулю два на элементе 10, образуют значение предсказанной четности результата сдвигателя

К

t © а

1 я

v

Сдвиг влево арифметический.

В этом режиме устройство работает так же, как и в предыдущем режиме,. и для тех же данных формируется то же значение предсказанной четности.

Сдвиг циклический.

На первый 11j и второй 11 разряды входа 11 типа сдвига устройства поступает код сдвига циклического 01, при котором независимо от уровня логического сигнала на входе 12 направления сдвига устройства на выходах 17-19 дешифратора 1 формируется код 000 (табл. 1).

В этом случае при любых значениях, поступающих на информационные входы первого 2 и второго 3 формирователей, на их выходах формируются коды 11111111 и 00000000 соответственно. По сформированным в устройстве маскирующим кодам на выходах первого блока элементов И получается значение К0К1Кг1ЦК4К5-К6К7, а на выходах второго блока 5 элементов И - значение 00000000, которые, суммируясь по модулю два на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ.10, образуют значение предсказанной четности результата сдвигателя

40

поступающее на выход 16 устройства.

В предлагаемом устройстве организован автономный (независимый) контроль по четности, не требующий введения дополнительных связей со сдвигате-45 лем и не ограничивающий варианты его реализации.

Формула изо-бретения

5

0

5

0

5

0

5

0

5

к соответствующим разрядам информационного, входа дешифратора вида едйй- га, информационные входы первого и второго формирователей кода маски подключены соответственно к группам старших и младших разрядов входа задания кода сдвига устройства, выходы первого и второго формирователей кода маски соединены с первыми входами соответственно первого и второго блоков элементов И, выходы которых соединены с соответствующими входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом контрольного разряда устройства, вход узла формирования обратного кода и первый информационный вход первого коммутатора подключен к группе старших разрядов входа задания кода сдвига устройства, выход узла формирования обратного кода соединен с вторым информационным входом первого коммутатора, выход которого соединен с управляющим входом второго коммутатора, информационный вход которого подключен к информационному входу устройства, второй вход первого блока элементов И подключен к входу контрольных разрядов устройства, выход второго коммутатора соединен с вторым входом второго блока элементов И, выход.элемента И соединен с соответствующим входом элемента ИС- КЛЮЧА101ЦЕЕ ИЛИ, первый выход дешифратора вида сдвига соединен с первым входом элемента И, второй и третий входы которого подключены соответственно к младшему разряду входа задания кода сдвига и старшему разряду информационного входа устройства, управляющий вход первого коммутатора подключен к входу задания направления сдвига устройства, второй и третий вькоды дешифратора вида сдвига соеди- йены с первым и вторым управляющими входами первого формирователя кода маски соответственно, о т л и ч а ю-- щ е е с я тем, что, с целью сокращения аппаратурных затрат устройства, второй и третий выходы дешифратора вида сдвига соединены соответственно с первым и вторым управляющими входами второго формирователя кода маски.

информационного

входа дешифратора, второй вход первого элемента И подключен к второму разряду информационного входа дешифратора, третий вход перво- , го элемента И, второй вход второго элемента И и вход элемента НЕ подключены к третьему разряду информационного входа дешифратора, выход элемента НЕ соединен с вторым входом третьего элемента И, выходы первого, второго и третьего элементов И образуют первый, второй и третий выходы дешифратора соответственно. I

Таблица 1

Фиг 2:

Составитель В. Гречнев Редактор А. Огар Техред Л.Олийнык Корректор А. Обручар

Заказ 1522

Тираж 419

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

| Авторское свидетельство СССР № 1300477, кл | |||

| С, 06 F 11/10, 1905 | |||

| Авторское свидетельство СССР № 1546985, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-05-15—Публикация

1988-12-21—Подача