Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных и импульсных сигналов, в структуре операционных усилителей, усилителей мощности и аналоговых интерфейсов различного функционального назначения.

В современных аналоговых микросхемах находят применение два типа входных каскадов - классический дифференциальный усилитель [1-3] и мостовой дифференциальный каскад (МДК) на основе двухтактных эмиттерных повторителей [4-15].

Мостовой дифференциальный каскад (МДК) стал основой построения практически всех быстродействующих операционных усилителей (ОУ) ведущих микроэлектронных фирм (Texas Instruments: патенты США №6710655, 6710654, 6492870, 6542032, 6249187, Analog Devices: патенты США №5150074, 6262633, Maxim: патенты США №6188281, 6429744, National Semiconductor: патенты США №5512859, 5399991, 5510754) [4-15].

Однако известные МДК имеют недостаточно высокое предельное быстродействие из-за нелинейных режимов работы его входных двухтактных эмиттерных повторителей при большом импульсном сигнале. Это не позволяет (из-за эффектов второго порядка) получить предельные (теоретические) значения максимальной скорости нарастания выходного напряжения (ϑвых. max), которая оказывается в 4-10 раз выше экспериментальных значений (ϑвых<<ϑвых. max). Проблема достижения предельно возможного быстродействия МДК и ОУ на их основе является одной из актуальных проблем современной аналоговой микросхемотехники.

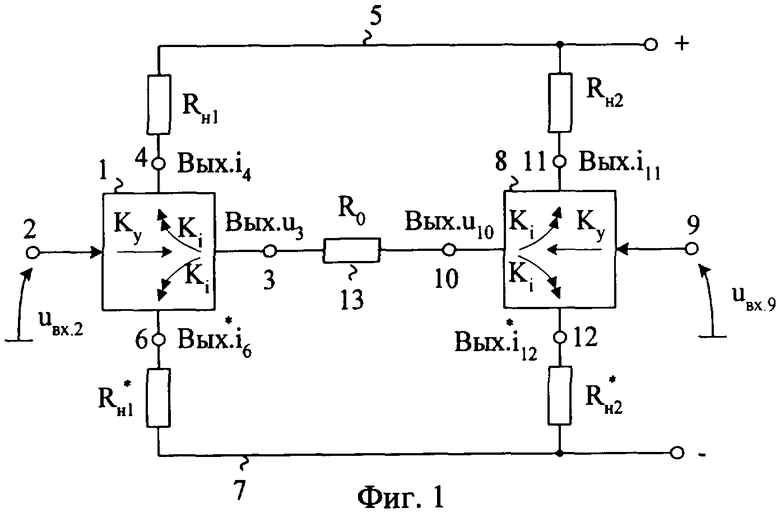

Ближайшим прототипом заявляемого устройства является входной каскад операционного усилителя (фиг.1) (патент фирмы Maxim - РСТ №WO 00/19604 от 6.04.2000 г., фиг.2), содержащий первый 1 двухтактный эмиттерный повторитель, который имеет потенциальный вход 2 и потенциальный выход 3, а также токовый выход 4, согласованный с шиной положительного источника питания 5, и токовый выход 6, согласованный с шиной отрицательного источника питания 7, второй двухтактный эмиттерный повторитель 8, который имеет потенциальный вход 9 и потенциальный выход 10, а также токовый выход 11, согласованный с шиной положительного источника питания 5, и токовый выход 12, согласованный с шиной отрицательного источника питания 7, причем между потенциальным выходом 3 первого 1 двухтактного эмиттерного повторителя и потенциальным выходом 10 второго 8 двухтактного эмиттерного повторителя включен двухполюсник 13.

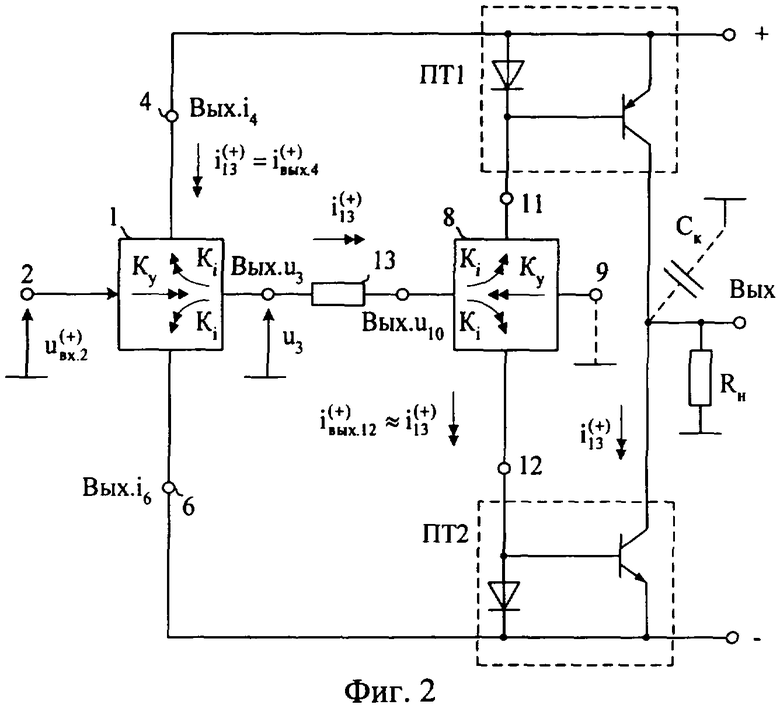

На фиг.2 показана схема входного каскада-прототипа при его включении в структуру операционного усилителя, содержащего повторители тока ПТ1, ПТ2.

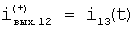

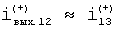

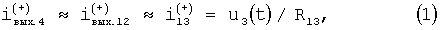

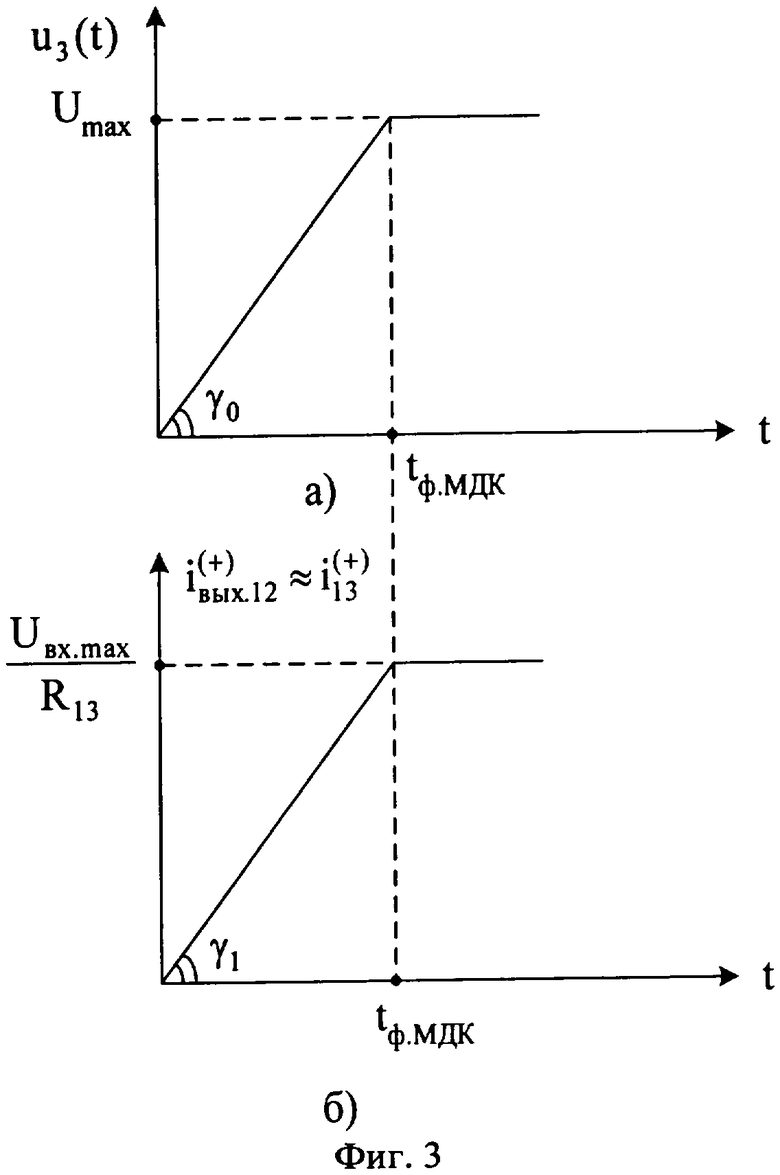

На фиг.3 приведены графики временной зависимости выходного напряжения u3(t) и выходного тока  известного устройства фиг.1 - фиг.2.

известного устройства фиг.1 - фиг.2.

Существенный недостаток известного устройства состоит в том, что его архитектура не позволяет полностью исключить динамическую перегрузку его входных двухтактных эмиттерных повторителей и тем самым получить предельные значения максимальной скорости нарастания выходного напряжения для большого сигнала, т.е. обеспечить ϑвых≈ϑвых.max.

Рассмотрим работу дифференциального входного каскада-прототипа. Если на вход 2 (фиг.2) подать прямоугольный импульс большой амплитуды  , то напряжение u3(t) на потенциальном выходе Вых.u3 начнет изменяться от статического (нулевого) значения до уровня Umax (фиг.3а). Так как коэффициент передачи двухтактного эмиттерного повторителя 1 близок к единице, то Umax=Uвх.max, где Uвх.max - амплитуда входного импульсного сигнала uвх.2.

, то напряжение u3(t) на потенциальном выходе Вых.u3 начнет изменяться от статического (нулевого) значения до уровня Umax (фиг.3а). Так как коэффициент передачи двухтактного эмиттерного повторителя 1 близок к единице, то Umax=Uвх.max, где Uвх.max - амплитуда входного импульсного сигнала uвх.2.

Двухтактный эмиттерный повторитель 1, имеющий в своей структуре транзисторы, транзисторные источники опорного тока, паразитные емкости на подложку и т.д., всегда характеризуется достаточно большой инерционностью, которая приводит к тому, что напряжение u3(t) на его потенциальном выходе 3 имеет форму «пилы» (фиг.3а), т.е. конечную скорость нарастания. Как показывает анализ типовых структур двухтактных эмиттерных повторителей, угол γ0 наклона кривой u3=f(t) к оси времени tgγ0≠90°, а время фронта tф.МДК лежит для современных биполярных технологий (НПО «Интеграл», ФГУП КПП «Пульсар») в пределах 10÷20 нс. Поэтому закон изменения импульсов тока через двухполюсник 13 и импульсов выходных токов  повторяет закон изменения u3(t):

повторяет закон изменения u3(t):

где R13 - сопротивление двухполюсника 13.

Сравнительно большие значения фронта  tф.МДК (фиг.3) не позволяют создавать на базе известных мостовых ДК быстродействующие ОУ с предельно высокими значениями максимальной скорости нарастания выходного напряжения ϑВЫХ, которая определяется передним фронтом тока

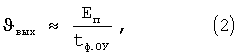

tф.МДК (фиг.3) не позволяют создавать на базе известных мостовых ДК быстродействующие ОУ с предельно высокими значениями максимальной скорости нарастания выходного напряжения ϑВЫХ, которая определяется передним фронтом тока  . Это объясняется тем, что быстродействие МДК должно быть значительно больше, чем быстродействие ОУ с МДК в целом, так как МДК «включается» в работу и форсирует процессы перезаряда самого инерционного элемента схемы (корректирующей емкости ОУ Ск) только во время фронта выходного напряжения ОУ tф.ОУ, которое связано с максимальной скоростью нарастания выходного напряжения (ϑвых) следующей приближенной формулой:

. Это объясняется тем, что быстродействие МДК должно быть значительно больше, чем быстродействие ОУ с МДК в целом, так как МДК «включается» в работу и форсирует процессы перезаряда самого инерционного элемента схемы (корректирующей емкости ОУ Ск) только во время фронта выходного напряжения ОУ tф.ОУ, которое связано с максимальной скоростью нарастания выходного напряжения (ϑвых) следующей приближенной формулой:

где Еп - напряжение питания ОУ, tф.ОУ - время фронта выходного напряжения ОУ при 100% обратной связи. В быстродействующих ОУ должно быть

Если проектируемый ОУ имеет ϑдых=5000 В/мкс и Еп=15 В, то должно быть tф.ОУ≈3,0 нс.

С учетом формул (1)-(3) можно найти, что при заданной величине ϑвых в схеме фиг.2 должно выполняться неравенство

Из формулы (4) следует, что при рассматриваемых параметрах элементов МДК-прототип не эффективен, если на его основе необходимо спроектировать ОУ, имеющий максимальную скорость нарастания выходного напряжения более 1000 В/мкс. Указанное обстоятельство становится еще более доминирующим при работе транзисторов двухтактных эмиттерных повторителей в микрорежиме, когда tф.МДК еще более возрастает.

Таким образом, невысокое предельное быстродействие известного устройства в режиме больших сигналов ограничивает быстродействие различных аналоговых устройств, в т.ч. операционных усилителей на его основе, НЧ-усилителей мощности с обратной связью и т.п.

Основная цель предлагаемого изобретения состоит в повышении быстродействия входного каскада. Это позволит получить максимальную скорость нарастания выходного напряжения в ОУ на его основе (ϑвых) в диапазоне нескольких тысяч вольт на микросекунду при использовании отечественных микронных технологий (5000÷10000 В/мкс).

Поставленная цель достигается тем, что в известном дифференциальном усилителе-прототипе, содержащем первый 1 двухтактный эмиттерный повторитель, который имеет потенциальный вход 2 и потенциальный выход 3, а также токовый выход 4, согласованный с шиной положительного источника питания 5, и токовый выход 6, согласованный с шиной отрицательного источника питания 7, второй двухтактный эмиттерный повторитель 8, который имеет потенциальный вход 9 и потенциальный выход 10, а также токовый выход 11, согласованный с шиной положительного источника питания 5, и токовый выход 12, согласованный с шиной отрицательного источника питания 7, причем между потенциальным выходом 3 первого 1 двухтактного эмиттерного повторителя и потенциальным выходом 10 второго 8 двухтактного эмиттерного повторителя включен двухполюсник 13, предусмотрены новые элементы и связи - вход 2 первого двухтактного эмиттерного повторителя 1 соединен с потенциальным выходом 10 второго 8 двухтактного эмиттерного повторителя через первую группу встречно-параллельно включенных р-n переходов 14.

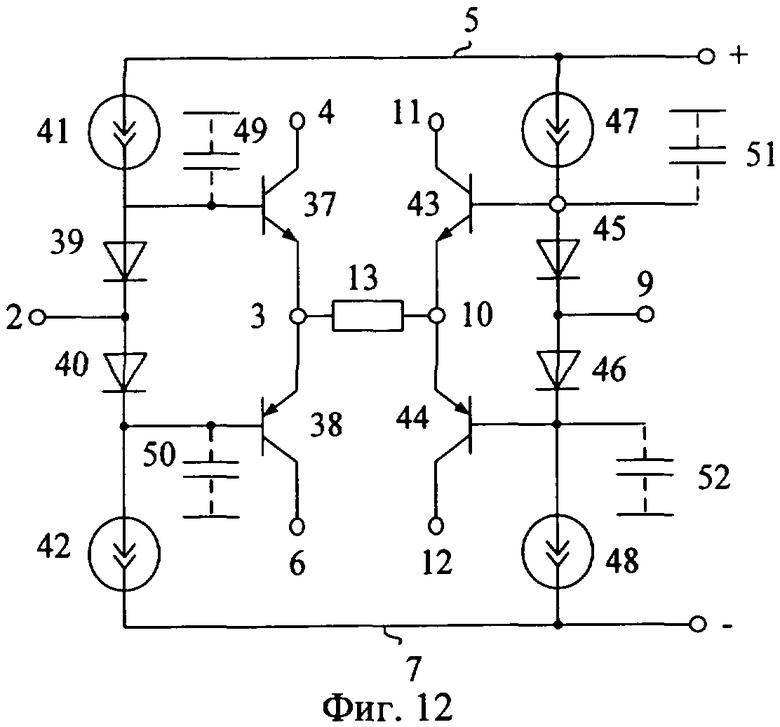

Схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения показана на фиг.4.

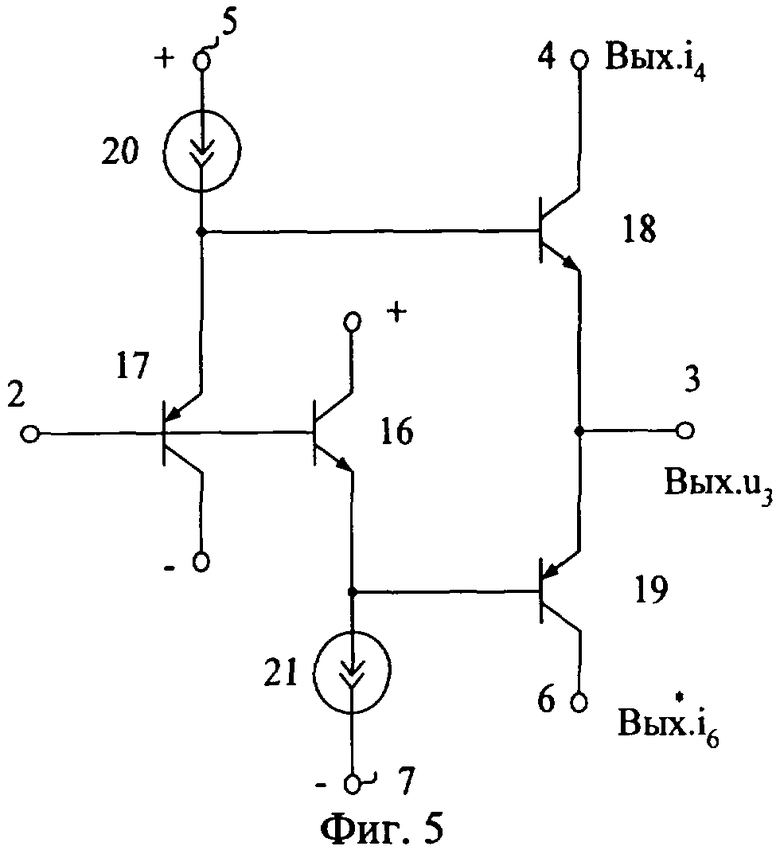

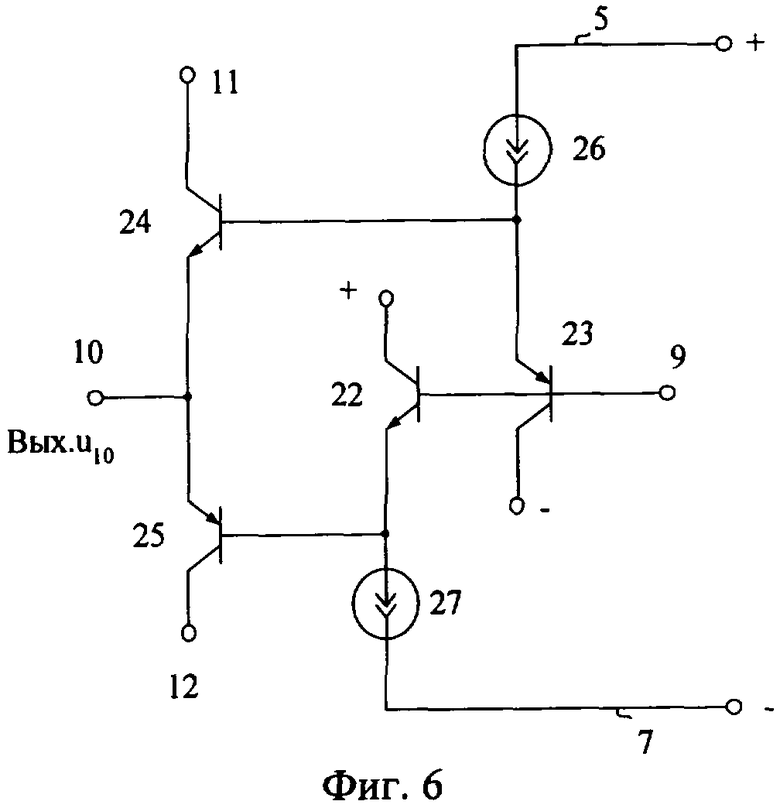

На фиг.5 и фиг.6 представлены частные случаи построения первого 1 и второго 8 двухтактных эмиттерных повторителей.

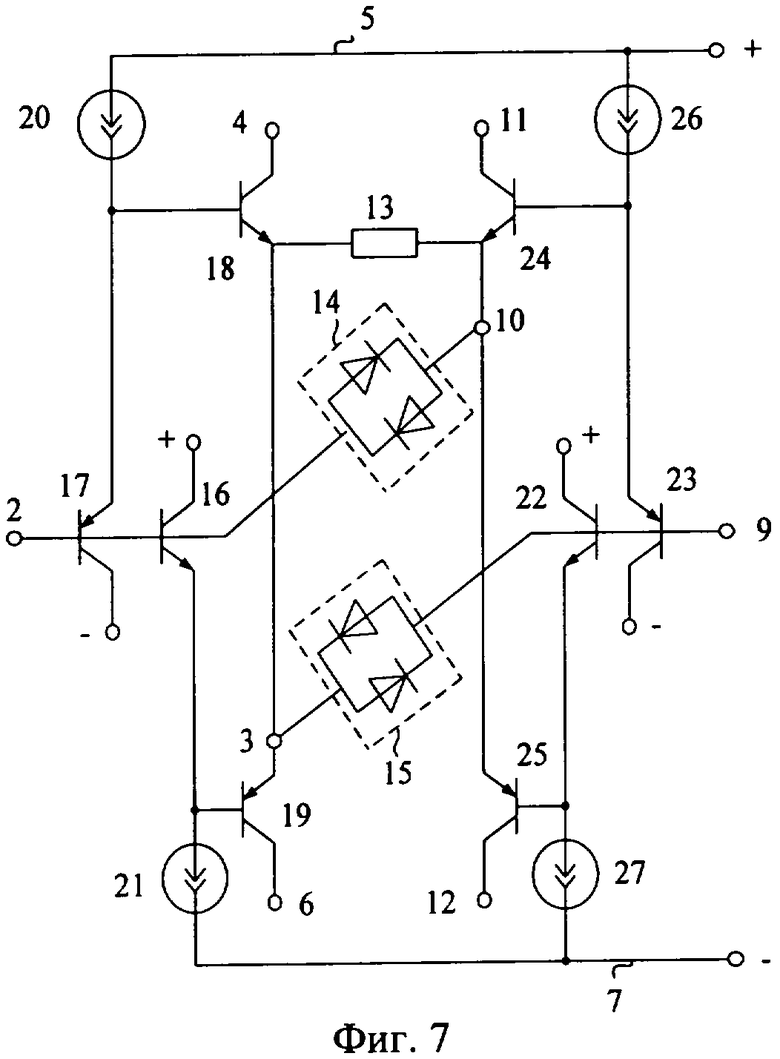

Показанная на фиг.7 схема заявляемого устройства иллюстрирует описанные в п.1 и п.2, п.3 и п.4 формулы изобретения варианты выполнения двухтактных эмиттерных повторителей (п.1, п.2), а также структуру первой 14 и второй 15 групп встречно-параллельного включения р-n переходов.

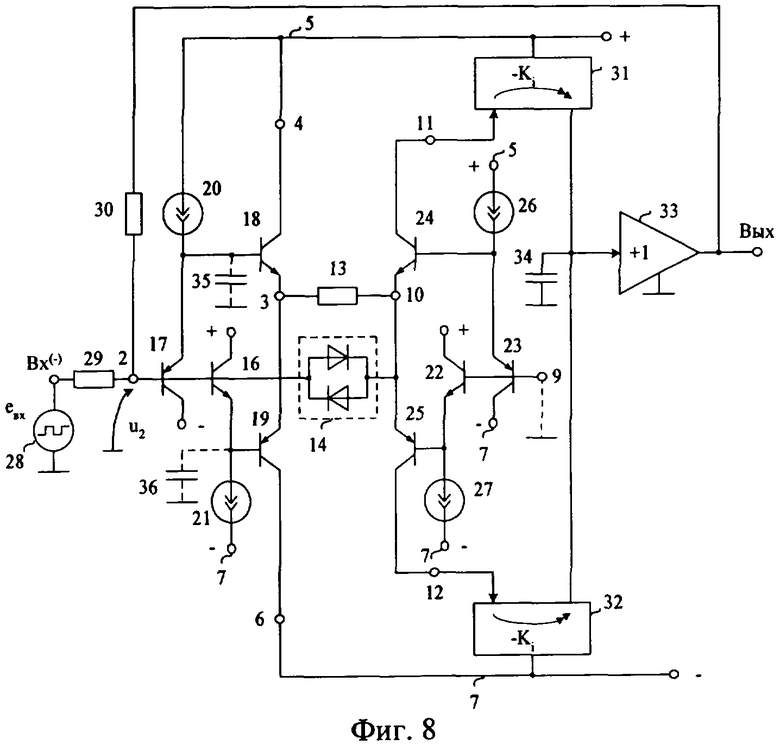

Схема быстродействующего операционного усилителя на базе заявляемого входного каскада показана на фиг.8.

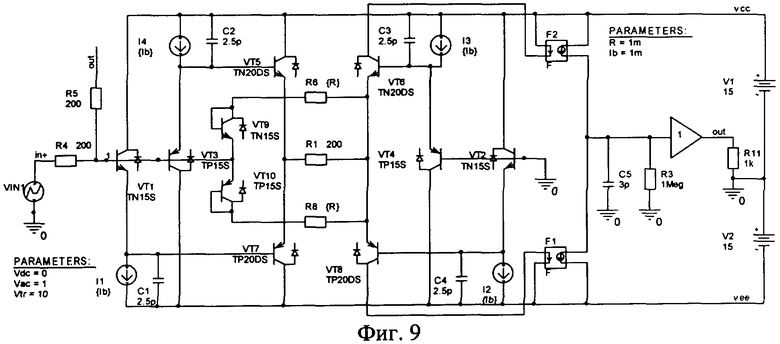

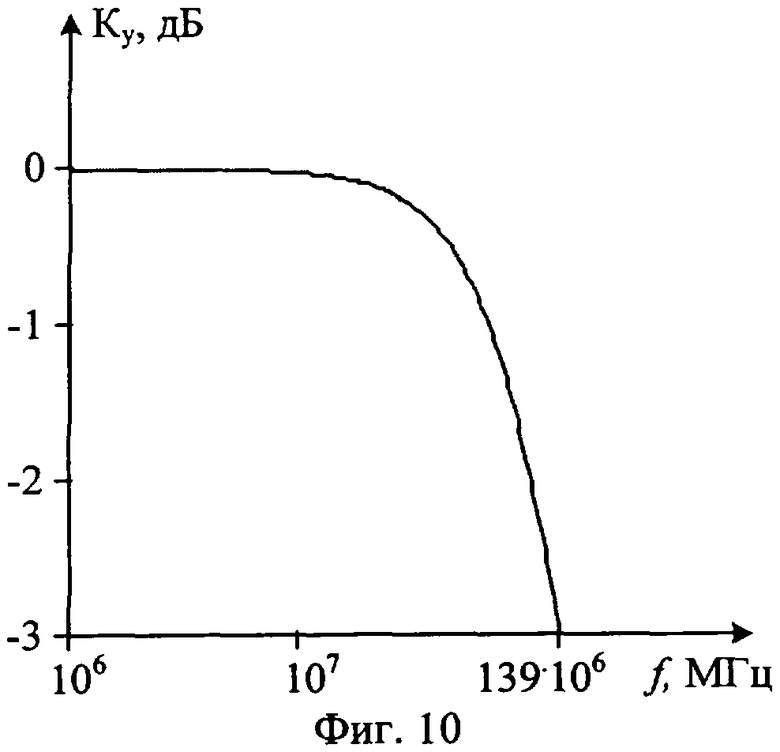

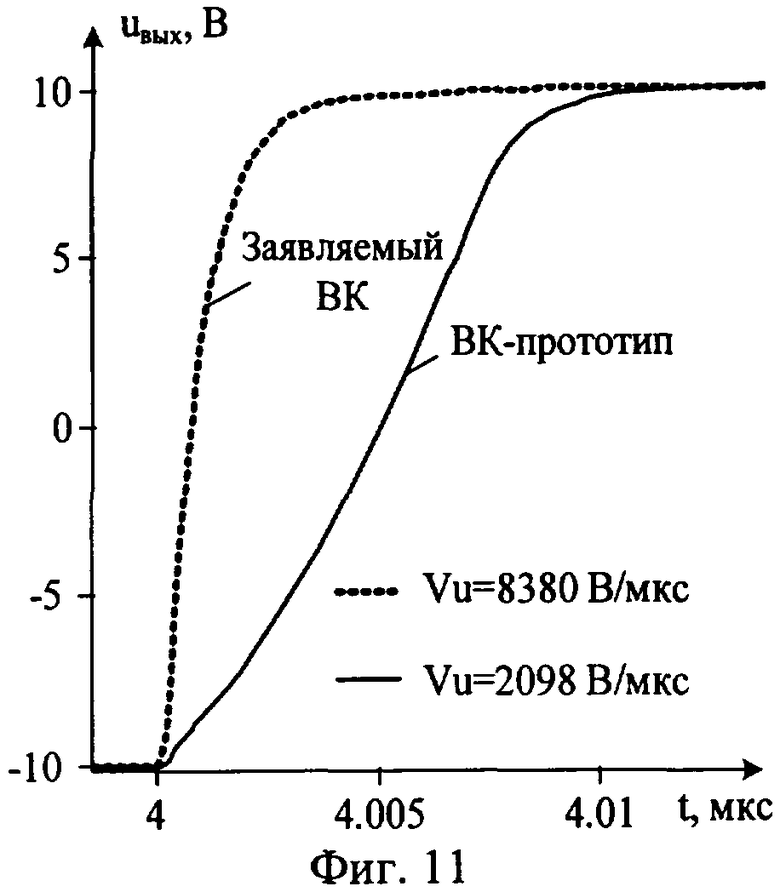

На фиг.9 представлена схема ОУ фиг.8 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.10-11 - результаты расчета ее АЧХ (фиг.10) и переходных процессов (фиг.11).

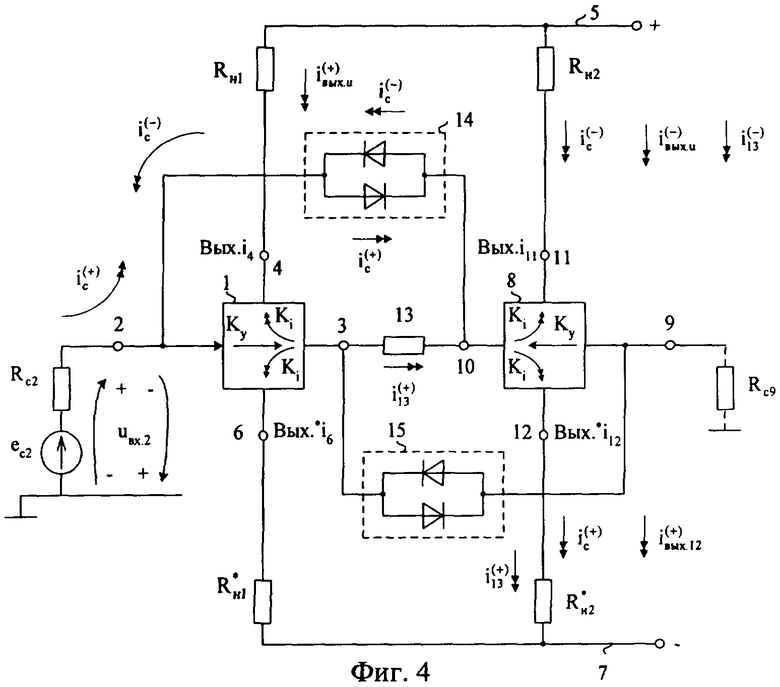

На фиг.12 показан в качестве примера дополнительный вариант построения двухтактных эмиттерных повторителей 1 и 8.

Входной каскад быстродействующего ОУ (фиг.4) содержит первый 1 двухтактный эмиттерный повторитель, который имеет потенциальный вход 2 и потенциальный выход 3, а также токовый выход 4, согласованный с шиной положительного источника питания 5, и токовый выход 6, согласованный с шиной отрицательного источника питания 7, второй двухтактный эмиттерный повторитель 8, который имеет потенциальный вход 9 и потенциальный выход 10, а также токовый выход 11, согласованный с шиной положительного источника питания 5, и токовый выход 12, согласованный с шиной отрицательного источника питания 7, причем между потенциальным выходом 3 первого 1 двухтактного эмиттерного повторителя и потенциальным выходом 10 второго 8 двухтактного эмиттерного повторителя включен двухполюсник 13. Вход 2 первого двухтактного эмиттерного повторителя 1 соединен с потенциальным выходом 10 второго 8 двухтактного эмиттерного повторителя через первую группу встречно-параллельно включенных р-n переходов 14.

Частный вариант выполнения первого 1 двухтактного эмиттерного повторителя (п.3 формулы изобретения), показанный на чертеже фиг.5, содержит первый 16 n-p-n и второй 17 р-n-р входные транзисторы, объединенные базы которых являются потенциальным входом 2 двухтактного эмиттерного повторителя 1, первый 18 n-p-n и второй 19 р-n-р выходные транзисторы, эмиттеры которых являются потенциальным выходом 3 двухтактного эмиттерного повторителя 1, причем коллекторы первого 18 n-p-n и второго 19 р-n-р выходных транзисторов являются токовыми выходами 4 и 6, согласованными соответственно с шиной 5 положительного и шиной 7 отрицательного источников питания, причем между шиной положительного источника питания 5 и базой первого выходного n-p-n транзистора 18, соединенной с эмиттером второго 17 входного р-n-р транзистора, включен первый токостабилизирующий двухполюсник 20, а между шиной отрицательного источника питания 7 и базой второго 19 выходного р-n-р транзистора, соединенной с эмиттером первого 16 входного n-p-n транзистора, включен второй токостабилизирующий двухполюсник 21.

Частный вариант выполнения второго 2 двухтактного эмиттерного повторителя (п.4 формулы изобретения), показанный на фиг.6, содержит первый 22 n-p-n и второй 23 р-n-р входные транзисторы, объединенные базы которых являются потенциальным входом 9 второго двухтактного эмиттерного повторителя 8, первый 24 n-p-n и второй 25 р-n-р выходные транзисторы, эмиттеры которых являются потенциальным выходом 10 второго 8 двухтактного эмиттерного повторителя, причем коллекторы первого 24 n-p-n и второго 25 р-n-р выходных транзисторов являются токовыми выходами 11 и 12, согласованными соответственно с шиной 5 положительного и шиной 7 отрицательного источников питания, причем между шиной 5 положительного источника питания и базой первого 24 выходного n-p-n транзистора, соединенной с эмиттером второго 23 входного р-n-р транзистора, включен первый 26 токостабилизирующий двухполюсник, а между шиной 7 отрицательного источника питания и базой второго 25 выходного р-n-р транзистора, соединенной с эмиттером первого 22 входного n-р-n транзистора 22, включен второй 27 токостабилизирующий двухполюсник.

Схема фиг.7, объединяющая фиг.4, 5, 6, иллюстрирует частный пример построения заявляемого устройства.

Операционный усилитель фиг.8 содержит все элементы заявляемого входного каскада фиг.7. Кроме этого, эта схема включает источник импульсного сигнала большой амплитуды 28, резисторы обратной связи 29 и 30. Токовые выходы 11 и 12 подключены к «токовым зеркалам» 31 и 32, выходы которых соединены со входом выходного буферного усилителя 33 и корректирующим конденсатором 34. Показанные в цепи баз транзисторов 18 и 19 паразитные емкости 35 и 36 (Сп=2÷3 пФ) моделируют инерционность основного канала усиления в ОУ фиг.6.

Схема операционного усилителя в среде PSpice на моделях интегральных транзисторах ФГУП ПНН «Пульсар», соответствующая ОУ фиг.8, содержит заявляемый входной каскад фиг.4, идеальные повторители тока F2 (ПТ1) и F1 (ПТ2), а также емкость коррекции Ск=3 пФ и идеальный буферный усилитель БУ.

Амплитудно-частотная характеристика замкнутого скорректированного ОУ фиг.9 показывает, что он имеет верхнюю граничную частоту 139 МГц.

Графики переходного процесса фиг.11 позволяют определить tф.ОУ операционного усилителя с входным каскадом-прототипом: tф.ОУ=10 нс. Из их рассмотрения также следует, что предлагаемый входной каскад обеспечивает повышение предельного быстродействия ОУ в 4 раза.

Двухтактные эмиттерные повторители 1 и 8, которые могут применяться в заявляемом устройстве, могут иметь десятки других вариантов построения. Дополнительный пример их практической реализации на элементах 37-42 и 43-48 показаны на чертеже фиг.12, где конденсаторы 49, 50, 51 и 52 моделируют паразитные емкости на подложку источников опорного тока 41, 42, 47 и 48.

Рассмотрим работу входного каскада фиг.4 для случая, когда вторая группа встречно-параллельно включенных р-n переходов 15 отсутствует (см. п.1 формулы изобретения), а на выход 2 от источника сигнала ес2 с внутренним сопротивлением Rc2 подается импульсный сигнал большой амплитуды.

Выходной ток каскада  в схеме на фиг.4 включает две составляющие

в схеме на фиг.4 включает две составляющие

где

Первая составляющая  имеет форму «пилы», так как двухтактный повторитель 1 характеризуется определенной инерционностью передачи сигнала (фиг.3а).

имеет форму «пилы», так как двухтактный повторитель 1 характеризуется определенной инерционностью передачи сигнала (фиг.3а).

Вторая составляющая  имеет достаточно крутой фронт, так как первая группа р-n переходов 14 создает в схеме фиг.4 дополнительный нелинейный канал передачи сигнала со входа 2 на выход 12. В результате, изменения тока выхода 12

имеет достаточно крутой фронт, так как первая группа р-n переходов 14 создает в схеме фиг.4 дополнительный нелинейный канал передачи сигнала со входа 2 на выход 12. В результате, изменения тока выхода 12  становятся более быстрыми, что улучшает динамические параметры ОУ на основе выходного каскада фиг.4.

становятся более быстрыми, что улучшает динамические параметры ОУ на основе выходного каскада фиг.4.

Рассмотрим работу заявляемого устройства в структуре ОУ фиг.8 при работе с импульсными сигналами большой амплитуды, соизмеримой с напряжением источников питания 7 и 5.

Первая группа р-n переходов 14 играет двоякую роль в схеме входного каскада ОУ фиг.8:

1. Во-первых, она ограничивает диапазон изменения входных напряжений в ОУ на уровне Uп=±0,7 B. Это предотвращает пробой р-n переходов транзисторов 16, 17, 18, 19 и позволяет получить (при Сп=С35=С36=0) максимальную скорость нарастания выходного напряжения на уровне

ϑвых=2πf1Uп,

где f1 - частота единичного усиления разомкнутого скорректированного ОУ.

2. Во-вторых, первая группа р-n переходов 14 создает быстродействующий нелинейный канал передачи импульсного тока через резистор 29 в эмиттер транзистора 25 (26) и далее - на вход токового зеркала 32 (31) в емкость коррекции 34. Этот канал «огибает» основной инерционный (из-за влияния емкостей 35, 36) канал передачи входного сигнала ОУ. В результате фронт импульсного тока, перезаряжающего емкость 34, существенно уменьшается, что позволяет получить более высокое быстродействие в ОУ фиг.8 (см. фиг.11).

Данный эффект реализуется при достаточно низкоомном резисторе 29, что характерно для усилителей с токовой обратной связью. По существу, усилитель фиг.8 (благодаря новому входному каскаду) имеет на малом сигнале линейную обратную связь по напряжению, а при больших сигналах - нелинейную токовую обратную связь. Такой «гибрид» обеспечивает получение предельного быстродействия, свойственного усилителю с токовой обратной связью, при сохранении малосигнальных и статических параметров, характерных для усилителей с обратной связью по напряжению.

Результаты компьютерного моделирования (фиг.11) показывают, что введение первой группы р-n переходов повышает предельное быстродействие ОУ (при напряжении питания 15 В) в 4 раза с 2098 В/мкс до 8380 В/мкс.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - Рис.6.11.

2. Операционные усилители с непосредственной связью каскадов / В.И.Анисимов, М.В.Капитонов, Н.Н.Прокопенко, Ю.М.Соколов. - Л., 1979.

3. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М., 1983. - 216 с.

4. Патент США №6710655.

5. Патент США №6710654.

6. Патент США №6492870.

7. Патент США №6542032.

8. Патент США №6249187.

9. Патент США №5150074.

10. Патент США №6262633.

11. Патент США №6188281.

12. Патент США №6429744.

13. Патент США №5512859.

14. Патент США №5399991.

15. Патент США №5510754.

| название | год | авторы | номер документа |

|---|---|---|---|

| ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321156C1 |

| МОСТОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2277753C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2390910C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2784047C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2280318C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2018 |

|

RU2684489C1 |

| ДВУХТАКТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319289C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2577183C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКООМНЫМИ ВХОДАМИ | 2008 |

|

RU2383099C2 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2008 |

|

RU2391768C2 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных и импульсных сигналов, в структуре операционных усилителей, усилителей мощности и аналоговых интерфейсов различного функционального назначения. Технический результат заключается в повышении быстродействия. Входной каскад быстродействующего операционного усилителя (ОУ) с нелинейной токовой обратной связью содержит первый (1) второй (8) двухтактные эмиттерные повторители (ДЭП), между потенциальным выходом (3) первого (1) ДЭП и потенциальным выходом (10) второго (8) ДЭП включен двухполюсник (13). Вход (2) первого (1) ДЭП соединен с потенциальным выходом (10) второго (8) ДЭП через первую группу встречно-параллельно включенных р-n переходов (14). 3 з.п. ф-лы, 12 ил.

| WO 00/19604 A1, 06.04.2000 | |||

| RU 2053592 C1, 27.01.1996 | |||

| Дифферинциальный усилитель | 1975 |

|

SU598215A1 |

| US 6710654 B2, 23.03.2004 | |||

| US 6710655 B2, 23.03.2004. | |||

Авторы

Даты

2008-03-27—Публикация

2006-12-13—Подача