g включенные между общей шиной и эмит2, Элемент по п. 1,, о т л и ч ю щ и и с я тем, что в него введе ны .два дополнительных источника тока,

1200413

терами соответственно первого и второго согласующих транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическая ячейка | 1985 |

|

SU1248056A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| Усилитель считывания | 1988 |

|

SU1580441A1 |

| Параметрический источник опорного напряжения для запоминающего устройства | 1989 |

|

SU1647647A1 |

| Управляемый генератор импульсов | 1984 |

|

SU1188857A1 |

| Логический элемент | 1983 |

|

SU1166296A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Быстродействующий помехоустойчивыйлОгичЕСКий элЕМЕНТ и-или/ и-или-HE | 1978 |

|

SU849488A1 |

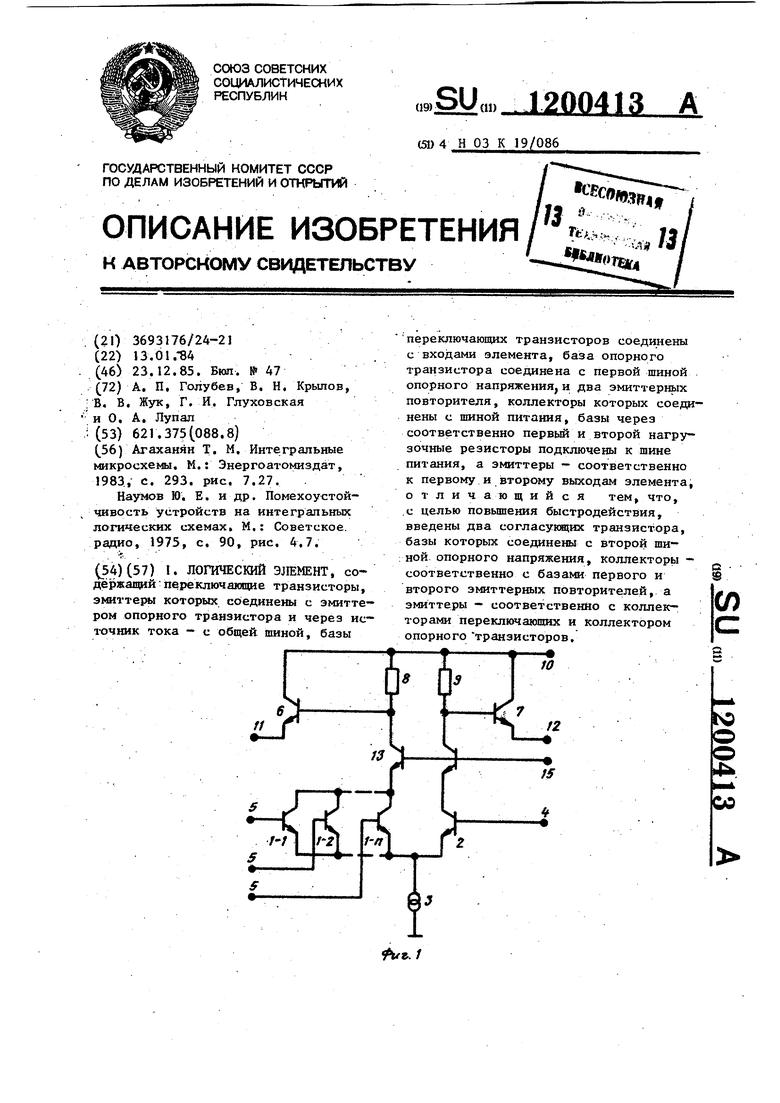

I. ЛОГИЧЕСКИЙ ЭЛЕМЕНТ, содержащий переключающие транзисторы, эмиттеры которых соединены с эмиттером опорного транзистора и через источник тока - с общей шиной, базы ...y. 19, - -.Л IJ fMiroji переключающих транзисторов соединены с входами элемента, база опорного транзистора соединена с первой шиной опорного напряжения, и два эмиттертгх повторителя, коллекторы которых соединены с шиной питания, базы через соответственно первый и второй нагрузочные резисторы подключены к шине питания, а эмиттеры - соответственно к первому и ззторому выходам элемента, о т л и ч а ю щ и и с я тем, что, .с целью повьш1ения быстродействия, введены два согласукщих транзистора, базы которых соединены с второй ши: ной опорного ндпряжения, коллекторы соответственно с базами первого и второго эмиттерных повторителей, а СЛ эмиттеры - соответственно с коллекторами переключающих и коллектором опорного транзисторов. О NU 00

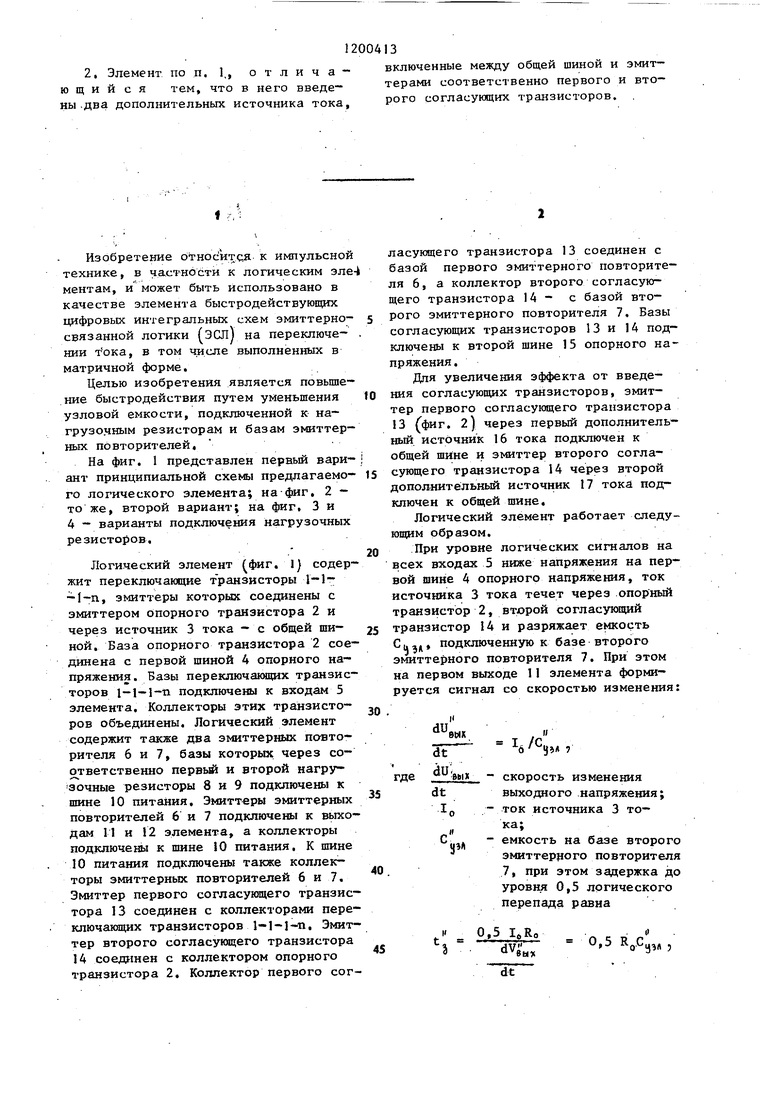

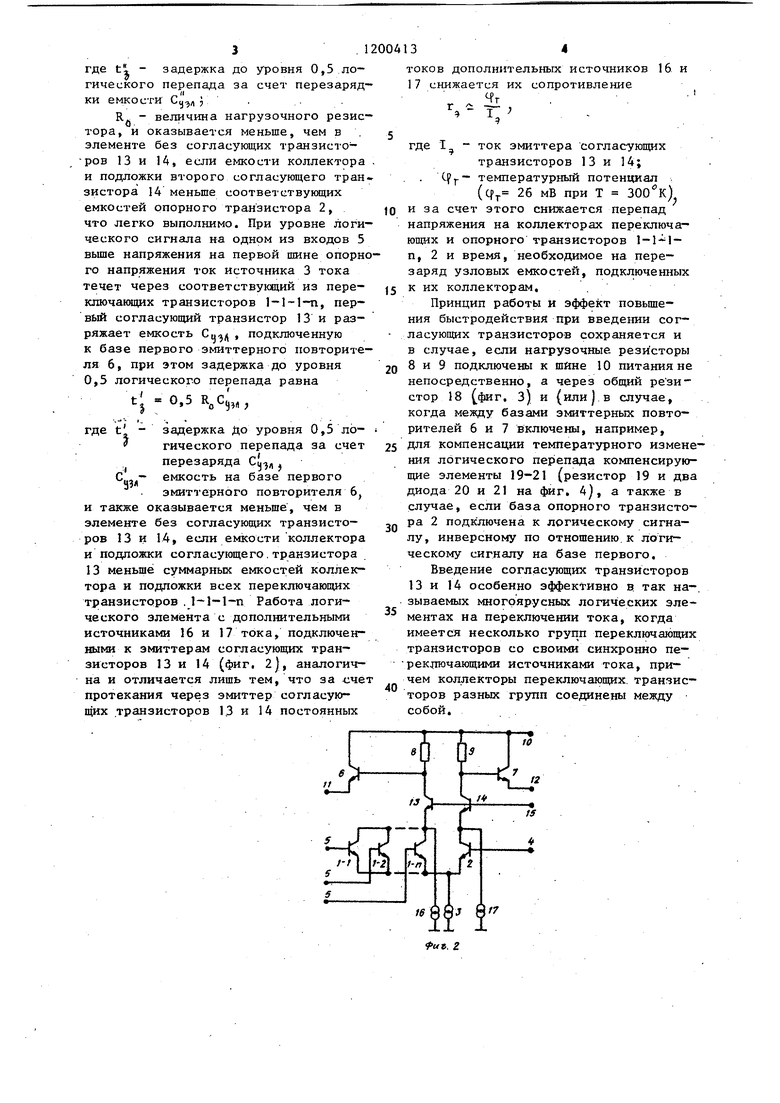

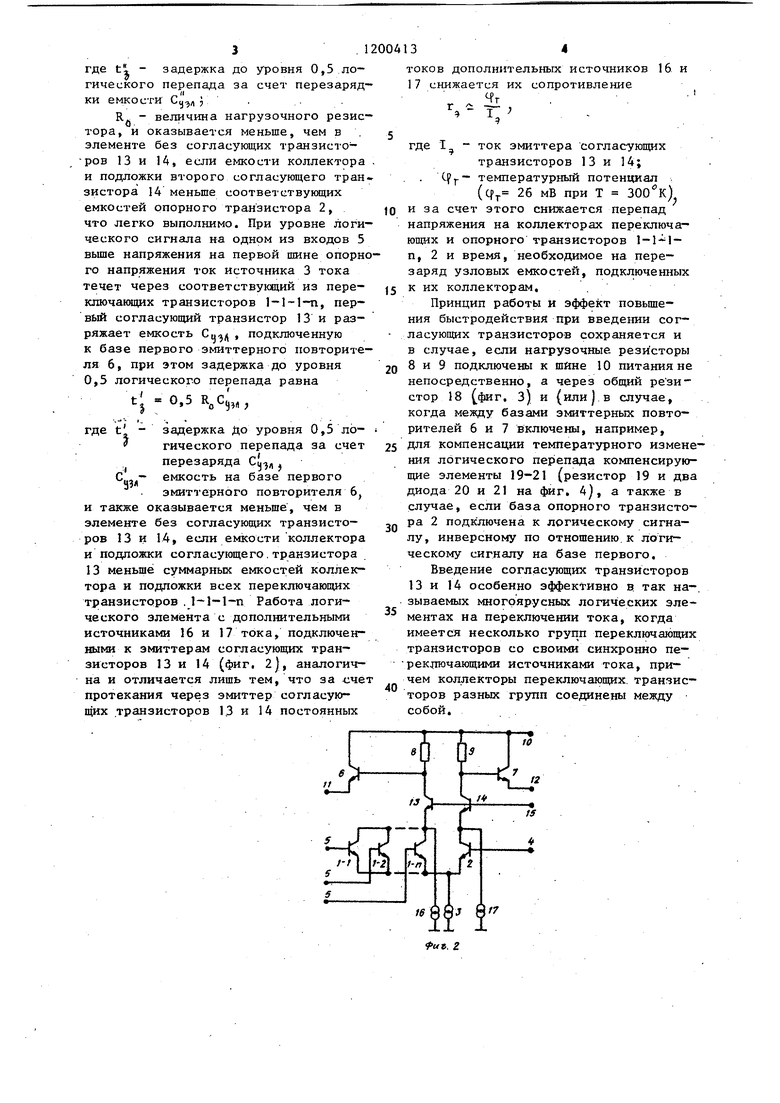

Изобретение относится к импульсной технике, в частности к логическим эле ментам, и может быть использовано в качестве элемента быстродействующих цифровых интегральных схем эмиттерносвязанной логики (ЭСЛ| на переключеНИИ тока, в том числе выполненных в матричной форме. Целью изобретения является повышение быстродействия путем уменьшения узловой емкости, подключенной к нагрузочным резисторам и базам эмиттерных повторителей. На фиг. 1 представлен первый вариант принциписшьной схемы предлагаемого логического элемента; на 4иг. 2 - то же, второй вариант; на фиг, 3 и 4 - варианты подключения нагрузочных резисторов. Логический элемент (фиг, 1) содержит переключающие транзисторы 1-1 -1-п, эмиттеры которых соединены с эмиттером опорного транзистора 2 и через источник 3 тока - с общей шиной. База опорного транзистора 2 соединена с первой шиной 4 опорного напряжения. Вазы переключакнцих транзисторов 1-1-1-п подключены к входам 5 элемента. Коллекторы этизс транзисторов объединены. Логический элемент содержит также два эмиттерных повторителя 6 и 7, базы которых через соответственно перв и второй нагру- зочные резисторы 8 и 9 подключены к шине 10 питания. Эмиттеры эмиттерных повторителей 6 и 7 подключены к выходам М и 12 элемента, а коллекторы подключены к шине 10 питания. К шине 10 питания подключены также коллекторы эмиттерных повторителей 6 и 7. Эмиттер первого согласующего транзистора 13 соединен с коллекторами переключающих транзисторов 1-1-1-та. Эмиттер второго согласующего транзистора 14 соединен с коллектором опорного транзистора 2. Коллектор первого согласующего транзистора 13 соединен с базой первого эмиттерного повторителя 6, а коллектор второго согласующего транзистора 14 - с базой второго эмиттерного повторителя 7. Вазы согласующих транзисторов 13 и 14 подключены к второй шине 15 опорного напряжения. Для увеличения эффекта от введения согласующих транзисторов, эмиттер первого согласующего транзистора 13 {фиг. 2) через первый дополнительный источник 16 тока подключен к общей шине и эмиттер второго согласующего транзистора 14 через второй дополнительный источник 17 тока подключен к общей шине. Логический элемент работает следующим образом. При уровне логических сигналов на всех входах 5 ниже напряжения на первой шине 4 опорного напряжения, ток источника 3 тока течет через опорный транзистор 2, второй согласующий транзистор 14 и разряжает емкость Cцa( подключенную к базе второго эмиттерного повторителя 7. При этом на первом выходе 11 элемента формируется сигнал со скоростью изменения: 1б /S. скорость изменения выходного напряжения; ток источника 3 тока;емкость на базе второго эмиттеррого повторителя 7 при этом задержка до уровня 0,5 логического перепада равна 0,5 0.5 К,.Су„ , 3. - задержка до уровня 0,5 логического перепада за счет перезаряд ки емкости С,л 5 . R - величина нагрузочного резис тора, и оказывается меньше, чем в . элементе без согласующих транзисторов 13 и 14, если емкости коллектора и подложки второго согласующего тран зистора 14 меньше соответствующих емкостей опорного транзистора 2, что легко выполнимо. При уровне логи ческого сигнала на одном из входов 5 выше напряжения на первой шине опорн го напряжения ток источника 3 тока течет через соответствующий из переключающих транзисторов , первьй согласующий транзистор 13 и разряжает емкость Cu} , подключенную к базе первого змиттерного повторите ля 6, при этом задержка до уровня 0,5 логического перепада равна 0.5 ,, задержка До уровня 0,5 логического перепада за счет перезаряда cL емкость на базе первого эмиттерного повторителя 6j и также оказывается меньше , чем в элементе без согласуюсцих транзисторов 13 и 14, если емкости коллектора и подложки согласующего.транзистора 13 меньше суммарных емкостей коллектора и подложки всех переключающих транзисторов .l-1-l-n Работа логического элемента с дополнительными источниками 16 и 17 тока, подключенными к эмиттерам согласующих транзисторов 13 и 14 (фиг. 2), аналогична и отличается лишь тем, что за :че протекания через эмиттер согласующих транзисторов 13 и 14 постоянных 34 токов дополнительных источников 16 и 17 снижается их сопротивление ; . , . S- 1, где I.J - ток эмиттера согласующих транзисторов 13 и 14; . ( температурный потенциал . (q 26 мВ при Т ) и за счет этого снижается перепад напряжения на коллекторах переключа- и опорного транзисторов , 2 и время, необходимое на перезаряд узловых емкостей, подключенных к их коллекторам, . Принцип работы и эффект повьщ1ения быстродействия при введении согласующих транзисторов сохраняется и в случае, если нагрузочные резисторы 8 и 9 подключены к шине 10 питания не непосредственно, а через общий резистор 18 (фиг, З) и (или) в случае, когда между базами эмиттерных повторителей 6 и 7 включены, например, для компенсации температурного изменения логического перепада компенсирующие элементы 19-21 (резистор 19 и два диода 20 и 21 на фиг. 4), а также в случае, если база опорного транзистора 2 подключена к логическому сигналу, инверсному по отношению.к логическому сигналу на базе первого. Введение согласующих транзисторов 13 и 14 особенно эффективно в так на-, зываемых многоярусных логических элементах на переключении тока, когда имеется несколько групп переключающих транзисторов со своими синхронно пе- реклгачающими источниками тока, причем коллекторы переключающих, транзисторов разных групп соединены между собой.

if т

ГТ

fMt.3

Jp p

-,

/« /

y

| Агаханян Т | |||

| М | |||

| Интегральные микросхемы | |||

| М.: Энергоатомиздат, 1983, с | |||

| ПРИСПОСОБЛЕНИЕ ДЛЯ ПОДАЧИ УГЛЯ В ТЕНДЕР ПАРОВОЗА | 1920 |

|

SU293A1 |

| рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Наумов Ю | |||

| Е | |||

| и др | |||

| Помехоу :тойчивость устройств на интегральных логических схемах, М.: Советское, радио, 1975, с | |||

| Пожарный двухцилиндровый насос | 0 |

|

SU90A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-12-23—Публикация

1984-01-13—Подача