Г

Изобретение относится к цифровой вычислительной технике и может быть использовано в составе цифровой вычислительной машины.

Известно устройство управления векторным процессором последовательного действия. В состав устройства входят регистры сдвига к сумматоры последовательного действия 1.

Недостатком такого устройства является низкая производительность обработки информации.

Наиболее близким по технической ; сущности и достигаемому результату к изобретению является устройство управления вычислительной машины.

Устройство содержит блок си ахронизирующих импульсов и блок операций, которые соединены между собой взаимнообратной связью. Выход блока синхронизирующих импульсов соединен с первыми входами счетчика циклов, коммутатора регистров, блока знака операции, триггера двойных итераций и счетчика итераций, а вторые входы всех упомянутых блоков соединены с выходом блока операций. Выход счетчика итераций подключен к первым входам коммутатора сдвигов и блока |)Ормирования адреса, а выход

счетчика циклов соединен с третьими входами триггера двойных итераций и хзчетчика итераций, который четвертым входом соединен с выходом триггера двойных итераций. Второй выход счетчика циклов подключен к третьему входу коммутатора регистров, первый выход которого подключен к первому, выходу устройства, а второй выход - .

10 к третьему входу блока знака операции,- выход которого является вторым выходом устройства, а четвертый вход блока знака операции соединен с магистралью управляющих сигналов ариф15метического устройства процессора. Третий и четвертый выходы устройства соединены соответственно с выходами коммутатора сдвигов и блока формирования адреса 2.

20

Недостаток известного устройства состоит в том, что в нем не предусмотрено автономное масштабирование исходных координат вектора, что приводит к уменьшению производительнос25ти векторного процессора и требует специального устройства умножения.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем,

30 что устройство управления векториьол

процессором, содержащее узел синхронизации, счетчик циклов,, первый триггер, счетчик итергщий, узел формироваиия знака, регистр сдвига, блок памяти сщресов, коммутатор,причем тактовые входы счетчика циклов, первого триггера, счетчика итераций, коммутатора и узла формирования знака соединены с первым выходом узла синхронизации, второй выход узла синхронизации является тактовым выхо дом устройства, информационные входы регистра сдвига и блока пгшяти адресов соединены с выходом счетчика итераций, информационные входы счетчика циклов и счетчика итераций, первого триггера, коьо утатора, узла формироваиия знака, регистра сдвига и блока памяти адресов соединены с соответствующими входами rpyntoi информационных входов устройства, единичный вход первого триггера и управляющий вход счетчика нтерраций соединены с первым выходом счетчика циклов, сум14иру1сщий вход счётчика итераций соединен с выходом первого триггера, первый выход коммутатора явля-г ется переключающим выходом устройст .ва, второй выход коммутат ч я соединен с третьим входом узла формирования знака, выход узла формирования знака является знаковым выходом устройства, выход регистра сдвига является разрешаюцим выходом устройства, выход блока Пс1мяти гицресов является адресным выходом устройства, четвертый вход узла формирования зиака является разрешающими входом устройства, третий вход коммутатора соединен со вторым выходом счетчика циклов, введены второй триггер и блок элементов И, причем тактовый вход второго триггера соединен с выходом узла синхронизации, первый вход блока элементов И соединен с выходом счетчика итераций, информационный вход второго триггера соединен с информационным входом устройства, единичный вход второго триггера соединен с третьим выходом коигмутатора, ||улевой вход второго триггера соединен с выходом блока элементов И, разрешающий вход счетчика итергихий, иулеврй вход первого триггера и второй вход .блока элементов И соединены с перв выходом вто ого триггера, второй выход второго триггера соединен с пятым входом узла формирования знака lii с управляющим входом счетчика циклов.

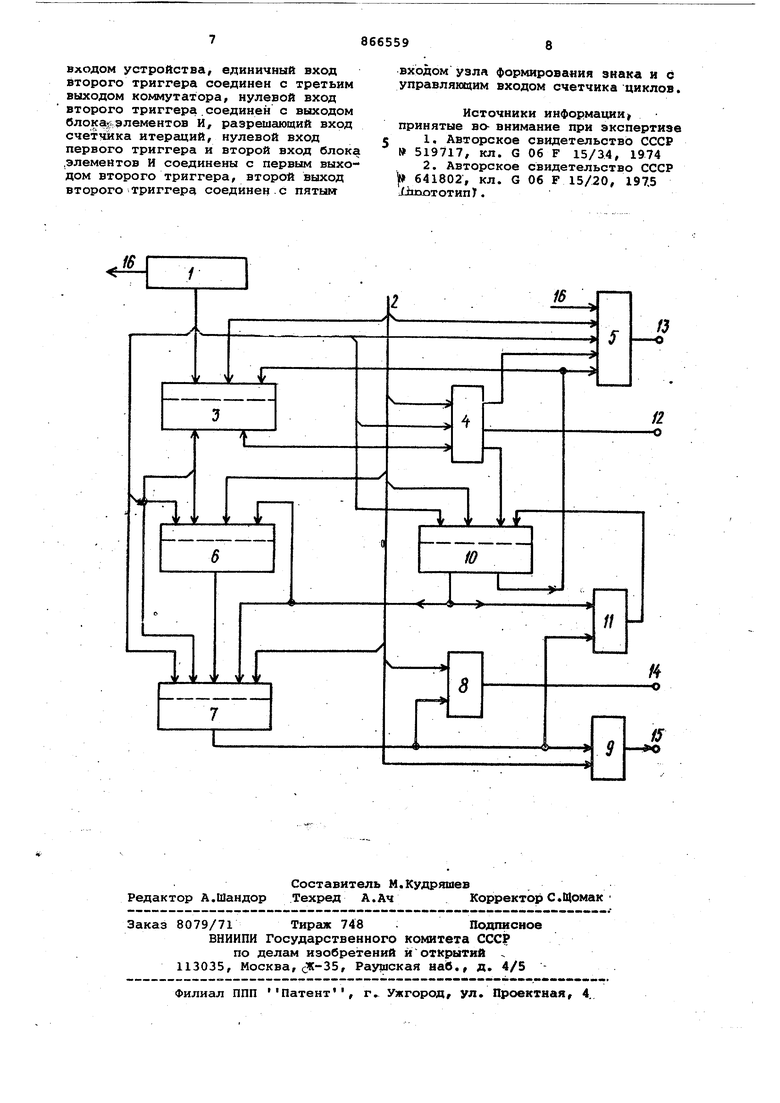

На чертеже приведена структурная схема устройства

Устройство содержит узел 1 синхронизации, группу информсощонных входов 2 устройства, счетчик 3 циклов, коьл татор 4, блок 5 формирования знака, триггер 6, счетчик 7 итераций регистр 8 сдвига, блок 9 ламяти адресов, триггер 10, блок -И элементов И, переключающий выход 12 устройства, знаковый выход 13 устройст- ва, разрешающий выход 14 устройства,; адресный выход 15 устройства, тактовый выход 16 устройства.

Работу устройства рассмотрим иа 5 примере вычисления функции arcein 4fX аппаратурным способом по методу цифра за цифрой, в основу которого положено вращение вектора на заранее расчитанн$ ю последовательность углов. 0 Вычислительная процедура этого метода описывается следующей сводкой Формул:f л

i х,-. - .- (1) У1- У4-1 + .. (2) cL4 (3)

У где индекс 1 характеризует номер BI полняемой итерации.

Максшкёшьное значение 1 равно количеству разрядов п в обрабатываемом числ. Подсчет количества итергщий0 ведется счетчиком 7. Для ложных функций типа arcsln каждая итерация дрлжна выполняться дважды, для чего предусмотрен триггер 6, коммутирующий входные сигналы для счётчика итера5

Qi - угловые константы, хранящиеся в запоминающем устройстве, адрес которых формируется блоком 9с учетом содержимого счетчика 7 и выполQ няемой операции, сигнал о которой поступает с входа 2.

В рассматриваемом алгоритме операция умножения оперантов . и на заменена операцией сдвига

, этих операндов вправо на (1-1) разряд, для чего предусмотрен регистр 8. Знак операции в формулах 1-3 зависит от значения оператора поворота шектора Е, равного +1.

0 Для функции arcsin Ei -1, если у;. /y|v иначе Б,- +1. Окончательный знак операции в формулах 1-3 формируется узлом 5, который по входу 16 получает инфорг мацию о знаке числа х -- и сравнимости числе у и fy/ из арифметического устройства процессора.

Рассматриваемое устройство управления предусмотрено для последовательно-параллельной обработки информации, т.е. формулы 1-3 будут выполняться последовательно одним арифметическим устройством параллельного действия. Для организации такой работы в устройстве предусмотрен

5 счетчик 3 и коммутатор 4. «Счетчик 3 работает с коэффициентом пересчета 3, а коммутатор формирует управляющие сигналы для соответствующих регис фов арифметического устройства и блока знака опергщий.

Отличительная особенность рассматриваемого алгоритма заключается в том, что при кгакдом повороте вектора на угол происходит удпинение его

5 координат раза, а общие удлинение за п двойных итераций рав но коэффициенту К, определяемому вы ражеииемк-ftiH+a2t -). . Для того/ чтобы учесть отмеченно удлинение, начгшьные координаты век тора в известных устройствах перед вычислением функции масштабируют, т задают в масштабе К, а именно: . YO-T; d,-o: Масштабирование требует выполнения двух команд умножения, что приводит к снижению производительности tipoueccopa и требует обязательного Нсшичия схемы умножения. В рассматриваемом устройстве коэффициент 1/К представлен в виде набора сомножителей, которые образу слеяупцую реккурентную формулу; 4---0,5 nCl-l- ; где К - элементы массива числа Р. Дпя 32-х разрядного процессора они имеют следующие значения: Р 2,6,10,14,18,22,26,30,31. Для компенсации отмеченного удли нения при тех значениях индекса i, для которого выполняется равенство (1-1) Рj, необходимо скорректировать координаты вектора по следую щим формул сил: V. v. -у. Л.-Х.;, А,. Ч -Ч- -У 1-1 1-1После выполнения текущего мас| Ггабирования можно переходить к выполнеиию алгоритма по формулам 1-3. ; Для регшизации данного варианта масштабирования в состав устройства введены триггер 10 масштабирования и блок 11, управляющие сигналы для которых формируются счетчиком 7 иа двоичных кодах чисел элементов MiacсиваР. Триггер 10 предварительно устанавливается в ноль и вьфабатывает разрешшощие потенциалы для: бло ков 6, 7 и 11. При (i - I) Р/, срабатывает блок 11, переключая Timrrep 10 в противоположное состоя ние, в результате чего по сигиашу о второго выхода триггера 10 в счетчи циклов записывается коэффициеит пересчета два для выполнения фоЕМул 4 и 5. Одновременно блок 5Получает У1фавляю11|йй сигнал для формировгшн соответствующего знака операции в формулах 4 и 5. После выполнения (1 - 1) итерации вместе с масштабированием с третьего выхода коммутатора 4 поступает сигНсШ для переключения триггера 10 в исходное нулевое состояние. Таким образом, устройство управления-йозволяет повысить производительность обработки информсщии,например, для 32-х разрядного процессора операция масштабирования координаты вектора выполняются за время 9 ко манд сложения, что в 3-5 раза быстрее по сравнению с обычным умйожением. Формула изобретения Устройство управления векторным процессором, содержащее . узел синхронизащии, счетчик циклов, первый xpiirгер, счетчик итераций, узел формирования знака, регистр сдвига, блок памяти адресов, коммутатор, причем. тактовые входы счетчика циклов, первого триггера, счетчика итераций, коммутатора и узла формирования знака соединены с перв10« выходом узла синхронизгщии, тррой выход узла синхронизации является тактовым выходом устройства, информационные входы регистра сдвига,и блока памяти адресов соединены с выходом счетчика итераций, информационные входы счетчика циклов, счетчика итераций, первого триггера, коммутатора, узла формирования знака, регистра сдвига и блока памяти адресов соединены с соответствующими входами группы информационных входов устройства, единичный вход первого тригге ра и управляющий вход счетчика итераций соединены с первым выходом счетчика циклов, суммируюций вход счетчика 1 тераций соединен с выходом первого триггера, первый выход коммутатора является переключающим выходом устройства, второй выхсщ коммутатсфа соединен с третьим входом узла формирования знака, выход узла формирования знака является знаковым выходом устройства, выход регистра сдвига является разрешающим выходом уст-; .ройства, выход блока памяти адресов является ада есным выходом устройства, четвертый вход узла фоЕмирования .знака является разрешгиощим входом устройства, третий вход коммутатора соединен со втосалм выходом счетчика циклов, отличающееся тем, что, с целью повышения производител ьности, устройство содержит второй триггер и блок злементов И, причем тактовый вход второго триггера соединен с выходом узла синхронизгщии, первый вход блока злементов И соединеи с выхасом счетчика итера1и1й, информационный вход второго триггера соединен с информационным

входом устройства, единичный вход второго триггера соединен с третьим выходом коммутатора, нулевой вход второго триггера.соединен с выходом блока :9лементов И, разрешающий вход счетчика итераций, нулевой вход первого триггера и второй вход блока .элементов И соединены с первым выходом второго триггера, второй выход второго триггера соединен с пятым

входом узла формирова«ия знака и с управляющим входом счетчика циклов.

Источники информации принятые во- внимание при экспертизе

1.Авторское свидетельство СССР 519717, кл. G 06 F 15/34, 1974

2.Авторское свидетельство СССР 641802, кл. G 06 F 15/20, 197.5 ХйсютотипТ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Векторный процессор | 1979 |

|

SU849228A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство управления для процессора быстрого преобразования Фурье | 1984 |

|

SU1270775A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1982 |

|

SU1056207A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Многоканальное операционное устройство | 1982 |

|

SU1124292A1 |

Авторы

Даты

1981-09-23—Публикация

1979-12-04—Подача