(54) ВЕКТОРНЫЙ ПРОЦЕССОР Изобретение относится к цифровой вычислительной технике и может использоваться, в высокопроизводительных вычислительных системах. Известно вычислительное устройство последовательного действия, содержащее три арифметических устройства последовательного действия с общим устройством управления. Арифме тические устройства содержат последовательные регистры сдвига и последовательные сумматоры, причем, в двух арифметических устройствах линейных координат вектора имеется па два пос ледовательно включенных сумматора { Недостатком этого устройства является низкая производительность обработки информации. Наиболее близким к изобретению по технической сущности является мультипроцессорное вычислительное устройство с параллельной обработкой информации, которое содержит три . процессора параллельного действия и способно аппаратурным способом выполнять векторные операции вычисления полярных .и прямоугольных коорди нат вектора. Два процессора являются процессо рами обработки линейных координат вектора, а третий является процессором обработки УГЛОВОЙ координаты вектора, причем каждый из ник имеет последовательно соединенные прием- ный регистр,, параллельный сдвигатель, блок прямой/инверсной выдачи, сумматор, выходной регистр,буферный регистр вьБСОд которого подключен на второй вход сумматора. Кроме того, буферные и приемные регистры соединены с первым выходом распределителя тактовых импульсов, а выходные регистры - с вторым выходом распределителя, третий выход которого соединен с первыми входами триггера двойных итераций и счетчика итераций, выход которого соединен с блоками формирования сигналов сдвига и формирования адреса, выходы которых подключены соответственно к второму входу параллельного сдвигателя и . блоку постоянной памяти, вторые выходы выходных регистров соединены с первым входом блока формирования знака операции, которого соединен с вторьоми входами блоков прямой/инвареной выдачи, второй вход триггера двойных итераций соединен с первым выходом блока операций, который соединен взаимнробратной связью с расределителем тактовых импульсов. Перый выход триггера двойных итераций оединен с вторыми входами счетчика итераций и блока формирования адреа, а второй выход триггера соединен вторыми.входами блоков формирования сигналов сдвига и знака операций. Второй, третий и четвертый выоды блока операций соединены соответственно с третьими входами счетика итераций, блоков формирования сигналов сдвига и адреса и блока формирования знака операции Г,

Недостатком известного устройства является его ограниченные функциональные возможности,так как оно не позволяет вычислить аппаратурным способом обратные тригонометрические функции arcsin и arccos.

Цель изобретения - повышение про- , изводительности и расширение класса решаемых задач.

Поставленная цель достигается тем, что в процессор, содержащий блок постоянной памяти, блок синхронизации, счетчик итераций, триггер двойных итераций, блок формирования сигналов сдвига, блок формирования адреса, блок формирования знака операции, два блока обработки линейной координаты, блок обработки угловой координаты, причем каждый блок обработки линейных координат содержит приемный регистр, выходной регистр, буферный регистр, сумматорвычйтатель, коммутатор сдвига, а блок обработки угловой координаты содержит приемный регистр, выходной регистр, буферный регистр, сумматррвычитатель, первый выход блока синхронизации соединен с первым входом счетчика итераций и входом триггера двойных итераций, второй выход блока синхронизации соединен с первым входом блока формирования знака операции, первыми входами приемньах регистров и буферных регистров, третий выход блока синхронизации подключен к второму входу блока формирования знака операции и первым входам выходных регистров, четвертый выход блока синхронизации подключен к первым входам блока формирования сигналов сдвига и блока формирования адреса, пятый выход блока синхронизации соединен с третьим входом блока формирования знака операции, четвертый, пятый, шестой и седьмой входы которого подключены соответственно к выходу приемного регистра блока обработки угловой координаты, первым, выходам выходных регистров блока обработки угловой координаты, первого и второго блоков обработки линейной координаты, первый выход триггера двойных итераций подключен к вторым входам четчика итераций и блока формирования адрес, ВЫХод которого соединен с входом блока постоянной памяти,, второй выход триггера двойных итераций соединен с восьмым входом блока, формирования знака операции и вторым входом блока формирования сигналов сдвига, выход счетчика итераций соединен с третьими входами блока формирования адреса и блока формирования сигналов сдвига, выход которого соединен с первыми входами коммутаторов сдвига первого и второго блоков обработки линейных координат, выход блока .формирования знака операции соединен с первыми входами сумматороввычитателей, в каждом из блоков обработки линейных координат выход коммутатора сдвига соединен с вторым входом сумматора-вычитателя, третий вход которого подключен к выходу буферного регистра, выход сумматора-вычитателя соединен с вторым в содом выходного регистра, второй вход коммутатора сдвига под-гключен к выходу приемного регистра, второй выход выходного регистра каждого блока обработки линейной координаты соединен с вторыми входами буферного регистра своего и приемного регистра другого блока обработки линейной координаты, в блоке обработки угловой координаты выход сумматора-вычитателя соединен с вторым входом выходного регистра, второй выход которого соединен с вторым входом буферного регистра , выход которого соединен с третьим входом сумматора-вычитателя, в блок.обработки угловой координаты дополнит льно введен коммутатор сдвига, выход которого соединен с входом сумматора-вычитателя блока, первый и второй входы коммутатора сдвига подключены соответственно с выходом блока формирования сигналов сдвига и блока постоянной памяти, третьи входы коммутаторов сдвига блоков обработки линейной координаты и блока обработки угловой координаты подключены соответственно к выходам буферных регистров этих блоков, а выход приемного регистра блока обработки угловой координаты Соединен, кроме того, с четвертым.входом коммутатора сдвига и третьим входом буферного регистра этого блока.

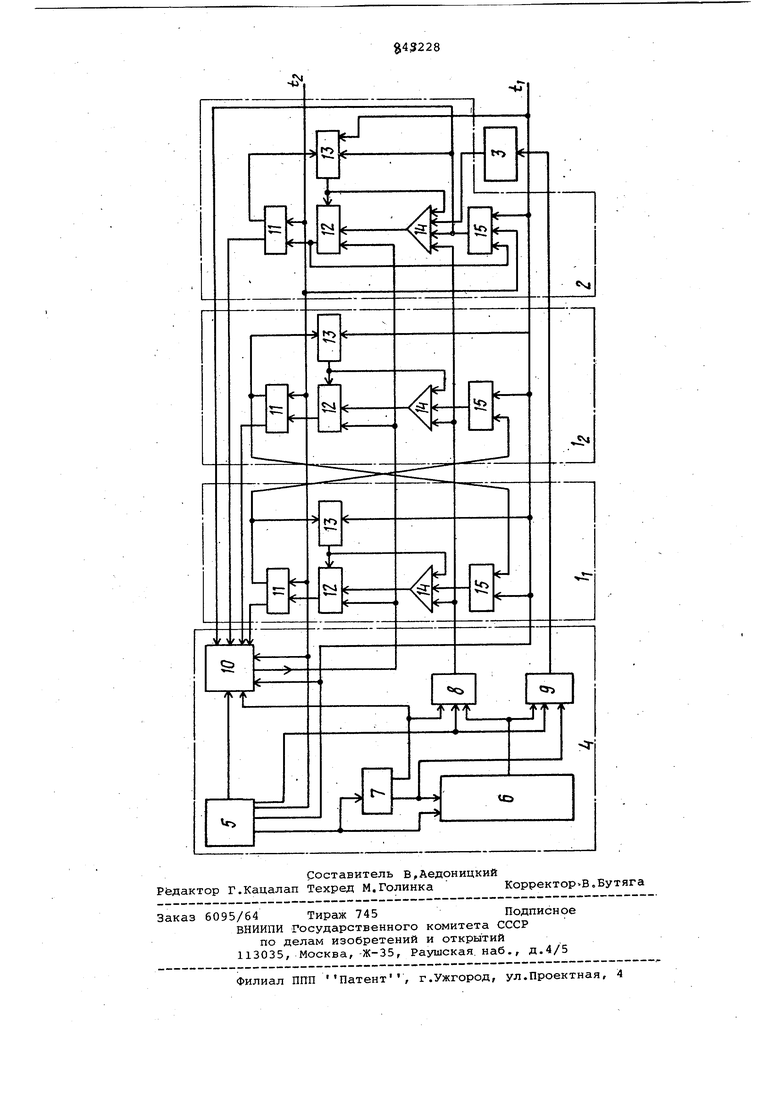

На чертеже приведена структурная схема векторного процессора.

Устройство содержит блоки 1 и li обработки линейных координат вектора, блок 2 обработки угловой координаты вектора, блок 3 постоянной памяти, устройство 4 управления, включающее блок 5 синхронизации, счетчик 6 итераций, триггер 7 двойных итераций, блок 8 формирования сигналов сдвига, блок 9 формирования адреса и блок 10 формирования знака операции. Блоки 1 , 1 и 2 содержат соотв ственно выходные регистры И -llj , сумматоры , буферные регист ры 13, -13j , коммутаторы 14 э сд га и приемные реггистры . Элементарные функции arcsin и arccos можно вычислить аппаратурны способом, используя численный мето цифра за цифрой; В основу этого метода положен итерационный вычисл тельный процесс с фиксированньом ко личеством итераций п, которые производятся над вектором, заданным координатами {},у} Вектор вращае ся в декартовой системе координат на заранее предрассчитанную послед вательность углов, которые определ ются выражением -(i-a) . 0. arctg 2 ; ,n, где i - номер очередной итерации; ji - количество разрядов в числ Эти константы хра нятся в блоке постоянной памяти. , ГГри вычислении функции arcsin Z первоначальный вектор располагают по оси абсцисс и вращают его в так направлении,что Y стремится к 2.Пр вычислении функции arccos. Z/x перво начальный вектор располагают по оси ординат и вращают его в таком направлении, что X стремится к Z. С целью сходимости методацифра за цифройкаждую итерацию необходимо повторять дважды, поэтому в составе устройства имеется триггер 7 двойных итераций. Вычислительная процедура для фун кций arcsin и arccos описывается фо мулами -e(i-2) -(.--i) . -х-, 2 . -Е,-у- 2 ,-Ч; ч, , 1Т-1 . --i г1 -у -у- +Е-Х- 2 ; f.i.IT-, т/-, . , +Е; 2Q ; ., +Z;., 2-(-). Для функции arcsin . 1+1 при- У;. Z;, . 1-1 пр У,.:, / 2., а для функции arccos Е,. (+1 ПР i- 2v- t (.-1 при Х. Zjf. , От значения Е; завис ит направление вращ.ения вектора и, как следствие, знак выполняемой операции в приведенных формулах. В приведенной сводке формул вычи лительная процедура представлена та ким образом,что знак Е операции на две итерации одного номера определяется один раз. На первом этапе вычисляют Е. Sign.(y. , ) X v. -V 22(-«) «,-1 . .2f,. / V,1 V -V. -( I , Л г-(.i в первом блоке 1 вычисляют X, во втором блоке Y, а в блоке 2 - Z и oi.- , Знак Е; операции определяется блоком 10, который может быть выполнен по схеме сумматора или сравнивающего устройства. Перед выполнением i-й итерации х находится в регистре 11, ., в регистре 11, а Z;.-B регистре 15. Триггер 7 двойных итераций устанавливается распределителем 5 в одно из устойчивых состояний, а в счетчике б итераций записывается число i-2, которое блоком 8 расшифровывается и поступает на сдвигатели 14. Первым тактовым импульсом t, содержимое выходных регистров 11 и 11 переписывается в буферные регистры 13., и 13,j , а содержимое регистра 15j в регистр I3j. Учитывая, что выход буферных регистров 13 подключен на входы сумматора и сдвигателя, происходит сложение (вычитание) соответствующих одноименных операндов, один из которых сдвинут вправо на 2(1-2) разрядов. Результат-.выполненной операции вторым тактовым импульсом t записывается в соответствующий регистр, т. е .х- - в регистр 11., , У; в регистр llj, а Z; - в регистр 15,. На втором этапе вычисляются х х;-Е,У., . 2 . ,; У; у +Е;х;., . 2 Ot. ct,,.,+E2Q;. Для реализации этих формул необходимы значения и у;. . Они на первом эт.апе первым тактовым импуль- сом ti переписываются перекрестно в противоположные приемные регистры, т.е. х;., из регистра 11 в регистр. 15, а у; из регистра ll в регистр 15, . С учетом произведенной подготов15 . С учетом произведенной подготов второй этап также выполняется двуМЯ ТЯНТПТЗЫМИ ММПУПКГЯМИ OHonvIfllllMM МЯ тактовыми импульсами следующим образом. Первым тактовым импульсом и - переписываются из регистров 11, и llfj соответственно в регистры 13 и 135, а из регистра 11л, в регистр 13. Вторые операнды Формул поступают на сумматор через сДвигатель 14 соответственно из регистров 15 и 15 и блока 3. Вторым тактовым импульсом результат сумматоров 12 записывается соответственно в выходные регистры II.-HT,Перед выполнением второго этапа четчик b итерации и триггер / устаавливаются в- соответствующее полоение, выдавая управляющие сигналы локам 8, 10 и 9. После исполнен;1я рассмотренных войных итераций в ответе получают регистре 11, значение функции rcsin Z/x; в регистре 11 - значеие косинуса угла; в регистре 11,начение синуса угла. Функция arccos вычисляется аналоичным образом, в целях экономии оборудования исходную координату вектора X целесообразно записать в регист 11, а У - -в регистр 11 . При таком расположении исходНЬх данных экономится дополнительная связь регистра 11 с 6ЛО1СОМ 10. Таким образом,, предлагаемый процессор обладает расширенными функци ональньоми во.зможностями, позволяет сэкономить оборудование и повысить производительность обработки информации, так как за время двух команд умножения вычисляются одновременно функции .arcsin(arccos), sin и cos. Формула изобретения Векторный процессор, содержащий блок постоянной памяти, блок синхро низации, счетчик итераций, триггер двойных итераций, блок формирования сигналов сдвига, блок формирования адреса, блок, формирования знака опе рации, два блока обработки . линейно координаты, блок обработки угловой координаты, причем каждый блок обра ботки линейных координат содержит приемный регистр, выходной регистр, буферный регистр, сумматор-вычитатель, коммутатор сдвига, а блок обр ботки угловой координаты содержит приемный регистр, выходной регистр, буферный регистр, сумматор-вычитатель, первый выход блока синхронизации соединен с первым входом счет чика итераций и входом триггера двойных итераций, второй выход блока синхронизации соединен с первым входом блока формирования знака опе рации, первыми входами приемных регистров и буферных регистров, тре тий выход блока синхронизации подключей к второму входу блока формирования знака операции и первым входам выходных регистров, четвертый выход блока синхронизации подключен к первым входам блока формирования сигналов сдвига и блока фор мирования адреса, пятый выход блока синхронизации соединен с тре.тьим входом блока формирования знака опе рации, четвертый, пятый, шестой и седьмой входы которого подключены соответственно к выходу приемного регистра блока обработки угловой ко ординаты, первым выходам выходных регистров блока обработки угловой координаты, первого и второго блоков обработки линейной координаты, первый выход триггера двойных итера ций подключен к вторым входам счет чика итераций и блока формирования адреса, выход которого соединен с входом блока постоянной памяти, второй выход Tpijrrepa двойных итераций соединен с восьмым входом блока формирования знака операции и вторым входом блока формирования сигналов сдвига, выход счетчика итераций соединен с третьими входами блока Формирования адреса и блока формирования сигналов сдвига, вtлkoд которого соединен с первыми входами коммутаторов сдвига первого и второго блоков обработки линейных координат, выход блока формирования знака операции соединен с первыми входами сумматоров-вычитателей, в каждом из блоков обработки линейных координат выход коммутатора сдвига соединен с вторым входом сумматора-вычитателя, третий вход которого подключен к выходу буферного регистра, выход сумматоравычитателя соединен с вторым входом выходного регистра, второй вход коммутатора сдвига подключен к выходу приемного регистра,второй выход выходного регистра каждого блока обрабЪтки -линейной координаты соединен с вторыми входами буферного регистра своего и приемного регистра другого блока обработки линейной координаты, в блоке обработки угловой координаты выход сумматора-вычитателя соединен с вторым входом выходного регистра, второй выход которого соединен с вторым входом буферного регистра, выход которого соединен с третьим входом сумматора-вычитателя, отличающийся тем, что, с целью повышения производительности и расширения класса оешаемых задач, в блок обработки угловой координаты введен коммутатор с двига, выход которого соединен с входом сумматора-вычитателя блока, первый и второй входы коммутаTqpa с пвига подключены соответственно к выходам блока формирования сигналов сдвига и блока постоянной памяти, третьи входы коммутаторов сдвига блоков обработки линейной координаты и блока обработки угловой координаты подключены соответственно к выходам буферных регистров этих блоков, а выход приемного регистра блока обработки угловой координаты соединен, кроме TorOj с четвертым входом коммутатора сдвига и третьим входом буферного регистра этого блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 445042, кл. G Об F 7/38, 1975. 2.Авторское свидетельство СССР № 492880, кл. G Об F 15/34. 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультипроцессорное вычислительное устройство с параллельной обработкой информации | 1972 |

|

SU492880A1 |

| Многоканальное операционное устройство | 1982 |

|

SU1124292A1 |

| Устройство управления векторным процессом | 1979 |

|

SU866559A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Вычислительное устройство | 1981 |

|

SU1136147A1 |

| Цифровой преобразователь координат | 1981 |

|

SU1076903A1 |

| Процессор цифровой обработки сигналов | 1990 |

|

SU1789991A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Цифровой анализатор спектра | 1987 |

|

SU1413545A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

Авторы

Даты

1981-07-23—Публикация

1979-10-12—Подача