(54) УСТРОЙСТВО КВАНТОВАННОЙ ВРЕМЕННОЙ ЗАДЕРЖКИ ИМПУЛЬСНЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1990 |

|

SU1777168A1 |

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU875622A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| Преобразователь интервалов времени в цифровой код | 1984 |

|

SU1255984A2 |

| Преобразователь время-код | 1991 |

|

SU1785073A1 |

| Аналого-цифровой преобразователь знакопеременных сигналов | 1987 |

|

SU1483641A1 |

| Устройство для вывода графической информации | 1978 |

|

SU752403A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2004 |

|

RU2260830C1 |

| Устройство для отображения графической информации на экране электроннолучевой трубки | 1976 |

|

SU624251A1 |

I

Изобретение относится к цифровой преобразовательной технике и может «быть использовано в преобразователях кода во временной интервал.

Известны устройства для получения временной задержки, основанные на принципе использования двух импульсных потоков с периодами следования импульсов и Т2соответствеино,различаихцихся на единицу дискретности Д:: -ь V. Для получения требуе- мой задержки И-Л совмещают начала обоих импульсных потоков, подсчитывают количество импульсов в обоих потоках, в качестве начала временной задержки выделяют h-ый импульс потока с периодом следования , а в качестве конца -й-ый импульс потока с периодом .

Однако в этих устройствах рабочей задержкой является интервал П()г задержанный относительно начала счёта на величину И - T-j , т.е. с

увеличением И сдвиг рабочей задержки растет монотонно.

Известно также устройство для получения квантованной задержки импульсных сигналов, в котором достигается значительное уменьшение сдвига рабочей задержки. Устройство содержит генераторы основного и дополнительного импульсных потоков счётчики импульсов, сумматор, блоки совпадения кодов и регистр кода требуемой задержки. В этом устройстве периоды следования импульсных потоков различаются на

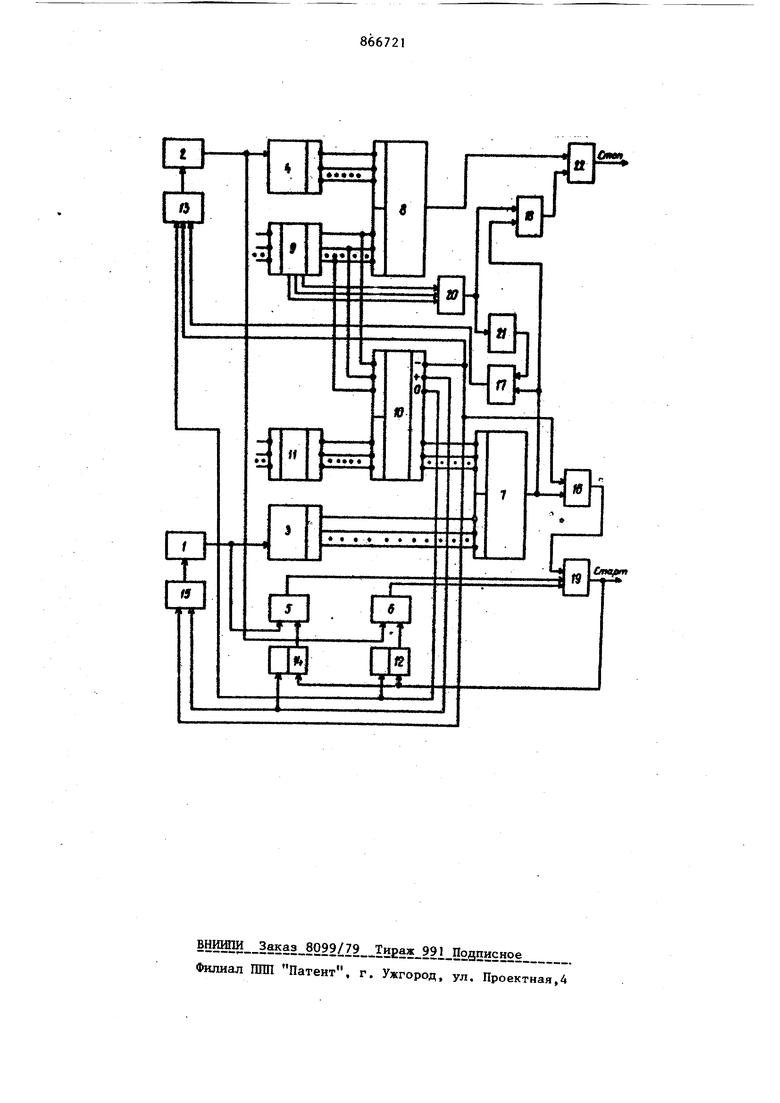

.единицу дискретности и выбираются травными соответственно Т 2 и :1Г 1, где .W - число младших разрядов двоичного представления величины задержки. Для получения искомой задержки в устройстве совмещают начала импульсшлх потоков, суммируют значение кода задержки в И младших разрядах со значением кода в старших разрядах, импульс дополнительного по- тока, монер которого равен значению кода задержки в И младших разрядах вы деляют в качестве начала требуемой задержки, а импульс основного потока номер которого равен значению кода суммы - в качестве конца требуемой задержки fzj. Однако величина сдвига начала рабочей задержки в диапазоне возможных величин задержки колеблется в пределах О - с периодом колебаний 2 , что неприемлемо в случаях, когда, например, частота работы измерителей времени достаточно высока или когда требуется точное совмещение начала счета и начала задержки во временных преобразователях. Целью изобретения является уменьшение сдвига рабочей задержки, Цель достигается тем, что в устройство, содержащее генераторы основ ного и дополнительного импульсных потоков, счетчики импульсов, блоки с падения кодов и регистр кода требуемой задержки, введены блок вычитания кодов, два клапанирукицик триггера, шесть элементов И, три элемента ИЛИ, элемент НЕ, причем единичные выходы младших и старших разрядов регистра кода требуемой задержки соединены со ответственно со входами вычитаемого и уменьшаемого блока вычитания кодов информационные выходы которого соеди нены со вторыми входами блока совпадения кодов основного канала; знаковый выход О блока вычитания кодов подключен к единичному входу первого клапанирующего триггера и через один из входов управляющего элемента ИЛИ дополнительного канала - ко входу генератора импульсов дополнительного пото ка; знаковый выход + блока вычитания кодов соединен с единичным входом второго клапанирующего триггера и через один из входов управляющего элемента ИЛИ основного канала - со входом-Генератора импульсов основного потока; знаковый выход блока вычитания кодов подключен ко входам управляющих элементов ИЛИ и ко входу первого элемента И, другой вход которого соединен с выходом блока совпаде ния кодов основного канала, а выход с одним из входов стартового элемента ИЛИ; выходы генераторов через первые входы соответствукицих клапанир гащих элементов И соединены со входами стар тового элемента ШШ, выход которого подключен кнулевым входам клапанирующих триггеров; выходы триггеров соединены со вторыми входами клапанирующих элементов И; выход блока совпадения кодов основного канала через один из входов второго элемента И подключен ко входу управляющего элемента ИЛИ дополнительного канала и через первый вход третьего элемента И - ко входу стопового элемента ИЛИ, другой вход которого соединен с выходом блока совпадения кодов дополнительного канала/ нулевые выходы младших разрядов регистра требуемой задержки соединены со входами четвертого элемента И, выход которого подключен ко второму входу третьего элемента И и через элемент НЕ - ко второму входу второго элемента И, В предлагаемом устройстве используется основной с периодом to дополнительный с периодом V zVl импульсные потоки, где И - число мпадших разрядов кода требуемой задержки. Уменьшение сдвига задержки достигается за счет вычитания значения кода задержки в г младших разря- , дах из значения кода в старших разрядах и формирования импульсов начала и конца требуемой задержки в зависимости от величины и знака кода разности. На чертеже приведена функциональная схема предлагаемого устройства. Устройство содержит управляемые генераторы I и 2 импульсов основного и дополнительного потоков соответственно с периодами следования импуль2 + I, выходы которых соединены со входами счетчиков импульсов осиовиого 3 и дополнительного 4 импульсных потоков и с первыми входами элементов И 5 и 6 соответственно. Выходы счетчиков 3 и 4 импульсов соединены с первыми входами блоков совпадения кодов основного 7 и дополнительного 8 каналов. Вторые входы блока 8 совпадения кодов подключены к регистру 9 младших разрядов исходного кода, а также к первым входам блока )0 вычитания кодов. Вторые входы блока 10 вычитания кодов соединены с регистром 11 старших разрядов исходного кода, Информационшле выходы блока 10 вычитания кодов соединены со вторыми входами блока 7 совпадения кода. Потенциальный знаковый выход О блока 10 вычигания кодов подключен к единичному входу триггера 12, а также через элемент ИЛИ 13 - к управляющему вхо ду генератора 2, Знаковый выход + блока 10 вычитания кодов подключен к единичному входу триггера 4 и через элемент ИЛИ 15 - к управляюще му входу генератора 1. Выход - блока 10 вычитания кодов через элементы ИЛИ 15 и 13 соединены соответ ственно с управляюпщми входами гене раторов 1 и 2, а также с одним из входов элемента И 16, другой вход которого подключен к выходу блока 7 совпадения кода и ко входам элементов И 17 и 18. Выход элемента И 16 соединен с одним из входов элемента ИЛИ 19, два других входа которого подключены к выходам элементов И 5 и 6. Выход элемента ИЛИ 19 соединен с нулевыми входами триггеров 12 и 14, выходы которых подключены соответственно ко вторым входам элементов И 5 и 6, Входы элемента И 20 соединены с нулевыми выходами регист ра 9 младших разрядов исходного кода, а выход подключен ко второму входу элемента И 8 и через элемент НЕ 21 - ко второму входу элемента И 17, выход которого через элемент ИЛИ 13 соединен с управляющим входом генератора 2. Выход элемента И 18 подключен к одному из входов эле мента ИЛИ 22, другой вход которого соединен с выходом блока 7 совпадения кодов. I Получение временной задержки осу ществляют следующим образом. Исходный код с регистра 9 И мпад- ших разрядов поступает на первые вхо ды блока 8 совпадения кодов и блока 10 вычитания кода, на другие входы которых поступают коды со. счетчика 4 импульсов дополнительного потока и и регистра старших разрядов 11 соответ ственно. Блок 10 вычитания кодов производит операцию вычитания кода : И младших разрядов из старших разрядов и выделяют потенциальный сигнал на одном из знаковых выходов, а также индицирует код разности, поступаювщй на первые входы блока 7 совпадения кодов, на другие входа которого пост пает код из счетчика 3 импульсов основного потока. Если знак кода разности - njsoc и значение кода ;задержки в И младших разрядах равно нулю, то сигнал с выхода + блока 10 вычитания кодов-йа;пускает через элемент ИЛИ 15 гёнера216тор 1 импульсов основного потока, а также переводит триггер 14 в единичное состояние. При этом импульсы основного потока начинают поступать в счетчик 3. Первый импульс основного потока проходит через элемент И 5 и элемент ИЛИ 19 на шину Старт в качестве начала задержки. Импульс с пшны Старт переводит триггер 14 в нулевое состояние, запрещая прохождение последующих импульсов основ-) ного потока через элемент И 5 и элемент ИЛИ 19 на шину Старт. Когда код на счетчике станет равным коду разности плюс единица, сработает блок, совпадения кодов 7. Импульс совпадения поступит через элемент И 18 и элемент ИЛИ 22 на шину Стоп, так как элемент И 18 открыт единичньм потенциалом с элемента И 20, входы которого соединены с нулевыми выходами регистра 9 младших разрядов(если код младших разрядов равен нулю, то на нулевых выходах - все единицы).: Сигнал, выделенный на шине Стоп, устанавливает регистр 9, 11, счетчики 3 и 4 и блок 10 вычитания кодов в нулевое состояние, а также производит срыв колебаний в генераторах 1 и 2 (цепи сброса на чертеже не показаныХЕсли код разности равен Hyjno, то потенциальный сигнал с выхода О блока 10 вычитания кодов запускает через элемент ИЛИ 13 генератор 2 импульсов дополнительного потока, а также переводит триггер 2 в единичное состояние. При этом импульсы дополнительного потока начинают поступать в счетчик 4. Первый импульс дополнительного потока проходит через элемент И 6 и элемент ИЖ 19 - на шину Старт в качестве начала задержки.Импульс с шины Старт переводит триггер 12 в нулевое состояние,запрещая прохождекие последующих импульсов дополнительного потока через элемент И 6 и элемент ИЛИ 19 на шину Старт. Когда код на счетчике 4 станет равным коду задержки в И младших разрядах плюс единица, сработает блок 8 совпадения кодов. Импульс совпадения поступает через элемент ИЛИ 22 на шину Стоп s качестве конца задержки. Если,знак кода разности - минус, то Потенциальный сигнал с выхода - лока 10 вычитания кодов запускает ерез элемент ИЛИ 13 и 15 генераторы 2 и 1 соответственно, а также разре78шает прохождение сигнала блока 7 совпадения кодов через элемент И 16 и элемент ИЛИ 19 на шину Старт.При этом импульсы основного потока поступают в счетчик 3, код которого сравнивается с кодом разности в блоке 7 совпадения кодов; импульсы дополнительного потока поступает в счетчик 4 код которого сравнивается с кодом в П младших разрядах в блоке 8 совпадения. Когда код на счетчике 3 станет равным коду разности плюс единица, сработает блок 7 совпадения кодов-. Импульс совпадения поступит через Элемент И 16 и элемент ИЛИ 19 на шину Старт в качестве начала задерж ки. Когда код на счетчике- 4 станет равным коду задержки в И младших разрядах плюс единица, сработает блок совпадекля кодов 8. Импульс совпадения поступит через элемент ИЛИ 22 на шину Стоп в качестве конца задержки. Если знак кода разности - плюс и значение кода задержки в И мпадпгах разрядах не равно нулю, то на выходе элемента И 20 - нулевой потенциал, а на одном из входов элемента И I7 единичный. Тем самым разрешается прохождение импульса совпадения блока 7 совпадения кодов через второй вход элемента И 17 и элемент ИЛИ }3 на запуск генератора 2 импульсов дополнительного потока. Потенциальный си1- нал с выхода «: блока 10 вычитания кодов запускает через элемент ИЛИ 15 генератор 1 импульсов основного потока а также переводит триггер 14 в единичное состояние. При этом импульсы основного потока начинают поступать в счетчик 3. Первый импульс основного потока проходит через элемент И 5 и элемент ИЛИ 19 на шину Старт в качестве сиг нала задержки. Импульс с шины Старт переводит триггер 14 в нулевое состоя ние, запрещая прохождение последукяцих импульсов основного потока через элемент И 5 и элемент ИЛИ 19. Когда код на счетчике 3 станет равным коду разности плюс единица, сработает блок 7 совпадения кодов. Импульс совпадения запускает через элемент И 17 и элемент ИЛИ 13 генератор 2 импульсов дополнительного потока, которые посту пают в счетчик 4, Когда код на счетчи ке 4 станет равным коду задержки в Л младших разрядах плюс единица,сработае блок 8 совпадения кодов и импульс сов1элемент ИЛИ 22 адения поступит через на шину Стоп. Величина сдвига начала рабочей задержки в предлагаемом устройстве для большинства величин задержки равна нулю, Формула изобретения Устройство квантованной временной задержки импульсных сигналов, содержащее управляемые генераторы и счетчики импульсов основного и дополнительного импульсных потоков, блоки совпадения кодов, первые входы которых соединены с выходами счетчиков, регистр кода требуемой задержки, младшие разряды -которого подключены ко вторым входам блока совпадения кодов дополнительного канала, отличающеес я тем, что, с целью уменьшения сдвига рабочей задержки, в него введены два клапанирующих триггера, шесть элементов И, три элемента ИЛИ и элемент НЕ, причем единичные выходы младших и старших разрядов регистра кода требуемой задержки соединены соответственно со входами вычитаемого и уменьшаемого блока вычитания кодов, информационные выходы которого соединены со .вторыми входами блока совпадения кодов основного канала знаковый выход О блока вычитания кодов подключен к единичному входу первого клапанирующего триггера и через один из входов управляющего элемента ИЛИ дополнительного канала - ко входу генератора импульсов дополнительного потока, знаковый выход + блока вычитания кодов соединен с единичным входом второго клапанирукяцего триггера и через один из входов управляющего элемента ИЛИ основного канала - с входом генератора импульсов основного потока, знаковый выход - блока вычитания кодов подключен ко входам управляющих элементов ИЖ и ко входу первого элемента И, другой вход которого соединен с выходом блока совпадеття кодов основного канала, а выход - с одним из входов стартового элемента ШЩ, выходы генераторов через первые входы соответствуюпдах клапанирующих элементов И соединены со входаьш стартового элемента ИЛИ, выход которого подключен к нулевым входам клапанируюощх триггеров, выходы триггеров соединены со вторыми входами клапанируклцих элементов И, выход блока совпадения кодов основного канала через один из входов второго элемента И подключен ко входу управляющего элемента ИЛИ дополнительного канала и через первый вход третьего элемента R - ко входу стопового элемента ИЛИ, другой вход которого соединен с выходом блока совпадения кодов дополнительного канала, . нулевые выходы младших разрядов регистра требуемой задержки соединешл со входами четвертого элемента И, которого подключен ко второму

входу третьего элемента И и через элемент НЕ - ко второму вхдду в1горого элемента И,

Источники информации,

принятые во внимание при экспертизе

, 2. Валсенина 3. П. и др. Методы и схемы временной задержки импульсных сигналов М., Советское радио, 1971, с. 199-203 .(прототип).

Авторы

Даты

1981-09-23—Публикация

1979-12-12—Подача