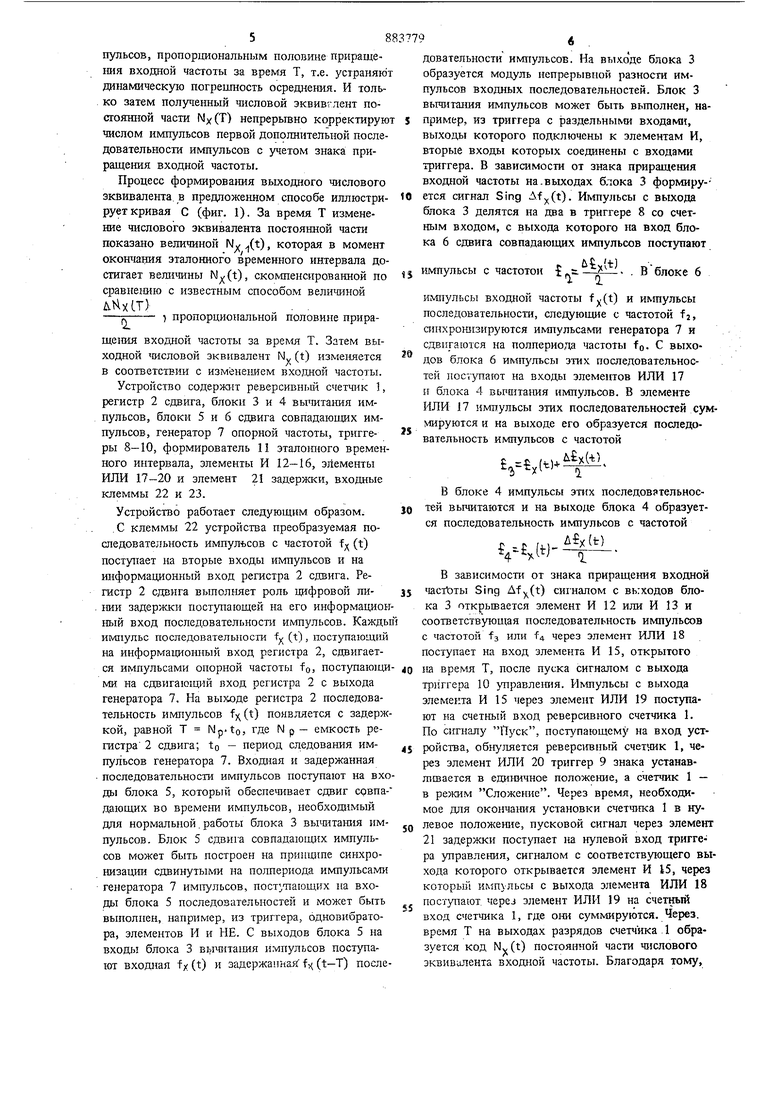

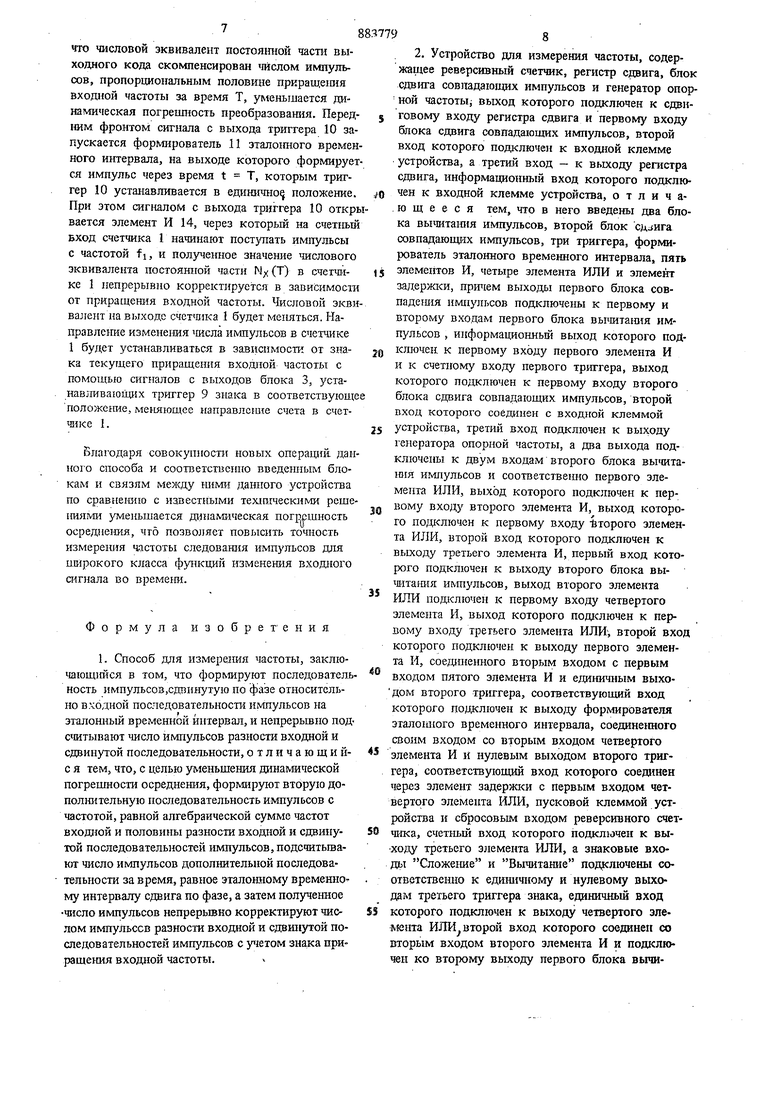

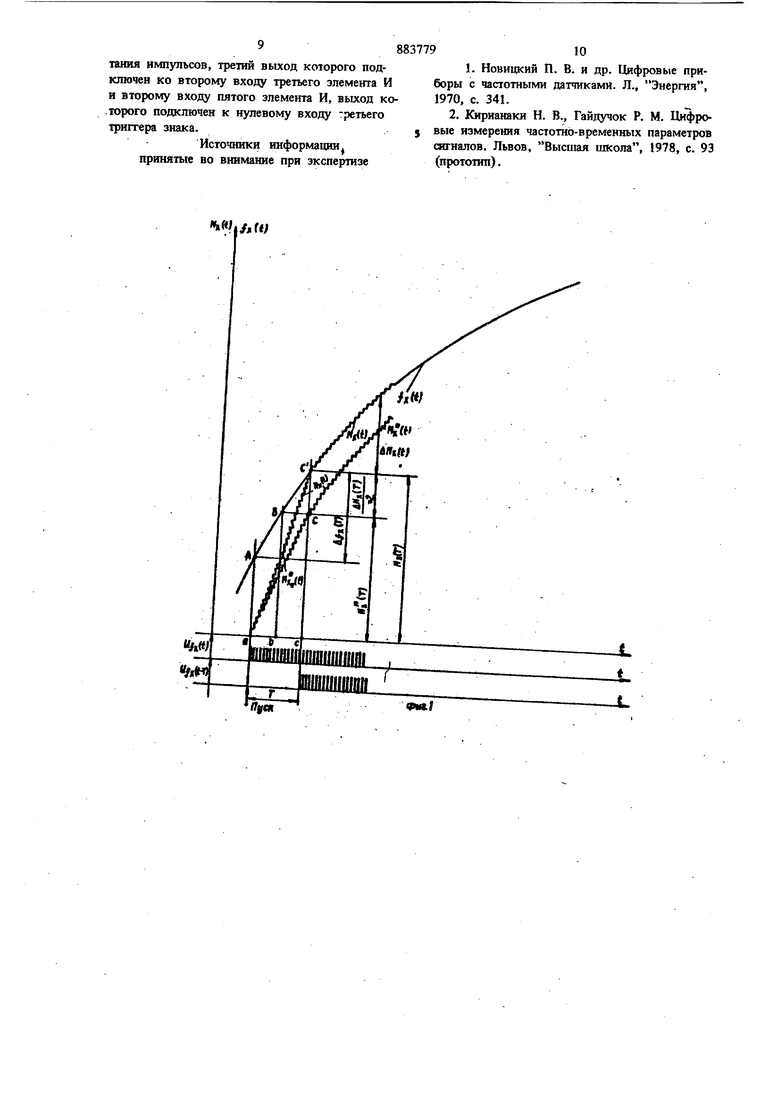

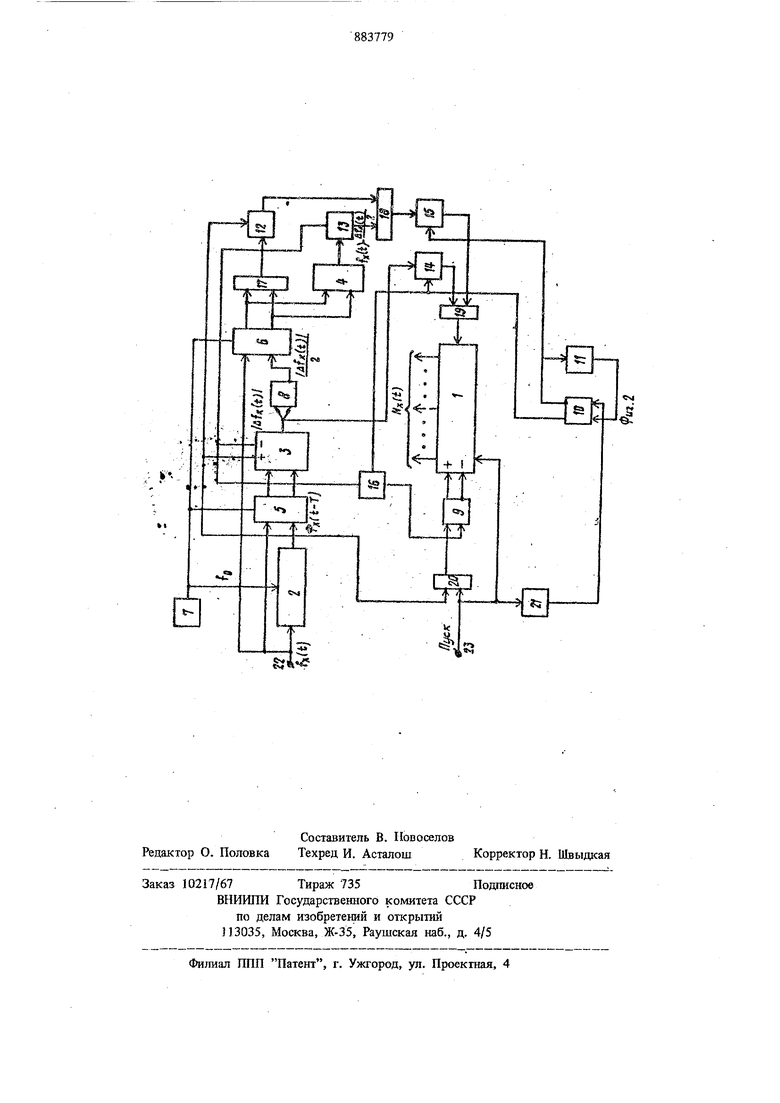

интервал, и в непрерывном подсчете числа илшульсов разности входной и сдвшгутой последовательностей, формируют вторую дополнительную последовательность импульсов с частотой, равной алгебраической сумме частот входной и половине разности входной и сдвинзтой последовательностей импульсов, подсчитывают число импульсов допол1штельной последовательности импульсов за время, равное эталонному сдвигу по фазе, а затем полугенное число импульсов нецрерьюно корректируют числом импульсов разности входной и сдвинутой последовательностей импульсов с знака приращешм входной частоты. I Поставленная цель достигается также тем, ,что в устройство для измереютя частотЫ) со. держащее реверсивный счетшк, регистр сдвига блок сдвига совпадающих импульсов и генератор опорной частоты, вьисод которого подключен к сдвиговому входу регистра СДВИГЕГ и первому входу блока сдвига совпадающих имг ульсов, второй вход которого подключен к ВХОД5ЮЙ клемме устройства, а третий вход к выходу регистра сдвига, информационный вход которого подключен к входной клемме устройства, введены два блока вычита1шя импуль сов, второй блок сдвига совпадающих импульсов, три триггера, формирователь эталоштого временного интервала, пять элементов И, четыре элемента ИЛИ и элемент задержки, причем вьь ходы первого блока совпадеш-ш импул)сов под ключены к первому И второму входам первого блока вышгания импульсов, информационный выход которого под1слючен к первому входу первого элемента И и к счетному.входу первого триггера, выход которого подключен к первому входу второго блока сдвига совпадающих импульсов, второй вход которого соедршен с входной клеммой устройства, третий вход подключен к генератора опорной частоты, а два выхода подключены к двум входам втор го блока вычиташ я импульсов и соответственно первого элемента ИЛИ, выход которого подклю чен к первому входу второго элемента И, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого под ключен к выходу третьего элемента И, первьш вход которого подк:лючен к выходу второго блока вычитания импульсов, выход второго эле мента ИЛИ подключен к первому входу четвер того элемента И, выход которого пощслючен к первому входу третьего элемента ИЛИ, второй вход KOTopoiO подключен к выходу первого элемента И, соединенного вторым входом с первым входом пятого элемента И и едиричlaiM выходом второго триггера, соответствующий вход которого подключен к выходу фор мировате1 я эталонного временного интервала, соединенного своим входом со вторым входом четвертого элемента И и нулевым выходом вто рого триггера, соответствуюпдий вход которого соединен через элемент задержки с первым входом четвертого элемента ИЛИ, пусковой клеммой устройства и сбросовым входом реверсивного счетчика, счетный вход которого подключен к выходу третьего элемента ИЛИ, а знаковые входы Сложение и Вычитание подключены соответственно к единишсму и нулевому выходам третьего триггера знака, единичный вход которого подключен к выходу четвертого элемента ИЛИ, второй вход которого соединен со вторым входом второго элемента И и подключен ко второму выходу первого блока вычитатшя импульсов, третий выход которого подК7почен ко второму входу третьего элемента И и второму входу пятого элемента И, выход которого подключен к нулевому входу третьего триггера знака. На фиг. 1 изображен временной график, поясняющий способ для измерешет частоты; .на фиг. 2 - блок-схема устройства, реализующего этот способ. Сущность способа .заключается в следующем. Получают пос71едовательность импульсов с частотой fj (t-Т), сдвинутую по фазе на величину ( Т эталонного интервала времени относительно входной последовательности импульсов с частотой f j( (t). После пуска в течешге времени Т имеется только входная последовательность импульсов f)((t). Через время Т формируется вторая последовательность импульсов f(t-Т), сдвинутая по фазе на велищ ну Т относительно входной. Для компенсации динамической погрешности осреднения в предлагаемом способе сначала формируют последовательность импульсов с частотой%, AfxW fxW -fxCt-O, равной текущему прираще1шю.истоты входной последовательности импульсов относительно сдвинутой. Затем фop fflpyют дополнительную последовательность импульсов с частотой f л (4.+.(t) , Ail )( равной алгебраической сумме входной частоты и половипы разности входной и сдвинутой последовательностей импульсов. Подсчитьшают число импульсов второй допол1штельной после. довательности за время эталонного временного интервала Т, за который обра.зуется шсловой эквивалент постояшюй части выходного кода N,(T) (i)±-i|Wjjat T(t) ...И) Как , числовой эквивалент постояшюй 4acTii выходного кода компенсируют числом импульсов, пропорциональным половине приращения входной частоты за время Т, т.е. устраняю динамическую погрешность осредаения. И только затем получе1шый числовой эквивглент постоянной части NX (Т) непрерьгено корректирую числом импульсов первой дополнительной последовательности импульсов с учетом знака приращения входной частоты. Процесс формирования выходного числового эквивалента в предложенном способе иллюстрирует кривая С (фиг. 1). За время Т изменение числового эквивалента постоянной части показано величиной N (t), которая в момент окончания эталонного временного интервала достигает величины N(t), скомпенсированной по сравнению с известным способом величиной uHxlT). . -jT) пропорциональной половине приращения входной частоты за врел-ш Т. Затем выходной числовой эквивалент N., (t) изменяется в соответствии с изменением входной частоты. Устройство содержит реверсивньш счетчик 1, регистр 2 сдвига, блоки 3 и 4 вычита1шя импульсов, блоки 5 и б сдвига совпадающих импульсов, генератор 7 опорной частоты, триггеры 8-10, формирователь 11 эталогаюго временного интервала, элементы И 12-16, элементы ИЛИ 17-20 и элемент 21 задеряжи, входные клеммы 22 и 23. Устройство работает следующим образом. .С клеммы 22 устройства преобразуемая последовательность импульсов с частотой f (t) поступает на вторые входы импульсов и на информационный вход регистра 2 сдвига. Регистр 2 сдвига выполняет роль цифровой линии задержки поступающей на его информацион ный вход последовательности импульсов. Каждь импульс последовательносш f (t), поступающш на информациощ1ый вход регистра 2, сдвигается импульсами опорной частоты fo, поступающи ми на сдвигаю1ций вход регистра 2 с выхода генератора 7. На выходе регистра 2 последовательность импульсов f (t) появляется с задержкой, равной Т Np. to, где N р - емкость регистра 2 сдвига; to - период следования импульсов генератора 7. Входная и задержанная последовательности импульсов поступают на вхо ды блока 5, который обеспечивает сдвиг совпадающих во времени импульсов, необход51мый для нормальной. работы блока 3 вьрштания импульсов. Блок 5 сдвига совпадаюиц1х импульсов может быть построен на принципе синхронизации сдвинутыми на полпериода импульсами генератора 7 импульсов, посг -пающих на входы блока 5 последовательностей и может быть вьщолнен, например, из триггера, одновибратора, элементов И и НЕ. С выходов блока 5 на блока 3 вь14 1та1шя импульсов поступают входная fX (t) и задержанная fx (t-T) последовательности импульсов. На выходе блока 3 образуется модуль непрерывной разности импульсов входных последовательностей. Блок 3 вычитшшя импульсов может быть вьшолнен, например, из триггера с раздельными входагл, выходы которого подключены к элементам И, вторые входы которых соединены с входами триггера. В зависимости от знака приращения входной частоты на.выходах блока 3 формиру-ется сигнал Sing Af.(t). Импульсы с выхода блока 3 делятся на два в триггере 8 со счетным входом, с выхода которого на вход блока 6 сдвига совпадающих импульсов поступают импульсы с частотой . t. У . В блоке 6 импульсы входной частоты f)((t) и импульсы последовательности, следующие с частотой fj, срп1хронизируются импульсами генератора 7 и сдвигаются на полпериода частоты fo. С выходов блока 6 импульсы этих последовательностей поступают на входы элементов ИЛИ 17 и блока 4 вышта1шя импульсов. В элементе ИЛИ 17 импульсы этих последовательностей суммируются и на выходе его образуется последовательность импульсов с частотой V,(t).« в блоке 4 импульсы этих последовательностей вьпштаются и на выходе блока 4 образуется последовательность импульсов с частотой (t) В зависимости от знака приращения входной часТЬты Sing Af(t) сигналом с выходов блока 3 открьтается элемент И 12 или И 13 и соответствующая последовательность импульсов с частотой fa или f4 через элемент ИЛИ 18 поступает на вход элемента И 15, открытого па время Т, после пуска сигналом с выхода Триггера 10 зтггравления. Илтульсы с выхода элемента И 15 через элемент ИЛИ 19 поступают на счетный вход реверсивного счетчика 1. По сигналу Пуск, поступающему на вход устройства, обн ляется реверС1геный счетдак 1, через элемент ИЛИ 20 триггер 9 знака устанавшшается в единичное положение, а счетчик 1 - в режим Сложение. Через время, необходимое для окончага я установки счетчика 1 в нулевое положение, пусковой сигнал через элемент 21 задержки nocTjTiaeT на нулевой вход триггера управления, сигналом с соответствующего выхода которого открывается элемент И 15, через который импульсы с выхода элемента ИЛИ 18 поступают через элемент ИЛИ 19 на счетный вход счетчика 1, где они суммируются. Через, время Т на выходах разрядов счетчика 1 образуется код Nv(t) постоянной части числового эквивалента входной частоты. Благодаря тому. что числовой эквивалент постая1шой части выходного кода ско1ипенсироваи числом импульсов, пропорцио1гальным половине пркращелия входной частоты за время Т, уменьшается динамическая погрешность прео6разоваш1я. Передним фронтом сигнала с выхода триггера 10 запускается формирователь 11 эталонного времен ного ит-ервала, на выходе которого формирует ся импульс через время t Т, которым триггер 10 устанавливается в единично положение. При этом сигналом с выхода триггера 10 откр вается элемент И 14, через который на счетньга вход счетчика 1 начинают поступать импульсы с частотой fi, и полученное значение числового эквивалента постоянной части NX (Т) в счетш ке 1 непрерывно корректируется в зависимое™ от приращения входной частоты. %словой экви валентна выходе счетчика 1 будет меняться. Направле1ше изменения вдела импульсов в счетчике 1 будет усганавливаться в зависимости от знака текущего нриращения входной частоты с помощью сигналов с выходов блока 3, устанавливаюйдах триггер 9 знака в соответствующе положсште, меняющее направлсшю счета в счетчике 1. Благодаря совокупности новых операций дан ного способа и соответственно введешгым блокам и связям мелоду ними данного устройства но сравнегшю с известными тех1шческнми реше 1шями уменьшается Д1«1а шческая погрешность осреднения, что нозволяет повысить точность измерештя частоты следования импульсов для широкого класса функций изменения входного шгнала во времени. Формула изобретения 1. Способ для измерения частоты, заключающийся в том, что форлшруют последователь ность импульсоз,сдпннутую по фазе относительно входной последовательности импульсов на эталонный временной интервал, и непрерьшно подСмтьн1ают число имнульсов разности входной и сдвинутой носледовательности, отличающийс я тем, что, с целью уменьшения дина шческой погреншосга осреднения, формируют вторую дополнительную последовательность импульсов с частотой, равной алгебраической сумме частот входлой и половины разности входной и сдвинутой последовательностей импульсов, подсчитьгаают число импульсов дополнительной последовательности за время, равное эталошюму временному интервалу сдвига по фазе, а затем полученное число и myльcoв непрерьшно корректируют числом импульссв разности входной и сдвинутой последовательностей импульсов с уктом знака прираще}шя вход1юй частоты. 8 2, Устройство для измерения частоты, содержаидее реверсивный счетчик, регистр сдвига, блок сдвига совпадающих имнульсов и генератор опорной частоты; выход которого подключен к сдвнговому входу регистра сдвига и первому входу блока сдвига совпадающих импульсов, второй вход которого подключен к входной клемме устройства, а третий вход - к выходу регастра сдвига, информационный вход которого подключей к входной клемме устройства, о т л и ч аю щ е е с я тем, что в него введены два блока вьпшта1шя импульсов, второй блок сдвига совнадающих импульсов, три триггера, форми рователь эталонного временного интервала, пять элементов И, четыре элемента ИЛИ и элемент задержки, пршюм выходы первого блока совпадешм имнульсов нодключены к первому и второму входам лервого блока вьршташ1я импульсов , информационньв выход которого поДключен к нервому входу лервого элемента И и к счетному входу нервого тркггера, выход которого нодключен к первому входу второго блока сдвига совнадающих импульсов, второй вход которого соединен с входной клеммой устройства, третий вход под1слючен к выходу генератора опорной частоты, а два выхода нодключены к двум входам второго блока вычита шя имнульсов и соответственно нервого элемента ИЛИ, выход которого нодключен к нервому входу второго элемента И, выход которого подключен к нервому входу iJTOporo элемента ИЛИ, второй вход которого подключен к выходу третьего элемента И, первый вход которого подключен к выходу второго блока вычиташ1я имнульсов, выход второго элемента ИЛИ подключен к первому входу четвертого элемента И, выход которого пощслючен к первому входу третьего элемента ИЛИ, второй вход которого подключен к выходу нервого элемента И, соедашенного вторым входом с первым входом пятого элемента И и еда1шчным выходом второго триггера, соответствующий вход которого подключен к выходу формирователя эталонного временного интервала, соедине1шого своим входом со вторым входом четвертого элемента И и нулевым выходом второго триггера, соответствующий вход которого соединен через элемент задержки с первым входом четвертого элемента ИЛИ, пусковой клеммой устройства и сбросовым входом реверсивного счетчика, счетгшш вход которого подключен к выходу третьего элемента ИЛИ, а знаковые входы Сложе1ше и Вычитание подалючены соответственно к еди шчному и нулевому выходам третьего триггера знака, единичный вход которого подключен к выходу четвертого элемента ИЛИ второй вход которого соединен со вторым входом второго элемента И и подключен ко второму выходу первого блока вычитания импульсов, третий выход которого подключей ко второму входу третьего элемента И и второму входу пятого элемента И, выход ко.торого подключен к нулевому входу третьего триггера знака.

Источники информации принятые во внимание при экспертизе

1. Новицкий П. В. и др. Цифровые приборы с частотными датчиками. Л., Энергия, 1970, с. 341.

2, Кирнанаки Н. В., Гайдучок Р. М. Цифровые измерения частотно-временных параметров сигналов. Львов, Высшая илсола, 1978, с. 93 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU875622A1 |

| Адаптивный аналого-цифровой преобразователь | 1979 |

|

SU864552A1 |

| Адаптивный аналого-цифровой преобразователь | 1979 |

|

SU866734A1 |

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU942257A1 |

| Адаптивный аналого-цифровой преобразователь | 1983 |

|

SU1109899A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1084852A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1037313A1 |

| Преобразователь цифрового кода в частоту следования импульсов | 1976 |

|

SU738158A1 |

| Цифровой компенсатор | 1972 |

|

SU439915A1 |

| Адаптивный аналого-цифровой преобразователь | 1982 |

|

SU1051703A1 |

Авторы

Даты

1981-11-23—Публикация

1980-02-01—Подача