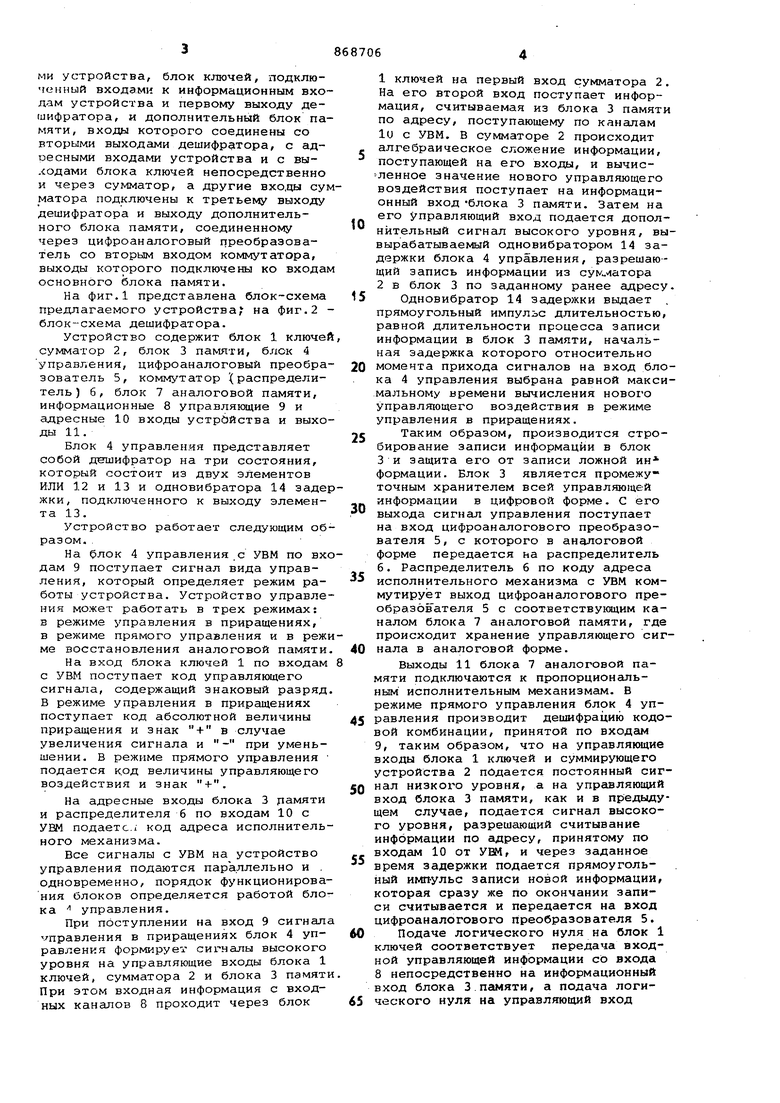

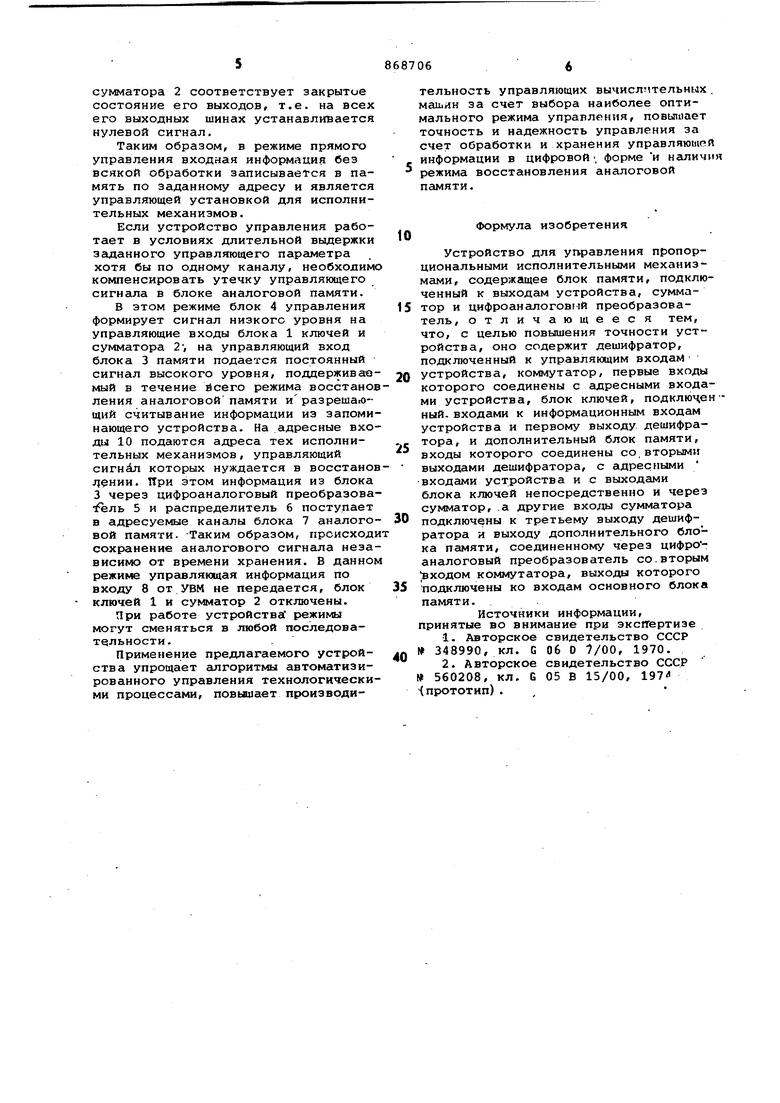

(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОПОРЦИОНАЛЬНЫМИ ИСПОЛНИТЕЛЬНЫМИ МЕХАНИЗМАМИ Изобретение относится к автоматике, и вычислительной технике и предназначено для использования в системах управления технологическими процессами с помощью управляющих вычислительных машин. Известно устройство для управлени пропорциональными исполнительными ме ханизмами, выполненное в виде цифроаналогового преобразователя, выход которого через блок памяти соединен с выходными каналами устройства t4 Однако известное устройство не об ладает достаточной точностью, так как может работать -только при формировании управляющих воздействий в приращениях, а также имеет одну лишь аналоговую , информация в кото рой подвержена утечке. Наиболее близким ,к предлагаемому является устройство для управления пропорциональными исполнительными механизмами, содержащее цифроаналого вый преобразователь, блок суммирован и блок аналоговой памяти, выходы которого являются выходными каналами устройства 2. (Указанное устройство также реализует управление пропорциональными исполнительными механизмами только в приращениях и не может обеспечить прямого регулирования, что снижает его точность (сужает область его при|июнения). Известное устройство. содержит цифроаналоговый преобоазователь на вход, при этом суммирование или вычитание сигнала и его хранение, в памяти осуществляется в аналоговой форме, что неизбежно вносит накапливгиощуюся ошибку управления. Взаимодействие известного устройства с УВМ несколько усложнено, так как необходимо сначала задать адрес исполнительного механизма на блок задания адреса, а после обработки сигнала необходимо такой же адрес задать в блок аналоговой памяти. Цель изобретения - повышение точности устройства и,расширение области применения. Поставленная цель достигается гем, что в устройство для управления пропорциональными исполнительньлхш механизмами, содержащее блок памяти, подключенный к выходам устройства, сумматор, и цифроаналоговый преобразователь, введены дешифратор, подключенный к управляющим входам устройства, коммутатор, первые входы которого соединены с адресными входами устройства, блок ключей, подключенный входами к информационным вхо дам устройства и первому выходу дешифратора, и дополнительный блок па мяти, входы которого соединены со вторыми выходами дешифратора, с адресными входами устройства и с выходами блока ключей непосредственно и через сумматор, а другие вхо.цы су матора подключены к третьему выходу дешифратора и выходу дополнительного блока памяти, соединенному через цифроаналоговый преобразователь со вторым входом коммутатора, выходы которого подключены ко входа основного блока памяти. На фиг.1 представлена блок-схема предлагаемого устройства; на фиг. 2 блок-схема дешифратора. Устройство содержит блок 1 ключе сумматор 2, блок 3 памяти, блок 4 управления, цифроаналоговый преобра зователь 5, коммутатор распределитель ) 6, блок 7 аналоговой памяти, информационные 8 управлякмдие 9 и адресные 10 входы устройства и выхо ды 11. Блок 4 управления представляет собой дешифратор на три состояния, который состоит из двух элементов ИЛИ 12 и 13 и одновибратора 14 заде жки, подключенного к выходу элемента 13. Устройство работает следующим об разом. . На блок 4 управления с УВМ по вх дам 9 поступает сигнал вида управления, который определяет режим работы устройства. Устройство управле ния может работать в трех режимах: в режиме управления в приращениях, в режиме прямого управления и в реж ме восстановления аналоговой памяти На вход блока ключей 1 по входам с УВМ поступает код управляющего сигнала, содержащий знаковый разряд В режиме управления в приращениях поступает код абсолютной величины приращения и знак + в случае увеличения сигнала и - при уменьшении. В режиме прямого управления подается к.од величины управляющего воздействия и знак +. На адресные входы блока 3 памяти и распределителя 6 по входам 10 с УВМ подаете.; код адреса исполнитель ного механизма. Все сигналы с УВМ на устройство управления подаются параллельно и . одновременно, порядок функционирова ния блоков определяется работой бло ка управления. При поступлении на вход 9 сигнал vпpaвлeния в приращениях блок 4 управления формирует сигналы высокого уровня на управляющие входы блока 1 ключей, сумматора 2 и блока 3 памят При этом входная информация с входных каналов 8 проходит через блок 1ключей на первый вход сумматора 2. На его второй вход поступает информация, считываемая из блока 3 памяти по адресу, поступающему по каналам 1и с УВМ, В сумматоре 2 происходит алгебраическое сложение информации, поступающей на его входы, и вычисленное значение нового управляющего воздействия поступает на информационный вход -блока 3 памяти. Затем на его управляющий вход подается дополнительный сигнал высокого уровня, вывырабатываемый одновибратором 14 задержки блока 4 управления, разрешающий запись информации из су - атора 2в блок 3 по заданному ранее адресу. Одновибратор 14 задержки выдает , прямоугольный импульс длительностью, равной длительности процесса записи информации в блок 3 памяти, начальная задержка которого относительно момента прихода сигналов на вход блока 4 управления выбрана равной максимальному времени вычисления нового управляющего воздействия в режиме управления в приращениях. Таким образом, производится стробирование записи информации в блок 3и защита его от записи ложной ин формации. Блок 3 является промежу точным хранителем всей управляющей информации в цифровой форме. С его выхода сигнал управления поступает на вход цифроаналогового преобразователя 5, с которого в аналоговой форме передается на распределитель 6. Распределитель 6 по коду адреса исполнительного механизма с УВМ коммутирует выход цифроаналогового преобразователя 5 с соответствукицим каналом блока 7 аналоговой памяти, где происходит хранение управляющего сигнала в аналоговой форме. Выходы 11 блока 7 аналоговой памяти подключаются к пропорциональным исполнительным механизмам. В режиме прямого управления блок 4 управления производит дешифрацию кодовой комбинации, принятой по входам 9, таким образом, что на управляющие входы блока 1 ключей и суммирующего устройства 2 подается постоянный сигнал низкох о уровня, а на управляющий вход блока 3 памяти, как и в предыдущем случае, подается сигнал высокого уровня, разрешающий считывание информации по адресу, принятому по входам 10 от УВМ, и через заданное время задержки подается прямоугольный импульс записи новой информации, которая сразу же по окончании записи считывается и передается на вход цифроаналогового преобразователя 5. Подаче логического нуля на блок 1 ключей соответствует передача входной управляющей информации со входа 8 непосредственно на информационный вход блока 3.памяти, а подача логического нуля на управляющий вход сумматора 2 соответствует закрытое состояние его выходов, т.е. на всех его выходных шинах устанавливается нулевой сигнал. Таким образом, в режиме прямого управления входная информация без всякой обработки записывается в память по заданному адресу и является управляющей установкой для исполнительных механизмов. Если устройство управления работает в условиях длительной выдержки заданного управляющего параметра хотя бы по одному каналу, необходим компенсировать утечку управляющего сигнала в блоке аналоговой памяти. В этом режиме блок 4 управления формирует сигнал низкого уровня на управляющие входы блока 1 ключей и сумматора 2, на управляющий вход блока 3 памяти подается постоянный сигнал высокого уровня, поддерживае мый в течение йсего режима восстанов ления аналоговой памяти иразрешающий считывание информации из запоминающего устройства. На .адресные вхо ды 10 подаются адреса тех исполнительных механизмов, управляющий сигнёл которых нуждается в восстанов . При этом информация из блока 3 через цифроаналоговый преобразова 5 и распределитель 6 поступает в адресуемые каналы блока 7 аналоговой памяти. Таким образом, происходи сохранение аналогового сигнала независимо от времени хранения. В данном режиме упрэизляющая информация по входу 8 от УЕМ не передается, блок ключей 1 и сумматор 2 отключены. При работе устройства режимы могут сменяться в любой последовательности. Применение предлагаемого устройства упрощает алгоритмы автоматизированного управления технологическими процессами, повьилает производительность управляющих вычислительных, машин за счет выбора наиболее оптимального режима управления, повышает точность и надежность управления за счет обработки и хранения управляющей информации в цифровой , форме и наличия режима восстановления аналоговой Пс1МЯТИ. Формула изобретения Устройство для управления пропорциональными исполнительными механизмами, содержащее блок памяти, подключенный к выходам устройства, сумматор и цифроаналоговый преобразователь, отличающееся тем, что, с целью повышения точности устройства, оно содержит дешифратор, подключенный к управляющим входам устройства, коммутатор, первые входы которого соединены с ащресными входами устройства, блок ключей, подключен ный. входами к информационным входам устройства и первому выходу, дешифратора, и дополнительный блок памяти, входы которого соединены со.вторыми выходами дешифратора, с адресными входами устройства и с выходами блока ключей непосредственно и через сумматор, .а другие входил сумматора подключены к третьему выходу дешифратора и выходу дополнительного блока памяти, соединенному через цифроаналоговый преобразователь со.вторым уходом коммутатора, выходы которого -подключены ко входам основного блока памяти. Источники информации, ринятые во внимание при экспертизе 1.Авторское свидетельство СССР 348990, кл. G Об О 7/00, 1970. 2.Авторское свидетельство СССР 560208, кл. G 05 В 15/00, 197 прототип).

иг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля параметров | 1990 |

|

SU1800447A1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| Устройство для вывода информации на экран электронно-лучевой трубки | 1977 |

|

SU1029177A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Программируемый генератор импульсов | 1984 |

|

SU1248029A1 |

| Устройство для формирования базисно-тригонометрических функций | 1990 |

|

SU1792542A3 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

П

(иг.г

Авторы

Даты

1981-09-30—Публикация

1980-01-22—Подача