( 54) ГЕНЕРАТОР ПВСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных чисел | 1980 |

|

SU883901A2 |

| Генератор псевдослучайных чисел | 1981 |

|

SU966693A1 |

| Генератор псевдослучайных двоичных чисел | 1978 |

|

SU781797A2 |

| Генератор псевдослучайных кодов | 1983 |

|

SU1167710A1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ ИМПУЛЬСОВ НА ОДНОРОДНОЙ СРЕДЕ С ПРОГРАММНО МЕНЯЮЩЕЙСЯ СТРУКТУРОЙ | 2005 |

|

RU2331915C2 |

| Генератор псевдослучайной последовательности | 1985 |

|

SU1305837A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1996 |

|

RU2120136C1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

| Псевдослучайный преобразователь | 1973 |

|

SU437062A1 |

| Генератор псевдослучайных сигналов | 1986 |

|

SU1347166A1 |

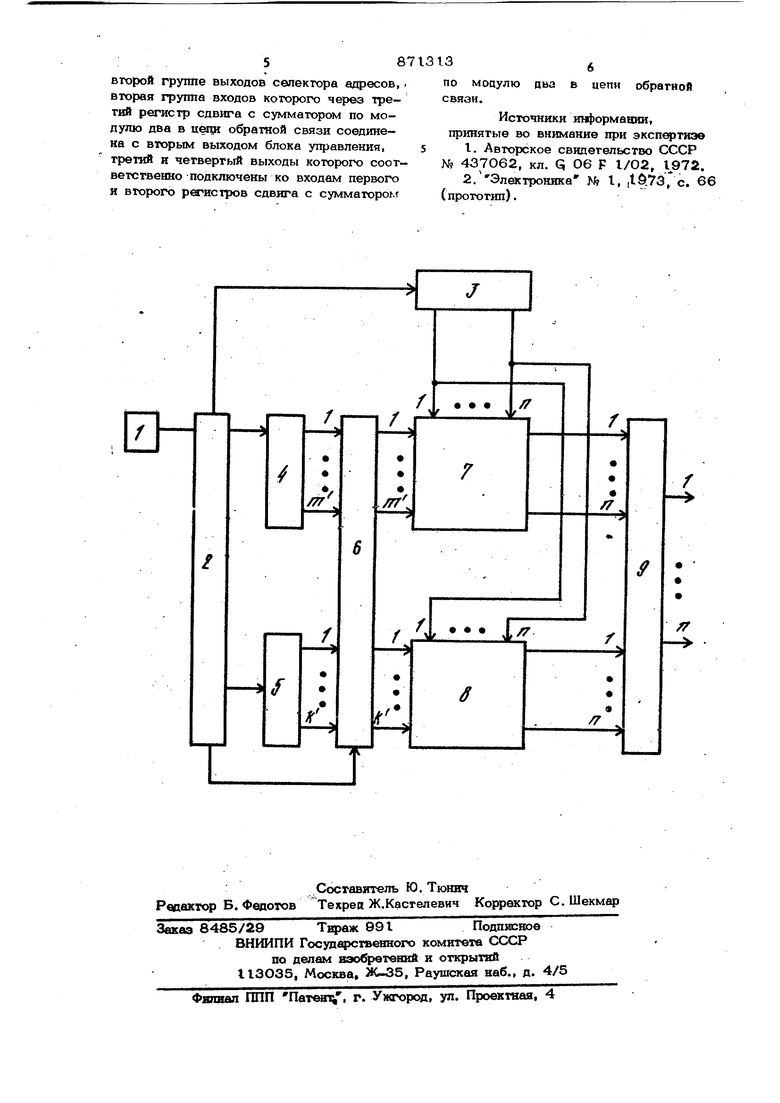

; Иэобретз{ие относится к импульсной технике, может быть использовано в кодщ уюпшх устройствах линий связи, где требуется высокая криптографическая стой кость сообщений. Известно устройство Tl 3, содержащее коммутатор, блок сумматоров по модулю два, регистр - преобразователь, входной регистр, г сератор тактовых импульсов, генератор пачки импульсов, блок сравие ния кодов, одиночно го импульса, счетчик числа иалож шй и блок регш;трации наложений. Недостатком данного устройства являе ся отсутствие равномерности распределения псевдослучайных чисел на выходе, что является необходимым- условием высокой криптографической стойкости. Известно устройство . содержащее генератор тактовых импульсов, запоминаю щее устройство, ин юрмаоионныевходы, ко торого подключены к выходам регистра сдвига с сумматор по модулю два в цепи о }атной связи, адресные входы ч&рез селектор адресов соединены с управ;ляющим генератором и вторым ретт1строМ сдвига с сукшатором по модулю два в цепи офатной связи, соединенным с выходом третьего регистра сдвига; управляющий генератор соединен через генератор тактовых импульсов со сходом первого регистра сдвига. Недостатком данного устройства является низкое быстродействие 1фи необха димости получения на его выхюде п - раэ р:шных двоичных чисел. У величине быстродействия за счет одновременного считывания из ОЗУ по п адресем приведет к потере .криптографической стойкости, поскольку в этом случае количество различных псевдослуч ных двоичных чисел на выходе генератора будет ох аничено объемом ОЗУ. Целью настояшехч) изобретения является 1ювышение &1к:тродействия генератора. Поставленная пель достигается тем, что в генератор 1юевдос;1учайных последовательност, содержащий генератор тактовых импульсов, выход которого соединен со входом блока управления, первый выход когорого подключен к управляющему входу свпекгора адресов, группа входов которого соединена с выходами первого регистра сдвига с сумматором по модулю два в цепи обратной связи, запоминающее устройство, информационные входы которого соединены с выходами второго регистра сдвига с сумматором по модулю два в цепи обратной связи, а адресные входы соединены с первой группой выходов селектора адресов, третий регистр сдвига с сумматором по модулю два в цепи обратной связи, в него дополнительно введены запоминающее устройст во и п - разрядный сумматор по модулю два, входы которого соединены с выходами оапоминающих устройств, причем информационные и адресные входы дополнительного запоминающего устройства под- . ключены соо1:ветственно к выходам второго регистра сдвига с сук матором по модулю два в цепи обратной связи и ко второй группе выходов селектора адресов вторая группа входов которого, через третий регистр сдвига с сумматорами по мо дулю два в цепи обратной связи соединена со вторым выходом блока управлени третий и четвертый выходы которого соо ветственно подключены ко входам Йервого и второгхэ регистров сдвига с сумматором по модулю два в цепи обратной связи. На чертеже приведена футпсщюнальная схема генератора. Генератор псевдослучайных последовательностей содернсит генератор I тактовы импульсов, блок 2 управления, регистры 3-5 сдвига с сумматором по модулю два в цепи обратной связи селектор 6 адресов, запоминающее устройство 7, 8, ц разрядный сумматор 9 по модулю два. Регистры 3-5 обеспечивают получение максимально длинной М -последовательности. Работает генератор следующим образом. В Исходном состоянии в регистры 3-5 занесены ключевые слова. Работа генератора начинается с режима записи. Под действием тактовых импульсов генератора I, проходящих через блок 2 управлени на входы сдвига регистров 3 и 4, в каждом такте работ происходит изменение содержимого регистра 3, которое записывается по адресу, соответствующему состоянию регистра 4, в запомннаюпгее устройство 7. До заполнения всех адресов запоминающего устройства адресные ВХОДЫ запоминающего устройства. 8 зарыты с помощью селектора 6 адресов игналом с блока 2 управления, и запись в запоминающечэ устройство 8 не происходит. По заполнении всех адресов запоминающего устройства 7 блок 2 управления режимами с помощью селектора 6 адресов запрет1ает запись в запоминакшее устройство 7 и разрешает запись в запоминающее устройство 8 по адресам, поступающим через селектор 6 адресов о регистра 5 сдвига. По заполнении всех адресов запоминающего устройства 8 блок 2 управ ления режимами переводит генератор в режим считывания. В этом режиме в каждом гакте работы из запоминающих устройств 7 и 8 считываются одновременно два Y -разрядных числа, которые складываются по модулю 2 на сумматоре 9. На выходах cjTvnwaTopa 9 в .каждом такте считывания формируется п - разрядное псевдослучайное двоичное число. Таким образом, описанный генератор обладает повыщенным быстродействием без снижения его криптографической стойкости. Формула изобретения Генератор псевдослучайных последовательностей, содержащий генератор тактовых импульсов, выход которого соединен со входом блока управления, первый выход которого подключен к управляющему входу селектора адреса, первая группа входов которого соединена с выходами первого регистра сдвига с сумматором по модулю два в цепи обратной связи, запсминающее устройство, информационные входы которого соединены с выходами второго регисгра сдвига с сумматором по модулю два в цепи обратной связи, а адресные входы соедииень с первой группой выходов селектора адресов, третий регистр сдвига с сумматором по модулю два в цепи офагной связи, о тличающийся тем, что, с целью повышения быстродействия, в него дополнительно введены запоминаю -. щее устройство и п - разрядный сумматчэр по модулю два, входы которого соединены с выходами запоминакипих устройств, при- чем информационные и адресные входы дополнительного запоминакяпего устройства подключены соответственно к выходам BTOpoiX) peimctpa сдвига с сумматором по модулю два в цепи статной связи в ко второй группе выходов селектора адресов,. вторая группа входов которого через третий регистр сдвига с сумматором по модулю два в uerai обратной связи соединена с вторым выходом блока управления, третий и четвертый выходы которого соответственно подключены ко входам первого и второго регистров сдвига с сумматоро.т 8 3и по модулю два в цепи обратной связи. Источники информаюш, принятые во внимание при экспертизе I. Авторское свидетельство СССР N9 437062, кл. Q 06 F 1/02, . 2/Электроника № 1, (16737 с. 66 (прототип).

Авторы

Даты

1981-10-07—Публикация

1979-10-12—Подача