Изобретение относится к вычислительной технике и может быть примене но в дешифраторах универсальных и специсшизированных цифровых вычислительных машин. Известны схемы дешифраторЬв контролем и обнаружением ошибок, содержащие элементы И, ИЛИ, схемы KOHt Роля С1,С23 и СЗ. Недостатком таких дешифраторов яв ляется плохая диагностируемость, сое тоящая в том, что в них контролируется непосредственно работа дешифраторов и обнаруживаются наиболее веро ятные ошибки (чаще всего появление двух ИЛИ более единиц или отсутствие единицы на выходах дешифратора). При обнаружении ошибки часто нельзя указать элементарную логическую схему, в которой она произошла, поэтому необходимо проводить проверку правильности работы дешифратора на всех наборах входных переменных, что связан с большими затратами машинного времени.. Наиболее близким техническим реше нием кпредлагаемому изобретению является дешифратор, состоящий из двух каскадов однотипных модулей, каждый из которых имеет два иифо «ационных входа, два управляющих входа и четыре выхода, причем управляющие входы для каждого модуля первого каскада соединены вместе, а к управляющим входам модулей второго каскада подключено по одному выходу модулей первого каскада, причем наборы выходов модулей первого каскада не повторяются, а первые и вторые информационные входы модулей второго каскада соединены соответственно между собой 4. Недостатком этого устройства является то, что для полной диагности-g ки такой схемы необходимо подавать 2. входных наборов, что приводит к большим затратам мгилинного ремеии. Цель изобретения - повышение быстродействия контроля и диагностики путем сокращения числа наборов, необходимых для полной диагностики дешифратора. Поставленная цель достигается тем, что в дешифратор, содержащий две группы дешифрирующих Ачеек, причем информационные входы дешифрирующих ячеек первой группы являются группой информационных входов дешифратора, первый и второй управяякхцие входы каждой дешифрирующей ячейки

первой группы объединены и являются соответственно первым и вторым управляющими входами дешифратора, выходы каждой 1-ой дешифрирующей ячейки второй группы являются группой выходов дешифратора,.введена группа из 2п элементов ИЛИ, к первому и второму управляющим входам каждой девшфоиоующей ячейки торой ГРУППЫ подключены выходы соответствующей пагы элементов ИЛИ, первые входы всех элементов ИЛИ группы соединены с третьим управляющим входом дешифpaTopai. каждый i -и выход к-ой дешифрлрующей ячейки первой группы соединен со вторыми входами Р-ых элементов ИЛИ группы ((к-1)+ 4(ч- + €, где С 1-4, , 1-4 , первые информационные входы дешиффирующих ячеек второй группы объединены и являются первым информационным входом дешифратора, вторые информационные входы дешифрирукяцих ячеек второй групгш объединены и являются вторым информационным входом дешифратора.

Кроме того, каждая дешифрирующая ячейка содержит четыре элемента И идва.элемента НЕ, причем первый и второй управлякйдие входы дешифрирукицей ячейки соединены соответственно с первыми и вторыми входами всех элементов И, выходы которых являются выходами дешифрирующей ячейки, первый информационный вход дешифрирующей ячейки соединен с первыми входами первого и второго элементов И и через первый элемент НЕ с первыми входами третьего и четвертого элемента И, второй информационный вход дешифрирукмцейячейки соединен со вторыми входами первого и третьего элемента И и через Ьторой элемент НЕ со вторыми входами второго и четвертого элементов И.

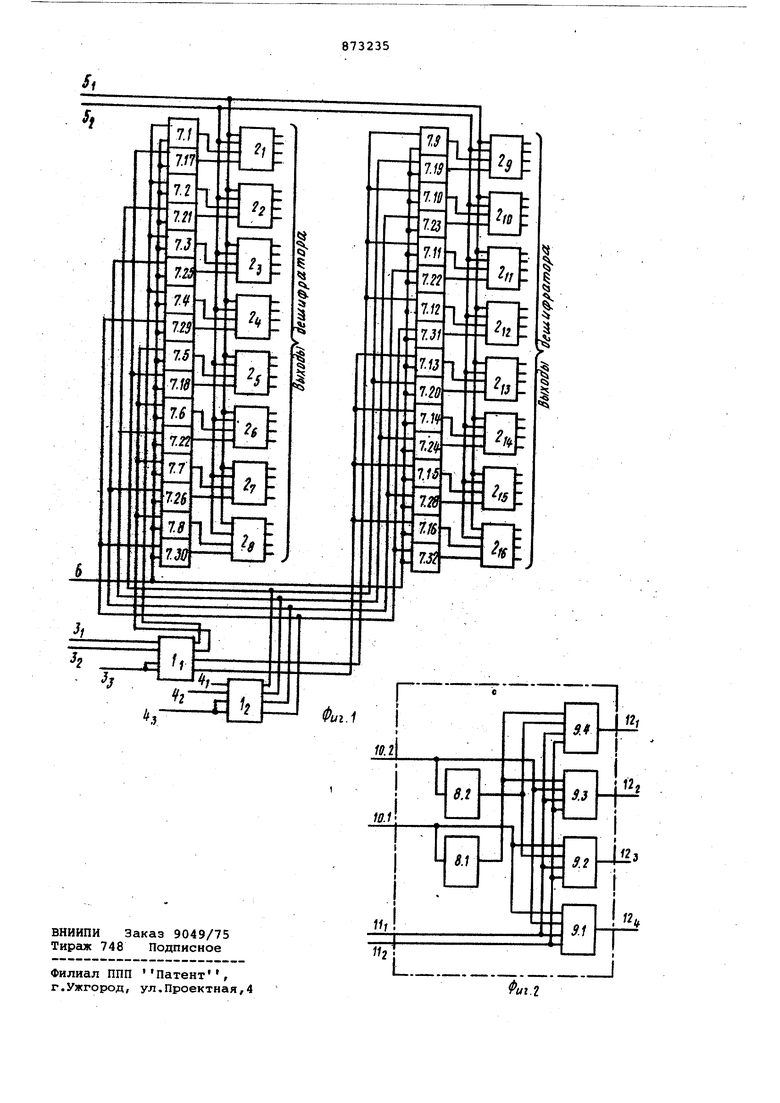

На фиг. 1 приведена схема дешифратора, на фиг. 2 дешифрирукхцая ячейка.

Дешифратор содержит дешифрирующие ячейки 1.1 и 1.2 первой группы, .дешифрирующие ячейки 2.1...2.16 второй группы, информационные входы устройства 3.1 и 3.2, входную шину устройства 4.1 и 4.2, входную шину устройства 4.3, информационные входы дешиф ратора 5.1 и 5.2 управляющий вход 6, элементы ИЛИ 7.1, 7.2...7.32. Дешифрирующая ячейка состоит иэ двух элементов НЕ 8.1 и 8.2 и четырех элементов И 9.1...9.4, информационных входов 10.1 и 10.2, управляющих входов 11.1 и 11.2, выходов 12.1...12.4 дешифрирукнцей ячейки.

Дешифратор работает следующим образом.

При нормальном режиме работы на управляющий вход 6 подается логический сигнал О и тогда сигналы на выходах элементов ИЛИ 7 группы определяются только сигналами на выходах Ьешифрирующей первой группы 1.1 и 1.2. При этом на управляющие входы дешифрирующих ячеек первой группы 1.1 и 1.2 всегда подается ло гический сигнал 1. Возбужденным будет тот выход дешифратора, который соответствует набору входных информационных сигналов, подаваемых на входы 3.1 и 3.2, 4.1 и 4.2, 5.1

и 5.2. Когда необходимо проводить

диагностику дешифратора, на управляю-, щий вход б подают логический сигнал 1. Тогда на всех выходах элементов 7 группы сигналы равны 1 и все элементы И 9 дешифрирующих ячеек

5 второй группы 2.1...2.16 открыты.

На входы 5.1 и 5.2 подаются всевозможг ные кодовые комбинации (в данном случае их 2 и тем самым последовательно возбуждены все выходы 12.1...

0 12.4 каждой дешифрирукядей ячейки второй группы. Таким образом, на первом этапе проверяются дешифрирующие ячейки второй группы дешифратора 2. 1. .. 2. 16. После этого на управляющий вход 6 подают сигнал логического О. На входы 5.1 и 5.2 можно подавать любой набор. Подавая на входы 3.1 и 3.2,4.1 и 4.2 всевозможные кодовые комбинации (в данном

Q случае их ) можно прэверить

правильность -функционирования дешифрирующих ячеек первого-каскада 1.1 и 1.2. Необходимость проверки на всех наборах входных сигналов для дешифрирующих ячеек первой группы 1.1 и 1.2 вытекает из того, что надо проверить прохождение сигналов с выходов дешифрирующих ячеек первой группы к выходам всех дешифрирующих ячеек второй группы 2.1...2.16. На

0 этом диагностика дешифратора заканчивается.

Таким образом, для проверки правильности функционирования дешифратора, nocTpo jHoro на однотипных

5 дешифрирующих ячейках, необходимо подать на его входы 2 наборов, т..е. 20, а не 2 64. Сокращение ..числа наборов, йеобходиьалх для полной диагностики, приводит к сокращению

Q времени, затрачиваемого на нее. Очевидно, что быстродействие дешифратора, построенного на однотипных дешифрирующих ячейках с дополнительными элементами ИЛИ, не уменьшается. При увеличении числа дешифрируемых

разрядов выигрыш в быстродействии контроля еще больше.

Формула изобретения

Дешифратор, содержащий две группы, дешифрирующих ячеек, причем информационные входы дешифрирующих ячеек первой группы являются группой информационных входов дешифратора, первый и второй управляющие входы каждой дешифрирующей ячейки первой группы объединены и являются соответственно первым и вторым управляющими входами дешифратора, выходы каждой дешифрирующей ячейки второй группы являются группой выходов дешифратора, отличающийся тем, что, с целью повышения быстродействия кон роля и диагностики, в него введена группа из 2 и элементов ИЛИ, к первому и второму управляющим входгш каждой дешифрирующей ячейки второй группы подключены выходы соответствующей пары элементов ИЛИ, первы входы всех элементов ИЛИ группы соединены с третьим управляющим входом дешифратора, каждый f-ый выходК-о дешифрирующей ячейки первой группы соединен со вторыми входами Р-ых элементов ИЛИ группы ( (к-1)+ 4M-1)+ е , где е-1-4, к 1-2, 4 1-4), первые информационные входы дешифрирующих ячеек второй группы объединены и являются первым информационным входом дешифратора, вторые информационные входы дешифрирующих ячеек второй группы объединены и являются втрршд информационным входом дешифратора.. ; 2. Дешифратор по п.1, о т-л и ч а ю щ и и с я тем, что каждая дёшифрирующая ячейка содержит четыре элемента И и два элемента НЕ, причем первый и второй управляющие входы дешифрирующей ячейки соединены соответственно с первыми и вторыми входа . ми всех элементов И, выходы кото(ос являются выходами дешифрирующей ячейки, первый информационный вход дешифрирующей ячейки соединен с первюш входами первого и второго элементов И и через первый элемент НЕ с первыми входами третьего и четвертого элемента И, второй информационный вход дешифрирующей Ячейки сое-. дин.ен со вторьми входами первого и третьего элемента И и через второй элемент НЕ со вторьв ш входами второго и четвертого элементов И. Источники инфО1 мации принятые во внимание при экспертизе 1.Авторское свидетельство СССР 305472, кл. G 06 F 5/02, 16,03.70. 2.Авторское свидетельство СССР № 398951, кл. G 06 F 11/02, 24.04.70. 3.Пате т США 3585377, 235-135, опублик. 16.06.69. 4.Корнейчук В.И.Тарасенко В.Н и Тесленко А.П. Синтез модульных структур дешифраторов. Автоматика и вычислительная техника, 1973, № 6, 0.68, рис. 4 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА КОММУТАЦИИ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1992 |

|

RU2126990C1 |

| Устройство для вычисления дискретного преобразования Фурье | 1990 |

|

SU1725228A1 |

| Способ и устройство автоматизированного структурирования мультикультурных учебных групп | 2016 |

|

RU2618387C1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1325511A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1988 |

|

SU1508233A1 |

| Устройство для сравнения чисел в модулярном коде | 1985 |

|

SU1256013A1 |

| РЕГИСТР СДВИГА | 2003 |

|

RU2247433C2 |

| Счетчик с кодом Либау-Крейга | 1985 |

|

SU1275764A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1735856A1 |

| Дешифратор на @ входов с контролем | 1982 |

|

SU1038934A1 |

Авторы

Даты

1981-10-15—Публикация

1979-12-17—Подача