Изобретение относится к авгомагике

н аычиспитепьной технике и моясвт быть использовано при построении узпсв я& скретных устройств, входящих в состав бгюков память и процессоров.

Известен с контролем, содержащий элементы И, ИЛИ, НЕ, регистр, иыходы которого соединены с входами дешифратора и триггера четности, грутшы выходов дешифратор соединены соответственно с входами первой грутшы элементов ИЛИ, одноименные к 1ходь каждой грутты выходов дешифратора совцишны соответственно с ваддама второй группы элементов ИЛИ l 1

Недостаток данного дешифратора в том что количество аппаратуры контроля дешифратора, быстро нарастает с увеличение числа его BbisoaoB.

Наибопее близким к предпагаемому газ технической сущности является цешифра- Tops содержащий группу элементов ИЛИ и две грутшы дешифрирующих ячеек, каждая из которых содержит четыре элемента И, два элемента НЕ, два информационных и два управгшющих входа, причем первые информационные входы дешифрирующих ячеек второй грутты объединены и явпяются первым информационным входом дешифратора, вторые инфор1у1ационные входы дешкфриряоших ячеек второй групггы обг единень и являются вторым инк{)ормациов ным входом дешифратора, утгравляюлшда входы каждой из дешифрирующих ячеек второй группы подключены к выходам соответствующей пары элементов ИЛИ, первые В7чодь всех элементов ИЛИ объединены и являются третьим управляющим входом дешифратора, выходы казадой дешифрирующей ячейки второй группы являются группой выходов дешифратора, управляющие входы каждой деитифрирующей ячейки первой объединены и ЯВТ1ЯЮТСЯ соответственно первым и вторым управпяющими входами дешифратора, информационные входы дешифрирующих .ячеек первой грутшы являются группой информационных входов дешифратора, каждый i-и вход К-й дешифрирующей ячейки первой грутшы соединен с вторыми входами Р-х элем «тов ИЛИ группы (к-1)+4( i-D-f е , где Р 1-4, к , i -1-4 21

Недостатками изБЭСтнрго дешифратора являются сложность его структура) и относительно низкое быстродействие конт ропя, требующего увеличения чиспа тестовых проверок с ростом числа выходов дешифратора.

Цель изобретения - поЕЫшение быстродействия контроля.

Поставленная цепь достигается тем, что в дешифратор на п входов с лонтропем, содержащий 2Т дешифрирукяцнх ячеек каждая из которых содержит элемент И, причем выходы элементов И всех дешш рирующих ячеек являются первой группой выходов дешифратора, каждый т-й ( i 2,.,.,h ) информационный вход дешифратора соединен с соответствующими входами элементов И 2 /2 дешифрирующих ячеек, при1ем первый информационный вход дешифратора соединён с соотзветствуютцими входами элементов И четной (нечетной) грутшы из2 /2дешифрирующих ячеек, второй информационный вход дешифраторе сое дижн с соответствующими входами элементов И двух чет№1х (нечетных) групп из 2 /4 дешифрирутощих ячеек, п -и информационный вход дешифратора соединен с соответствуюхцнми входами элементов И чет№)х (iffiHefiibtit) дешифрирующих ячеек, введены п суг/гмагоров по модулю два, (.) и () дешифрирующие ячейки, а каждая из (2 +2)-х дешифрирующих ячеек дополнительно содержит элемент ИЛИ, п входов которого соединены с соответствующими входами эгаемента И этой же дешифр{фующей ячейки, выходы элементов И и ИЛИ 2 дешифрирующих ячеек соединены с соответствующими вхо дами (2 +1)-й дешифрирующей ячейки, которой являются второй группой выходов дешифратора, управляющий вход которого соединен с первыми входами И сумматоров по модулю два, второй вход каждого из сумматоров по кгодупю два соединен с соответствующим i -м информационным входом дешифратора, выход каждого из п сумматоров по модулю ова соединен с соответствуклцш.Г входом (2 +2)--й дешифрирующей ячейки и с соответствующими входами элементов И дешифрирующих ячеек, причем выход сумматора по модулю два, соединенного с первым информационным входом дешифратора, соединен с соответствующими входами элементов И нечетной (четной) группы

2

иа -V-дешифрирующих ячеек, выход сумматора по модулю два, соединенного с вторым информационным входом дешифратора, соединен с соответствующими входаьге элементов И нечетных (четных) групп из2 /4 дешифрирующих ячеек, выход сумматора по модулю два, соединенного с П -м информационным входом дешифратора, соединен с соответствующими входами

элементов И нечетных (четных) дешифрирующих ячеек, выходы {2 +2)-й аеши(| рирующей ячейки являются третьей группой выходов дешифратора.

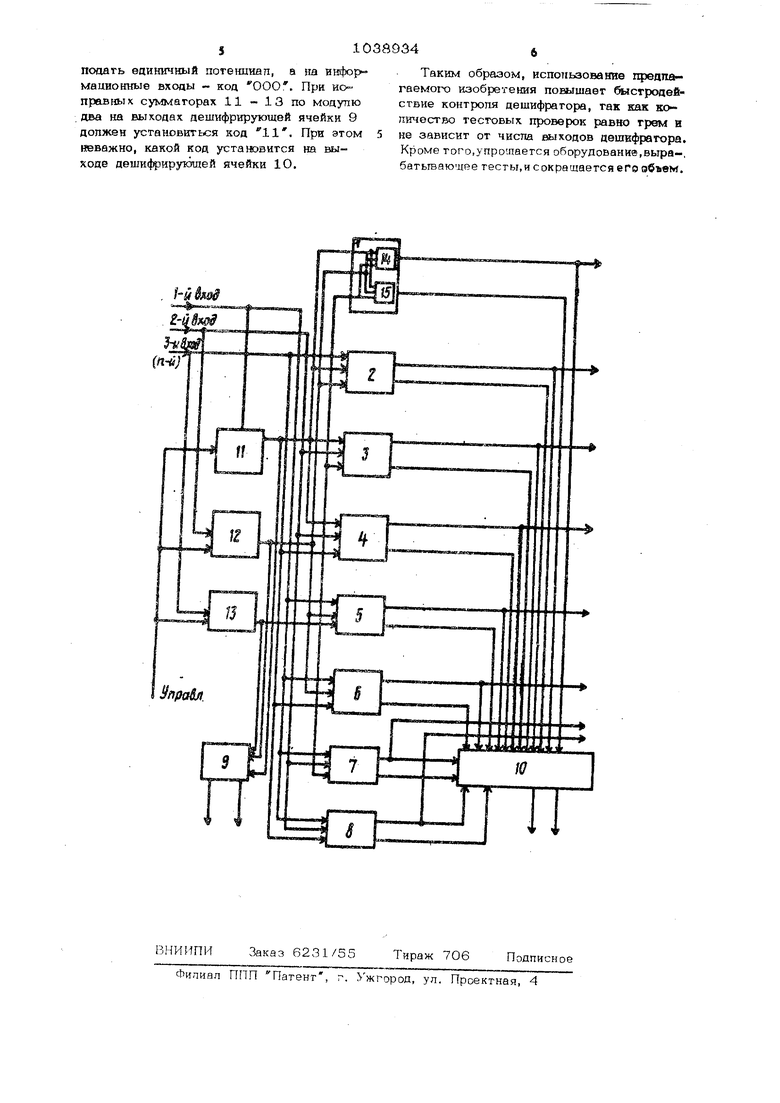

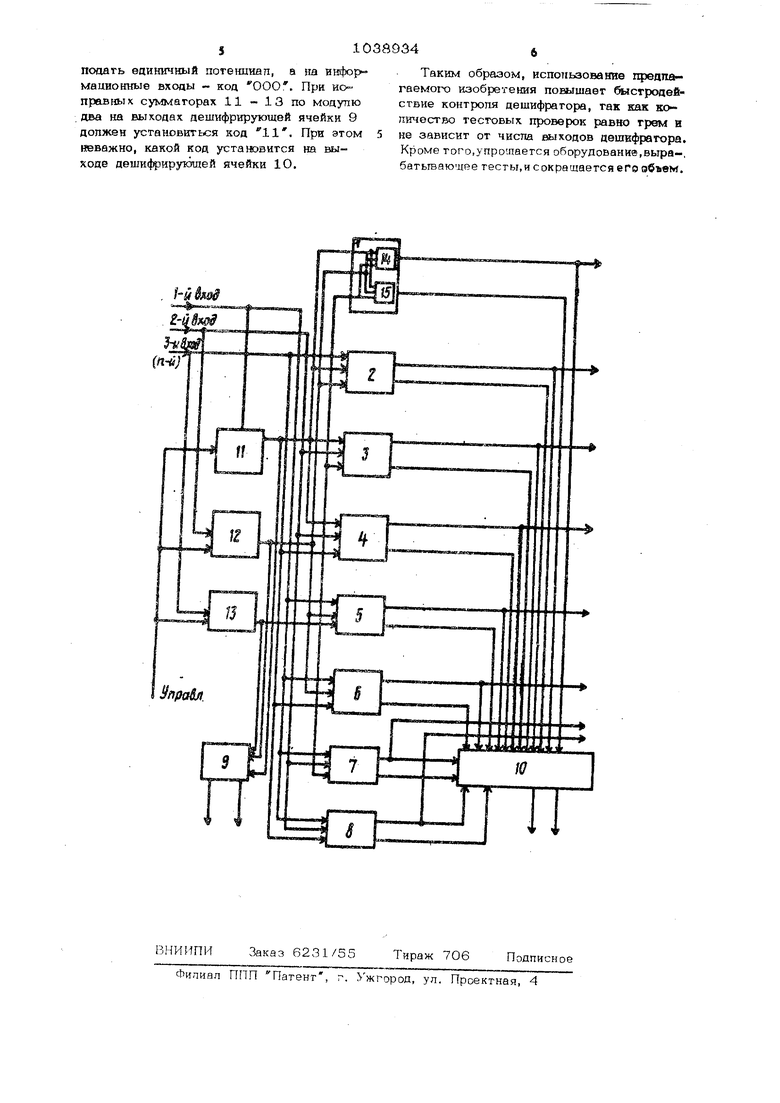

На чертеже представлена блок-схема однохч) из вариантов деши(|фатора на п входов с контролем дешифратора на три входа.

Схема содержит дешифрирующие ячейки 1-10, сумматоры 11-13 по модулю два, элемент И 14 и элемент ИЛИ 15.

Деши4ратор имеет три информационных и один управляющий входы. Выходы элементов И дешифрирующих ячеек 1-8 составляют группу информационных выходов дешифратора, а выходы дешифрирующи ячеек 9 и10 - две группы выходов для результатов контроля работы дешифратора

Дешифратор работает следующим образом.

В рабочем режиме ма управляющий вход подается единичный потенциал. При этом каждый из сумматоров 11-13 по модулю два будет реализовывать функцию инверсии входного информационного сигнала. Логическая функция, реапизуемая сумматорами по модулю два, имеет вид

у , d;

где V - выходное значение сигнала сумматора;

С - входной управляющий сигнал; X - входной информационный сигнал. При ,.

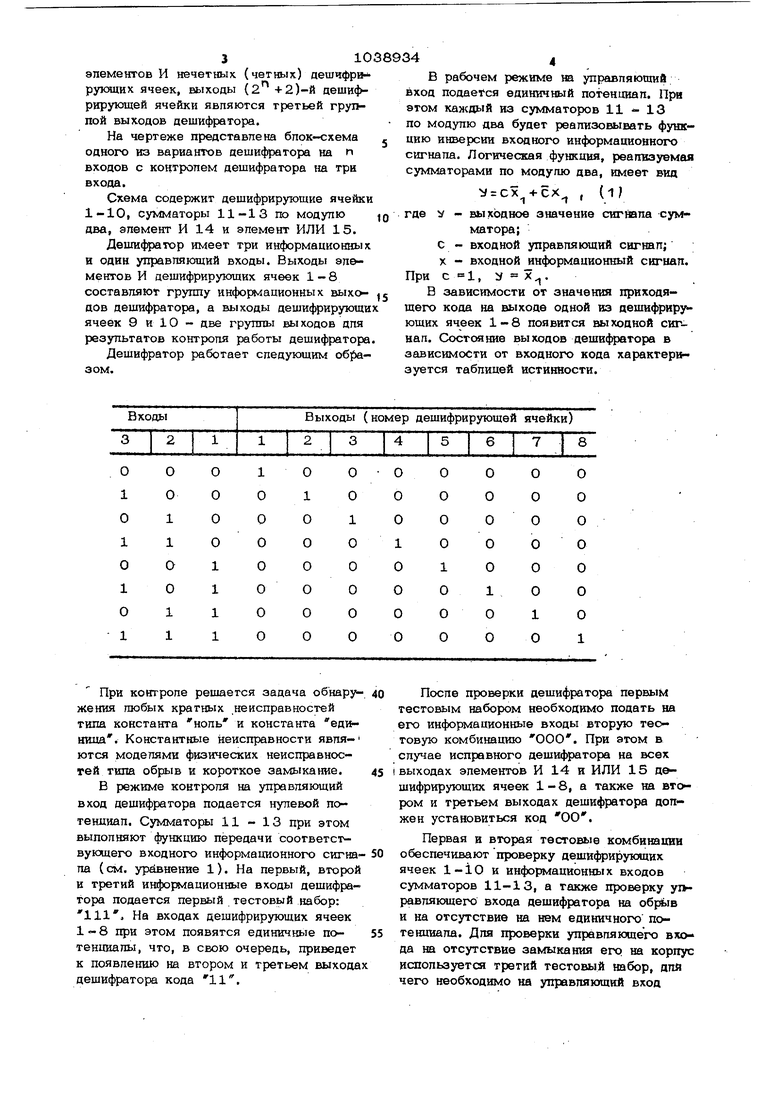

В зависимости от значения приходящего кода на выходе одной из дешифрирую ющих ячеек 1-8 появится выходной сигнал. Состояние выходов дешифратора в зависимости от входного кода характер зуется таблицей истинности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1987 |

|

SU1501043A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1981 |

|

SU991516A1 |

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1481901A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Сигнатурный анализатор | 1981 |

|

SU1048475A1 |

| Микропрограммное устройствоупРАВлЕНия C КОНТРОлЕМ | 1979 |

|

SU798836A1 |

| Устройство для исправления ошибокВ блОКЕ пАМяТи | 1979 |

|

SU842976A1 |

| КОЛЬЦЕВОЙ ДЕШИФРАТОР | 1972 |

|

SU342298A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

ДЕШИФРАТОР НА П ВХОДОВ С КОНТРОЛЕМ, содержащий 2 дешифрирующих ячеек, каждая из которых содержит эпе мент И, причем выкоды эпементов И всех дешифрирующих ячеек являются первой группой выходов дешифратора, каждый 1-й( 1,2,...,п) информационнь й вход дешифратора соединен с соответствующими входами эпементов И 2 /2дешифрирующих ячеек, причем первый информационный вход дешифратора соединен с соответствующими входами эпементов И четной (нечетной) группы из дешифрирующих ячеек, второй информационный вход дешифратора соединен с соответствующими входами эпементов И двух четных (нечетных.) групп дешифрирующих ячеек, п -и информационный вход дешифратора соединен с соответствующими входами элементов И четных (нечетных) дешифрирующих ячеек, отличающийся тем, что, с целью повышения быстродействия контропя, в дешифратор введены Ъ сумматоров по модулю два, () и () дешифрирующие ячейки, а каждая из ()-х -...J дешифрирующих ячеек дополнительно сендержит элемент ИЛИ, п входов которого соединены с соответствующими входами элемента И этой же дешифрирующей ячейки, выкоды элементов И н ИЛИ 2 дешифрирующих ячеек соединены с соответствующими входами

При контроле решается задача обнару-. жения любых кратных .неисправностей типа константа ноль и константа единица. Константные неисправности являются моделями физических неисправностей типа обрыв и короткое замыкание.

В режиме контроля на управляющий вход дешифратора подается нулевой потендиал. Сумматоры 11-13 при этом выполняют функцию передачи соответствующего входного информационного сигнала (см. уравнение 1). На первый, второй и третий инфору1ационные входы дешифратора подается первый тестовый набор: 111, На входах дешифрирующих ячеек 1-8 при этом появятся единичные потеншшлы, что, в свою очередь, приведет к появлению на втором и третьем выходах дешифратора кода 11.

После проверки дешифратора первым тестовым набором необходимо подать на его информационные входы вторую тестовую комбинацию ООО. При этом в случае исправного дешифратора на всех {выходах элементов И 14 и ИЛИ 15 дешифрирующих ячеек 1-8, а также на втором и третьем выходах дешифратора допжен установиться код 00.

Первая в вторая тестовые комбинации обеспечивают проверку дешифрирующих ячеек 1-10 и информационных входов сумматоров 11-13, а также проверку yi равляклдего входа дешифратора на обрьш и на отсутствие на нем единичного потенциала. Для проверки управляющего входа на отсутствие замыкания его на корпус используется третий тестовый набор, дпя чего необходимо на управляющий вход

пооать единичный поте1щиап, а ка инфор- мационные входы - код ООО. При иоnpastbix сумматорах 11 13 по модулю два на выходах дешифрирующей ячейки 9 должен установиться код 11. При этом неважно, какой код установится на выходе дешифрирующей ячейки 10.

(

Таким образом, испопьзование предпагаемого изобретения повышает быстродействие контроля дешифратора, так как ко пичество тестовых проверок равно трем и не зависит от чиспа йыходов дешифратора. Кроме того,упрощается оборудований,выра-, батывающйе тесты,и сокращается его .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для получения сажи, ретортного графита и других угольных продуктов из натурального газа | 1926 |

|

SU40831A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Дешифратор | 1979 |

|

SU873235A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-08-30—Публикация

1982-01-04—Подача