(54) УСТРОЙСТВО ДЛЯ ЗАДАНИЯ РЕЖИМОВ РАБОТЫ

ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ ГШОИНЫ И ИНДИКАЦИИ Изобретение относится к вычислительной технике и может быть исполь зовано при построении ЦВМ. Известно устройство для задания режимов работы ЦВМ и ее индикации, включающее матрицу индикаторных лам и матрицу переключателей, которые связаны с блоком обработки данных к белем. Взаимодействие устройства и блока выработки данных осуществляет ся по специальным цепям, которые уп равляются генератором и подключвцот внутренние регистры блока обработки данных к матрицам пульта управления 1 . Недостатком данного устройств является сложность схем синхронизации и большие затраты оборудования на регшизацию передачи информации из устройства в блок обработки информации, и наоборот.. Наиболее близким к изобретению п технической сущности и достигаемому результату является устройство длй задания режимов работы ЦВМ и индикации ее состояния, содержащее блок набора Информации, информационные выходы которого соединены со входами блока вшхачи информации, блок& сравнения адресов, выход которого ЕЕ СОСТОЯНИЯ соединен с одним входом блока управления, другой вход которого соединен с выходом блока выработки управляющих сигисшов, а также регистром признаков, выходы которого соединены с блоком выдачи информации, блок индикации, соединенный с регистром индикации и процессором, к которому подключены блоки сравнения адресов, управления,выдачи информации, регистр индикации 2. Недостатком устройства является его нТазкое быстродействие. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для задания режимов работы цифровой вычислительной машины и индикации ее состояния, содержащее блок набора информации, выход которого соединен с первым входом схемы сравнения и со входом блока элементов И, блок ручного управления, блок индиксщии и шифратор, первый, второй входы и которого соединены соответственно с выходом схемы сравнения, с первым выходом блока ручного управления и с первым выходом устройства, причем второй вход схемы сравнения является первым

ВХОДОМ устройства, введены блок памяти, счетчик, коммутатор и дешифратор, причём информационный вход блока памяти соединен со вторым входом устройства и с выходом блока элементов И, третий вход устройства через дешифратор соединен со входом блока ручного управления, второй выход которого соединен.с запускающим входом блока памяти, третий выход блока ручного управления соединен со счетным входом счетчика и с управляющим входом коммутатора, первый информационный вход которого соединен с четвертым входом устройства, выход счетчика соединен со входом блока набора информации, со вторым информационным входом коммутатора и с адресным входом блока индикации, анформационный вход которого и второй выход устройства соединены с выходом блока памяти, а адресный вход блока памяти соединен с выходом коммутатора ,

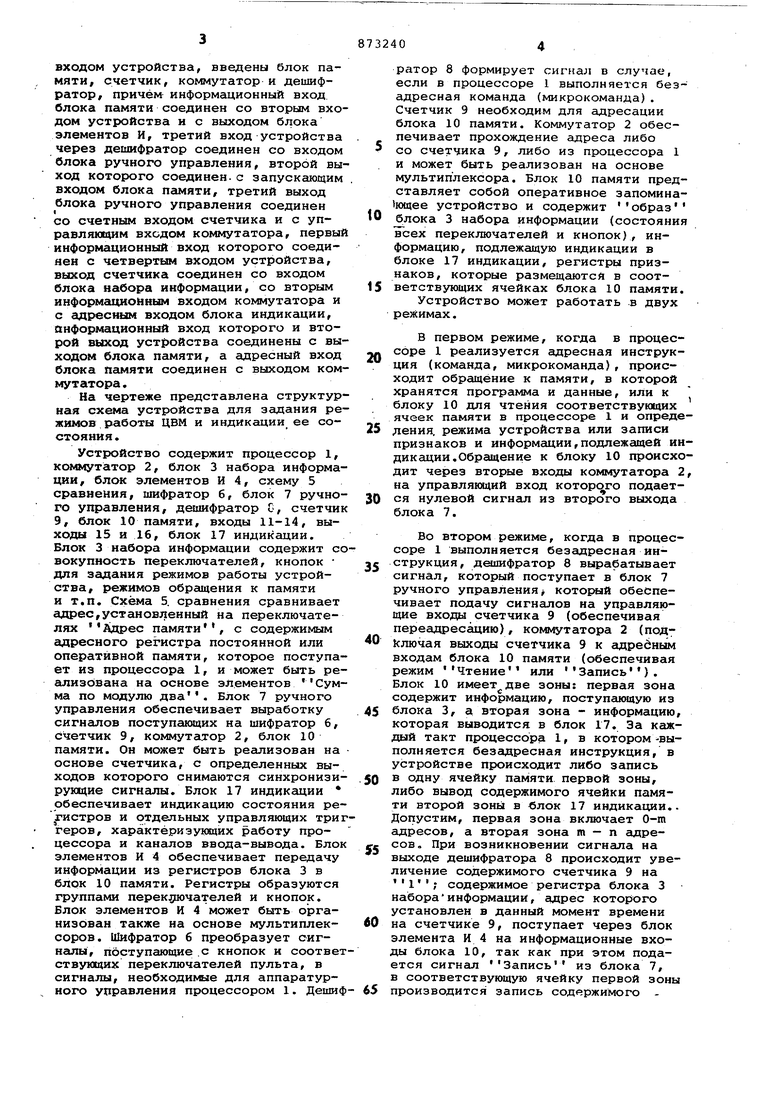

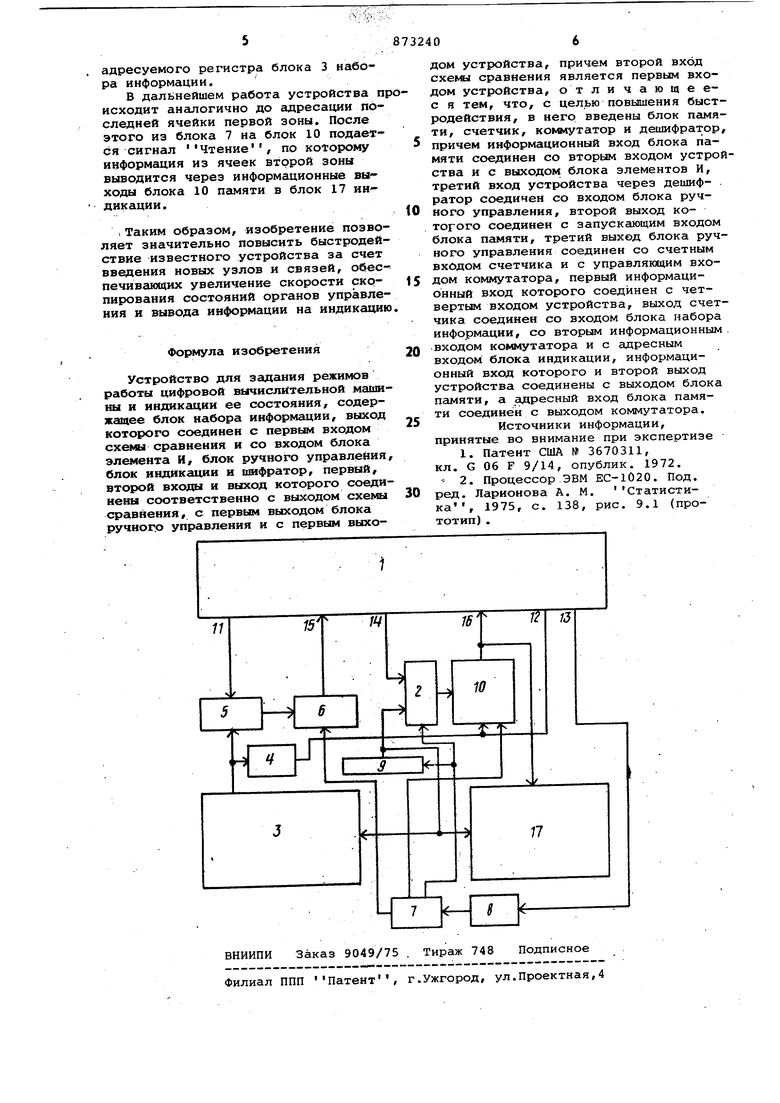

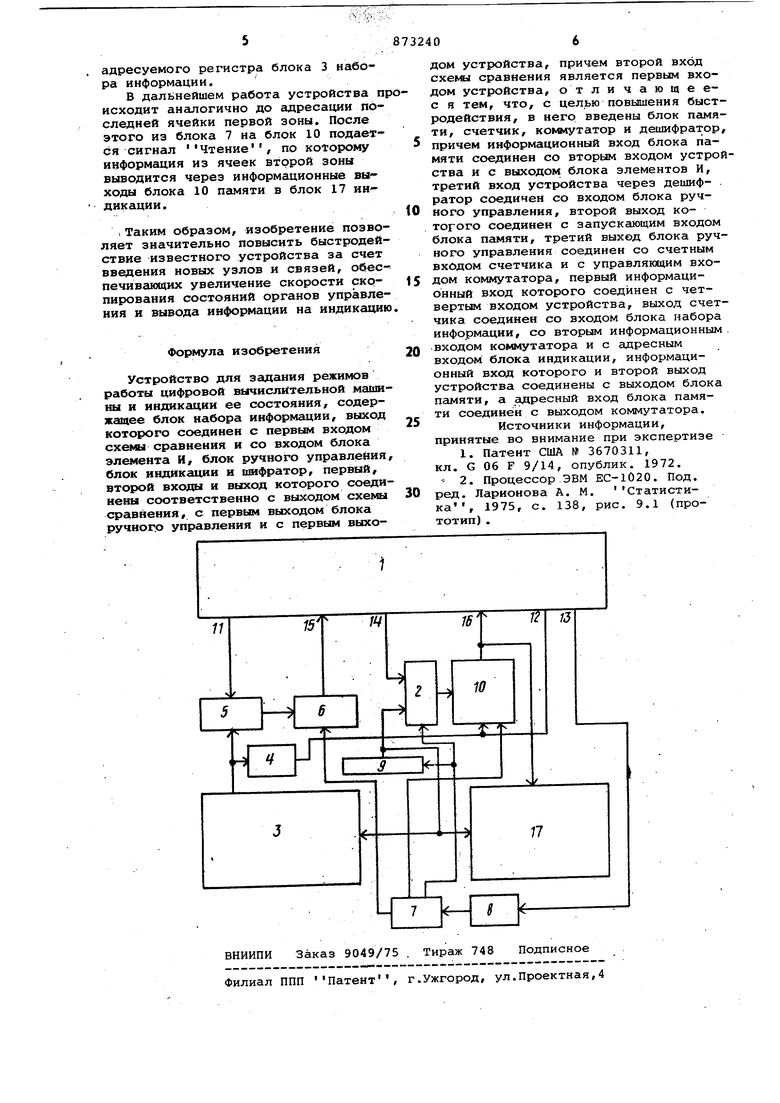

На чертеже представлена структурная схема устройства для задания режимов работы ЦВМ и индикации ее состояния.

Устройство содержит процессор 1, коммутатор 2, блок 3 набора информации, блок элементов И 4, схему 5 сравнения, шифратор 6, блок 7 ручного управления, дешифратор С, счетчик 9, блок 10 памяти, входы 11-14, выходы 15 и 16, блок 17 индикации. Блок 3 набора информации содержит совокупность переключателей, кнопок для задания режимов работы устройства, режимов обрсицения к памяти и т.п. Схема 5, сравнения сравнивает адрес,установленный на переключателях Адрес памяти , с содержимым адресного регистра постоянной или оперативной пгшяти, которое поступает из процессора 1, и может быть реализована на основе элементов Сумма по модулю два . Блок 7 ручного управления обеспечивает выработку сигналов поступакнцих на шифратор 6, счетчик 9, коммутатор 2, блок 10 памяти. Он может быть регшизован на основе счетчика, с определенных выходов которого снимаются синхронизирующие сигналы. Блок 17 индикации обеспечивает индикацию состояния ре гистров и отдельных управляющих триггеров, характёризукяцих работу процессора и каналов ввода-вывода. Блок элементов И 4 обеспечивает передачу информации из регистров блока 3 в блок 10 памяти. Регистры образуются группами перекл оочателей и кнопок. Блок элементов И 4 может быть организован также на основе мультиплексоров. Шифратор б преобразует сигналы, поступающие .с кнопок и соответствующих переключателей пульта, в сигналы, необходимые для аппаратурного управления процессором 1. Дешифратор 8 формирует сигнал в случае, если в процессоре 1 выполняется безадресная команда (микрокоманда). Счетчик 9 необходим для адресации блока 10 памяти. Коммутатор 2 обеспечивает прохождение адреса либо 5 со счетчика 9, либо из процессора 1 и может быть реализован на основе мультиплексора. Блок 10 памяти представляет собой оперативное запомина1ющее устройство и содержит образ

О лока 3 набора информации (состояния всех переключателей и кнопок), информацию, подлежащую индикации в блоке 17 индикации, регистры признаков, которые размещаются в соответствующих ячейках блока 10 памяти. Устройство может работать .в двух режимах.

В первом режиме, когда в процессоре 1 реализуется адресная инструкция (команда, микрокоманда), происходит обращение к памяти, в которой хранятся программа и данные, или к блоку 10 для чтения соответствующих ячеек памяти в процессоре 1 и опреде5 дения. режима устройства или записи признаков и информации,подлежащей индикации.Обращение к блоку 10 происходит через вторые входы коммутатора 2, на управляющий вход которс го подается нулевой сигнал из второго выхода блока 7.

Во втором режиме, когда в процессоре 1 выполняется безадресная инJ струкция, дешифратор 8 вырабатывает сигнал, который поступает в блок 7 ручного управленияj который обеспечивает подачу сигналов на управляющие входы счетчика 9 (обеспечивая переадресацию}, коммутатора 2 (под0 kлючaя выходы счетчика 9 к адредным входам блока 10 памяти (обеспечивая

Чтение или Запись ).

режим

Блок 10 имеет две зоны: первая зона содержит информацию, поступающую из

блока 3, а вторая зона - информацию, которая выводится в блок 17. За каждый такт процессора 1, в котором-выполняется безадресная инструкция, в устройстве происходит либо запись

в одну ячейку памяти первой зоны, либо вывод содержимого ячейки памяти второй зоны в блок 17 индикации.. Допустим, первая зона включает 0-т адресов, а вторая зона m - п адресов. При возникновении сигнала на выходе дешифратора 8 происходит увеличение содержимого счетчика 9 на содержимое регистра блока 3 набораинформации, адрес которого установлен в данный момент времени

на счетчике 9, поступает через блок элемента И 4 на информационные входы блока 10, так как при этом подается сигнал Запись из блока 7, в соответствующую ячейку первой зоны

производится запись содержимого

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки и контроля хода программ | 1988 |

|

SU1529227A1 |

| Устройство для сопряжения | 1983 |

|

SU1124277A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для проверки функциональных блоков | 1980 |

|

SU1008745A1 |

| Устройство для обмена информацией между аналоговой и цифровой вычислительными машинами | 1990 |

|

SU1755372A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Внешнее устройство управления | 1978 |

|

SU736100A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

| Устройство для контроля электромонтажа | 1989 |

|

SU1688263A1 |

Авторы

Даты

1981-10-15—Публикация

1979-10-08—Подача