(54) УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ПОДСТРОЙКИ ЧАСТОТЫ

. 1 .

Изобретение относится к радиотехнике и может использоваться в аппаратуре систем связи.

Известно устройство автоматической подстройки частоты, содержащее последовательно соединенные генератор, управляемый делитель, блок сравнения фаз, другой вход которого является, входом устройства, и накапливающий . сумматор, к второму входу которого подключен регистр, а выход накапливающего сумматора подключен к управляющему входу управляемого делителя 1J.

Однако известное устройство имеет 5 сравнительно невысокую точность.

Целью изобретения является повьаиение точнорти ;

Цель достигается TeW, что межд входом устройства и входом регистра 20 включены последовательно цифровой частотный детектор, к другому входу которого подключен генератор, первый элемент И и счетчик - сумматор, меж-ду выходом счетчика - сумматора и его 5 первым управляющим входом включены последовательно второй элемент И, третий элемент И и триггер знака, между выходом второго элемента И и нулевым входом триггера знака включен чет-JO

вертый элемент И, другой выход триггера знака подключен к второму управляющему входу счётчика - сумматора, между выходом генератора и другим входом регистра включен последовательно пятый элемент И, счетчик, блок управления, другой вход которого подключен к генератору, v блок очередности, к второму входу которого подключен выход управляемого делителя, второй вы-ход блока очередности подключен к третьему входу накапливакяцего сумматора, второй, третий и четвертый выходы блока управления подключены соответственно к другому входу первого элемента И, к другому входу счетчика сумматора и к другому входу пятого элемента И,положительный знаковый выход цифрового частотного детектора по подключен к другому входу четвертого элемента Ник третьему управляющему входу счетчика - сумматора,отрицательный знаковый выход цифрового частотного детектора - к четвертому управляющему входу счетчика - сумматора и к другому входу третьего элемента И,третьи входы третьего и четвертого элементов И подключены к входу устройства, а дополнительные выходы управляемого делителя подключены к соотвеЧктвующим дополнительным входам цифрового частотного детектора.

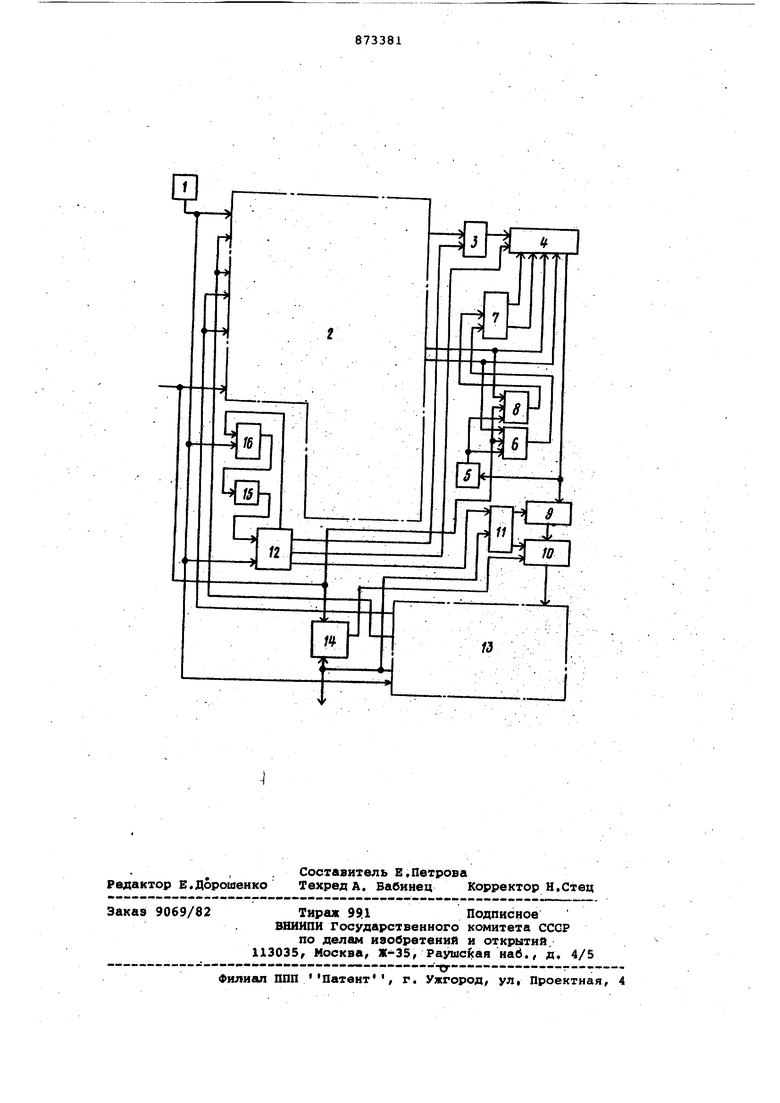

На чертеже приведена структурная электрическая схема предложенного устройства .

Устройство автоматической подстройки частоты содержит генератор 1, цифровой частотный детектор 2, первый элемент И 3, счетчик - сумматор 4, второй элемент И 5, третий элемент И б, триггер 7 знака, четвертый элемент И 8, регистр 9, накапливающий сумматор 10, блок 11 очередности, блок 12 управления, управляемый делитель 13, блок 14 сравнения фаз, счетчик 15 и пятый элемент И 16.

Устройство работает следующим образом.

Частота генератора 1 выбирается кратной частоте входного сигнала, т. е. имеет место приближенное равенство Tax ,., .. где Т Bj( период образующей частоты;

входных импульсов; К - целое число; Т г - период генератора 1.

Входной сигнал приходит не в виде сплошной регулярной последовательности импульсов, а в виде кодовых посылок. Точное значение числа К, обозначим его к , определяется по формуле

I TBX KNJ:|H

Tr N

где N - некоторое число периодов i eнератора 1;

п - количество периодов генерато-i ра 1, на которое число периодов частоты Tjx отличается от; N за время прохождения N пе- i риодов генератора 1.

CL,

Число N выбирается N 2, тогда еление на N сводится к сдвигу запятой Haq разрядов вправо. Подстойка астоты сводится к определению чиса п, подсчету точного значения коэфициента К и формированию частоты из колебаний генератора 1 по определеному коэффициенту К на управляемом елителе 13; реред началом работы четчик - сумматор 4 устанавливаетя в О, а триггер 7 в положение . Кодовая посылка входного сигнала, записывается в цифровом частотном детекторе 2 в виде соответствуюего кода фазы входного сигнала.

Вследствие нестабильности частоты генератора 1 момент прихода входного сигнала по отношению к формируе- V ым в цифровом частотном детекторе 2 стробам постепенно изменяется, следовательно, через некоторые промежутки времени значения кода фазы принимают разные значения. Если Tj-v К TBH/ цифровой частотный детектор 2 фиксирует такое временное первмещени е входного сигнала, при котором формируется потенциал плюс. Перемещение мсялента прихода входного сигнала в обратном направлении означает, что К Тд Tg, и на выходе цифрового частотного детектора 2 аналогичным образом формируется сигнал минус.

Полный оборот в смещении фазы ВХОДНОГО сигнала вызывает формирова;.ние сигнала ,что означает, что фаза входного сигнала сместилась на один период генератора 1. Синхронизацию работы устройства осуществляет Q блок 12.в начале такта работы блок 12 открывает прохождение ч стоты генератора 1 на счетчик 15 через пятый элемент И 16, который отсчитывает N 2 периодов генератора 1 и прохожс цифрового часдение сигналов

тотного детектора 2 через первый элемент И 3 на вход счетчика - суммато-. ра 4. Причем сигнал плюс цифрового частотного детектора 2 устанавли- вает счетчик - сумматор 4 в режим 0 прямого счета, а сигнал минус в режим обратного счёта.. Таким обра плюс

зом, при сигнале

на счетчике - сумматоре 4 получается прямой код количества сигналов i с цифрового частотного детектора 2, а при сигнале минус - дополнительный код 2 - п, где Р - количество разрядов счетчика - сумматора 4. В момент обнуления счетчика - сумматора 4,что

Дешифрируется вторым элементом И 5, производится по входному сигналу запись знака цифрового частотного детектора 2 через третий и четвертый элементы И б и 8 в триггер 7,причем

знак плюс записывается ,а Знак минус - О.

Таким образом, при качании периода Тр. в пределах - в момент прохождения содержимого счетчика - сумматора 4 значения нуля происходит смена знака в триггере 7. После переполнения счетчика 15 блок 12 закрывает входы счетчика 15 и счетчика - сумматора 4 через пятый и первый элементы И 16 и. 3 соответственно.

Затем блок 12 дает на счетчик - сумматор 4 импульс сдвига на один разряд вправо, причем, .если на тирггере 7 хранится код , :вписывается: код О, а если, триггер 7 хранит

код О, то вписывается l,.

Содержимое счетчика - сумматбра 4 после достаточно большого количества шагов счета равно числу п с точностью единицы младшего разряда. После каждого такта счета содержимое счетчика - сумматора 4. по импульсу с блока 12, прошедшему через блок 11, переписывается в регистр 9, содержимое которого участвует как слагаемое при

сложении в накапливающем сумматоре 10.

Суммирование производится сразу после формирования выходного сигнала. Блок 11 обеспечивает разнесение

по времени, смену информации в регистре 9 и суммирование в накапливающе сумматоре 10. Добавление числа К про изводится постоянной распайкой входо накапливающего сумматора 10, а деление числа п на 2 - разводкой выходо регистра 9 на вход накапливающего су матора 10 с сдвигом на q разрядов вправо. В результате содержимое накапливающего сумматора 10 делится на целую и дробовую часть, кроме того, так как число п может быть представлено как в прямом, так и в дополнительном коде, оно может как добавляться, так и вычитаться из общей суммы. Выходной сигнал управляемого делителя 13 в блоке 14 анализируется на временное рассогласование с входными кодовыми посылками. В случае на личия сдвига фаз формируется сигнал добавления или вычитания из :младшего разряда накапливающего сумматора 10. Работа блока 14 происходи в основном в начальный период работы устройства, так как точность подстройки частоты высокая, и рассогласов ние фаз накапливается редко. Предложенное устойство позволяет подстраивать частоту по кодовым посылкс1М входного сигнала и обеспечива ет любую наперед заданную точность надстройки. Формула изобретения Устройство автоматической подстройки частоты, содержащее последовательно соединенные генератор, управляемый делитель, блок сравнения фаз, другой вход которого является входом устройства, и накапливающий сумматор к второму входу которого подключен регистр, а выход накапливающего сумматора подключен к управляющему входу управляемого делителя, о т л ичающее с я тем, что, с целью по вышения точности, между входом устройства и входом регистра включены последовательно цифровой частотный детектор, к другому входу которого подключен генератор, первый элемент И и счетчик сумматор, между выходом сче.тчика - сумматора и его первым управляющим входом включены последовательно второй элемент И, третий элемент И и триггер знака. Между выходом второго элемента И и нулевым входом триггера знака включен четвертый элемент И, другой выход триггера знака подключен к второму управляющему входу счетчика - сумматора, между выходом генератора и другим входом регистра включены последовательно элемент И, счетчик, блок управления, другой вход которого.подключен к генератору, и блок очередности, к, второму входу которого подключен выход управляемого делителя, второй выход блока очередности подключен к (третьему входу накапливающего сумматора, второй, третий и четвертый выходы блока управления подключены соответственно к другому входу первого элемента И, к другому входу счетчика - сумматора к другому входу пятого элемр нта И, положительный знаковый выход цифрового частотного детектора подключен к другому входу четвертого элемента И и к третьему управляющему входу счетчика - сумматора, отрицательный знаковый выход цифрового частотного детектора - к четвертому управляющему входу счетчика сумматора и к другому входу третьего элемента И, третьи входы третьего и .четвертого элементов И подключены к входу устройства, а дополнительные выходы управляемого делителя подключены к соответствующим дополнительнымвходам цифрового частотного детектора. . . Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 576655, кл. Н 03 В 3/04, 1977 (про- тотип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Устройство для автоматической подстройки частоты | 1984 |

|

SU1298912A1 |

| Устройство цифровой фазовой автоподстройки частоты | 1982 |

|

SU1125748A1 |

| ФОРМИРОВАТЕЛЬ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1992 |

|

RU2033685C1 |

| Устройство фазовой автоподстройки частоты | 1987 |

|

SU1469553A1 |

| Устройство синхронизации с фазовой автоподстройкой частоты | 1988 |

|

SU1700751A1 |

| Цифровой частотный демодулятор | 1984 |

|

SU1298845A1 |

| Цифровой термометр | 1987 |

|

SU1571427A1 |

| Цифровой термометр | 1986 |

|

SU1397749A1 |

| Резервированный генератор импульсов | 1989 |

|

SU1619440A1 |

Авторы

Даты

1981-10-15—Публикация

1979-05-14—Подача