Изобретение относится к радиотехнике и может быть использовано в аппаратуре систем связи.

Цель изобретения - повьшение точности при одновременном упрощении.

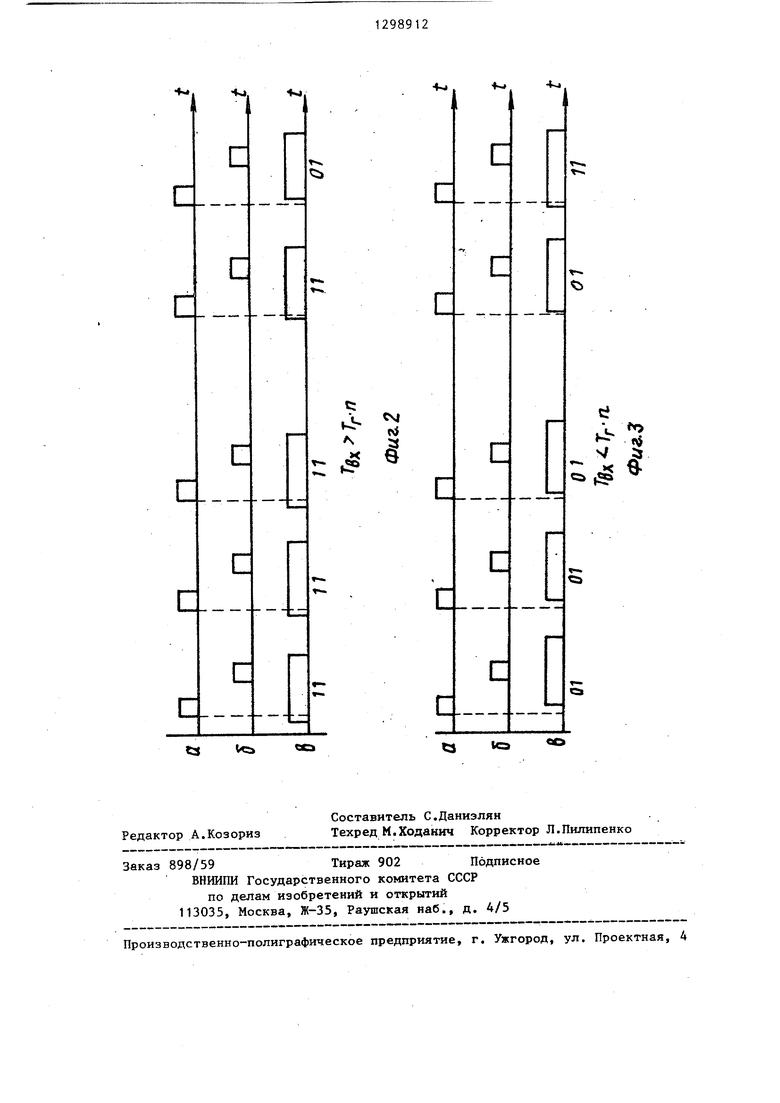

На фиг.1 представлена принципиальная электрическая схема устройства для автоматической подстройки частоты; на фиг.2 и 3 - временные диаграммы, поясняющие работу устройства.

Устройство для автоматической подстройки частоты содержит генератор 1, первьй дополнительный счетчик 2, распределитель 3 импульсов, чувствительный элемент 4, вьшолненный в виде третьего 5, четвертого 6, пятого 7 и шестого 8 D-триггеров, элемента И-НЕ 9, третьего 10, четвертого 11 и пятого f2 элементов И и седьмого 13 и восьмого 14 Р-триггеров, триггер 15 знака, первый элемент ИЛИ 16, первый 17 и второй 18 элементы И, элемент НЕ 19, первый 20 и второй 21 D-триг- геры, второй элемент ИЛИ 22, счетчик 23, регистр 24, управляемый делитель 25 частоты, выполненный в виде второ- . го дополнительного счетчика 26, блока 27 сравнения, шестого элемента И 28, третьего элемента ИЛИ 29, реверсивного регистра 30 сдвига, линии 31 задержки и мультиплексора 32.

Устройство для автоматической подстройки частоты работает следующим образом.

Входной сигнал представляет собой кодовую последовательность или регулярный сигнал частоты, примерно кратной 4aqTOTe генератора 1, причем длительность входного сигнала должна превышать четверть периода образующей его частоты и не может быть больше 3/4 того же периода. Так как частота генератора 1 выбирается в целое число раз большей частоты входного сигнала то частота генератора 1 делится в первом дополнительном счетчике 2 до номинального значения частоты входного сигнала.

Чувствительньй элемент 4 определяет моменты изменения разности фаз входного сигнала и сигнала с распределителя 3 импульсов и формирует потенциал, указьшающий какой сигнал входной или с распределителя 3 импульсов имеет большую частоту. Как только чувствительный элемент 4 обнаруживает момент изменения разности фаз, то

fO

89122

формируется сигнал, переписывающий состояние счетчика 23 в регистр 24.

Таким образом, счетчик 23 просчитывает количество импульсов с распределителя 3 импульсов между моментами изменения разности фаз входного сигнала и сигнала с распределителя 3 импульсов 3. В момент изменения разности фаз в регистр 24 переписывается значение двоичного кода, поделенное на число градаций периода входного сигнала. Поскольку управляемый делитель 25 фазируется сигналом с чувствительного элемента 4, то фаза сигнала на выходе управляемого делителя 25 поддерживается близкой к фазе входного сигнала, второй 1)-триггер 21 и второй элемент ИЛИ 22 предназначены для отключения чувствительного элемента 4 сразу после момента определения момента изменения разности фаз.

f5

20

Такое отключение необходимо для

устранения ложного срабатывания чув- ствительного элемента 4, когда фазы сравниваемых сигналов очень близки.

Устройство для автоматической подстройки частоты работает следующим образом.

Пусть вначале входной сигнал (фиг,2в) опережает импульсы с первого (фиг.2а) и второго (фиг.26) выходов распределителя 3 импульсов, однако в процессе продолжения колебаний, так как входной сигнал с сигналы с распределителя 4 импульсов и, например

т..

пТ где Т„ - период образующей

ВХ

0

5

0

5

частоты входного сигнала, п - коэффициент деления первого дополнительного счетчика 1, Т - период сигнала генератора 1, произойдет перемещение вход- . ного сигнала по отношению к сигналу распределителя 3 импульсов и наступит момент, когда входной сигнал будет отставать от сигнала с первого выхода распределителя 3 импульсов, но,опережая сигнал с второго его выхода - это и будет моментом изменения разности

фаз. I

На фиг.З показан случай, когда входной сигнал (фиг.Зв) запаздывает по отношению к сигналу с первого выхода распределителя 3 импульсов (фиг.За) и опережает сигнал с второго выхода распределителя 3 импульсов (фиг.36). Момент, когда входной сигнал опередит оба сигнала, - это и будет моментом изменения разности фаз .

31

Входной сигнал поступает на информационные управляющие входы третьего 5 и пятого -7 D-триггеров, на тактовы входы которых поступают сигналы с первого и второго вькодов распредели теля 3 импульсов соответственно.. Состояние этих триггеров определяется взаимным расположением импульсов, поступающих на его входы. Сигналом с четвертого выхода распределителя 3 импульсов состояния этих D-триггеров переписываются в четвертый и шестой Б-триггеры соответственно, однако, - если состояния третьего 5 и четверто

го 7 D-триггеров 00, что происходи в моменты отсутствия входного сигнала, который представлен кодовой последовательностью, то с помощью элемента И-НЕ 9 и третьего элемента И 1 сигнал перезаписи не формируется и состояния четвертого 6 и шестого 8 D-триггеров остаются в прежнем состоянии. На четвертом 11 и пятом 12 эле мейтах И анализируется направление перехода состояний В-триггеров 5 и 7 и D-триггеров 6 и 8, если D-триггеры 6 и 8 находятся в состоянии 11, а D-триггеры 5 и 7 - в состоянии 01, это означает момент изменения разности фаз и тот факт, что Т пТ. Это состояние Дешифрируется четвертым элементом И 11 и по сигналу с третьего выхода распределителя 3 импульсов записывается в седьмой D-триггер 13,

пepexo из состояния 01 в состояние35 повышения точности при одновременном 11 дешифрируется пятым элементом И 12 и записывается в восьмой D-триггер 14. Срабатывания этих D-триггеупрощении, в него введены последовательно соединенные первьй дополни- тельньй счетчик, вход которого подключен к выходу генератора, и распределитель импул сов, последовательно соединенные первый элемент ЮТИ и первый элемент И, первый D-триггер, управляющий вход которого подключен к выходу первого элемента ИЛИ, второй элемент И, первый вход которого подключен к выходу первого D-триггера, элемент НЕ, выход которого подключен к вторым входам первого и второго элементов И, второй D-триггер, управляющий вход которого является .входом для подачи сигнала логической единицы, тактовый вход соединен с инверсным выходом первого D-триггера и второй элемент ИЛИ, входы которого соединены с инверсными выходами первого и второго D-триггеров соответственно, при этом чувствительный эле

ров - есть момент изменения разности фаз, причем срабатывание седьмого Dтриггера 11 означает, что Т пТ.,

.вх г

а срабатывание восьмого D-триггера

14 - Т пТ. . Вькодные сигналы этих D-триггеров устанавливают триггер 15 знака, указьшающий результат сравнения частот.

С помощью первого D-триггера 20, первого 17 и второго 18 элементов И и элемента НЕ 19 формируются два. сдвинутых во времени импульса. При этом импульсом с выхода первого элемента И 17 состояние счетчика 23 перепишется в регистр 24, а импульсом с выхода второго элемента И 18 содержимое счетчика обнулится и начнется новый цикл. Импульсом с выхода первого элемента И 17 содержимое регистра

24 постоянно сравнивается в блоке 27 мент вьшолнен в виде последовательно

сравнения с состоянием второго дополнительного счетчика 26. Как только коды сравняются, срабатывает блок 27

5

-5 0

5

сравнения, шестой элемент И 28 и производится сдвиг сигнала 1 s реверсивном регистре 30. Этот же сигнал сбрасывает содержимое второго дополнительного счетчика для начала отсчета нового момента времени для внесе- ния последующей коррекции. Направление сдвига l в реверсивном регистре 30 определяется сигналом с выхода триггера 15 знака, а первоначальная установка 1 в реверсивный регистр

30производится сигналом с выхода первого элемента И 17, потенциалы с выхода реверсивного регистра 30 поступают на адресные входы мультиплексора 25 и переключают отводы линии

31задержки, что приводит к тому, что фаза сигнала на выходе управляемого делителя 25 близка к фазе входного сигнала.

Формула изобретения

Устройство для автоматической подстройки частоты, содержащее последовательно соединенные генератор и управляемый делитель частоты, а также чувствительный элемент, вход которого является входом устройства, счетчик, регистр и триггер знака, отличающееся тем, что, с целью

повышения точности при одновременном

упрощении, в него введены последовательно соединенные первьй дополни- тельньй счетчик, вход которого подключен к выходу генератора, и распределитель импул сов, последовательно соединенные первый элемент ЮТИ и первый элемент И, первый D-триггер, управляющий вход которого подключен к выходу первого элемента ИЛИ, второй элемент И, первый вход которого подключен к выходу первого D-триггера, элемент НЕ, выход которого подключен к вторым входам первого и второго элементов И, второй D-триггер, управляющий вход которого является .входом для подачи сигнала логической единицы, тактовый вход соединен с инверсным выходом первого D-триггера и второй элемент ИЛИ, входы которого соединены с инверсными выходами первого и второго D-триггеров соответственно, при этом чувствительный эле5129

соединенных третьего D-триггера, управляющий вход которого является входом чувствительного элемента, и четвертого D-триггера, последовательно соединенных пятого D-триггера, управляющий вход которого соединен с входом устройства, и шестого D-триггера, последовательно соединенных элемента И-НЕ, входы которого подключены к инверсным выходам третьего и четвертого D-триггеров соответственно, и третьего элемента И, четвертого элемента И, входы которого подключены к выходу шестого D-триггера, четвертого D-триггера, пятого D-триггера и третьего D-триг- гера соответственно, пятого элемента И, входы которого подключены к инверсному выходу четвертого D-триггера, к выходу шестого D-триггера, к выходу пятого D-триггера и выходу третьего D-триггера соотв тственно, седьмого D-триггера, управляющий вход которого соединен с выходом четвертого элемента И, и восьмого D-триггера, зшравля- ющий вход которого соединен с выходом пятого элемента И, выходы седьмого и восьмого D-триггеров являются первым и вторьм выходами чувствительного элемента соответственно, тактовые входы третьего, пятого и седьмого с восьмым D-триггеров подключены соответственно к первому, второму и третьему выходам распределителя импульсов, четвертый выход которого подключен к второму входу третьего элемента И, входы сброса седьмого и восьмого D-триггеров подключены к выходу вто- рого элемента ШШ, управляемый дели

5

5

0

тель частоты вьтолнен в виде линии задержки, вход которой является входом управляемого делителя частоты, отводы которой подключены к информа- ционньЫ входам мультиплексора, выход которого является выходом управляемого делителя частоты, последовательно соединенных второго дополнительного счетчика, блока сравнения, шестого элемента И и реверсивного регистра сдвига, выходы которого подключены к соответствующим входам адреса мультиплексора, и третьего элемента ИЛИ, первьй вход которого подключен к выходу шестого элемента И, а выход - к входу сброса второго дополнительного счетчика, причем тактовые входы второго дополнительного счетчика и счетчика подключены к четвертому выходу распределителя импульсов, второй вход третьего элемента ИЛИ, вход сброса реверсивного регистра сдвига и тактовый вход регистра подключены к выходу первого элемента И, вход знака реверсивного регистра сдвига подключен к выходу триггера знака, установочный вход и вход сброса которого подключены к первым и вторым выходам чувствительного элемента, второй вход блока сравнения подключен к выходу регистра, вход сброса счетчика подключен к выходу второго элемента И, выходы счетчика подключены к управляющим входам регистра, а вход элемента НЕ и тактовый вход первого J) -триггё ра: подключены к третьему выходу распределителя импУ1 ь- сов.

t3

Редактор А.Козориз

Составитель С.Даниэлян

Техред М.Ходакнч Корректор Л.Пилипенко

Заказ 898/59Тираж 902 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

t3 to «

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения отклонения частоты от номинального значения | 1985 |

|

SU1311027A1 |

| Устройство для измерения временных интервалов | 1982 |

|

SU1034009A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Двухступенчатый параллельно-последовательный регенератор | 1985 |

|

SU1246394A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ | 1989 |

|

RU2042261C1 |

| Устройство для измерения параметров вибрации | 1990 |

|

SU1783318A1 |

| Цифровой фазометр | 1988 |

|

SU1553918A2 |

| Устройство автоматической стабилизации амплитуды видеосигнала | 1990 |

|

SU1757124A1 |

| Вычислительное устройство | 1986 |

|

SU1437858A1 |

| Следящий измеритель частоты | 1985 |

|

SU1298675A1 |

Изобретение может быть использовано в аппаратуре систем связи. Цель изобретения - повышение точности при одновременном утфощении. Устройство содержит генератор 1, чувствительный элемент (Э) 4, выполненный в виде D- триггеров 5-8, 13, 14, Э И-НЕ 9 и Э И 10-12, а также триггер 15 знака, счетчик 23, регистр 24, управляемый делитель 25 частоты, выполненный в виде счетчика 26, блока 27 сравнения, Э И 28, Э ИЛИ 29, реверсивного регистра 30 сдвига, линии 31 задержки и мультиплексора 32. В устройство введены счетчик 2, распределитель 3 импульсов, Э ИЛИ 16 и 22, ЭЙ 17 и 18, Э НЕ 19, D-триггеры 20 и 21. Входной сигнал представляет кодовую последовательность или регулярный сигнал частоты, примерно кратной частоте генератора 1. Длительность сигнала должна превышать четверть периода образующей его частоты и не может быть больше 3/4 того же периода. 3 ил. (Л

| Устройство автоматической подстройки частоты | 1979 |

|

SU873381A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-03-23—Публикация

1984-09-19—Подача