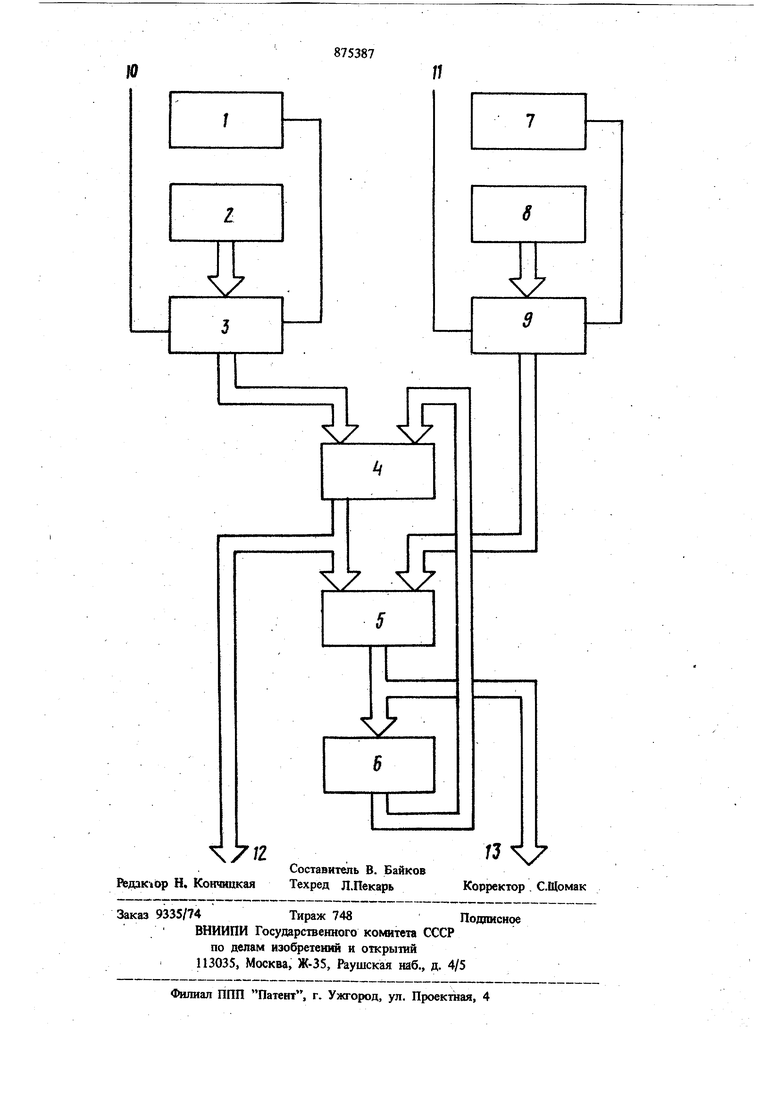

(54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ БАЗОВОЙ ОПЕРАЦИИ БЫСТЮГО ПРЕОБРАЗОВАНИЯ Изобретение относится к автоматике и вычи лительной технике и может быть использовано дня построения процессоров быстрого преобразования Фурье (БПФ) и других устройств цифровой вычислительной техники, в которьтх необходимо выполнять операции вида (1): PI А « (±ВС ± DS) Ра А - (±ВС ± DS) Известно арифметическое устройство KOM&Iнацирнного типа, используемое для вьшолнения операций БПФ вида (1), содержащее четыре матричных умножителя и четыре суммато;1а {1} Недостатком этого устройства являются большие аппаратурные затраты, обусловленные тем, что количество оборудования, необходимого дпя построения данного устройства, пропорци- . (жально квадрату числа разрядов обрабатьюаемых слов. Наиболее близким техническим решением к предлагаемому является арифметическое устройство дпя базовой операции быстрого преобразования Фурье, содержащее два статических регистра, два регистра сдвига, два блока преобразования прямого кода в инверсный, KOMUIФУРЬЕнационный и накапливающий сумматоры, а так,же элемента И, ИЛИ 2. Недостатком известного устройства является низкое быстродействие, поскольку базовая операция БПФ вида (1) выполняется в нем в два зтапа через операцию вида (2): (± ЕС ± bS) Цель изобретения - повышение быстродействия устрсжства. Поставленная цель достигается тем, что арифметическое устройство дпя базовой операции быстрого преобразования Фурье, содержащее два регистра, два регистра сдвига, два блока 1феобразоваш1я прямого кода в инверсный, первый сумматор, накапливающий сумматор, причем выход первого и выход второго регистров подключены соответственно к информационным входам первого и второго блоков преобразования прямого кода в инверсный, управляющие входы которых являются управляющими входами устршства, а входа управления выдачей информации первого и второго блоков преобразования прямого кода в инверсный подюпичены к выходам первого и второго регистров 38 сдвига соответственно, выход накапливающего I сумматора лодключен к первому входу первого сумматора, выход которого является первым выходом устройства, содержит второй сумматор, выход которого является вторым выходом устройства и подкйючен ко входу накапливающе го сумматора, второй вход первого сумматора подключен к выходу первого блока преобразговашш прямого кода в инверсный, выход первого сумматора подключен к первому, а выход второго блока преобразования прямого кода в инверсный - ко второму входу второго сумматора. На чертеже представлеиа функциональная схема арифметического устройства для базовой операции быстрого преобразования Фурье. Схема содержит регистр 1 сдвига (первого мнояштеля), регистр 2 (первого множимого), Ёлок 3 преобразования прямого кода в инверсный, сумматоры 4 и S (комбинационного типа) накапливающий сумматор 6, регистр 7 сдвига (второго множителя), регистр 8 (второго множимого) , блок преобразовашш прямого кода в инверсный, управляющие входы 10 и 11, выходы 12 и 13. Функция каждого из блоков 3 и 9 определяется следующим образом. При нулевом сигнале на соответствующем управлякндем входе 10 или 11 выходной код регистра 2 или 8 передается на выход блока 3 или 9 без изменения . При едашичном управляющем сигнале осуществляется поразрядная инверсия кода. Передача кода через блок 3 или 9 разрешена, если в выходном разряде регистра сдвига 1 или 7 записана единица, в противном случае на выходе блока 3 или 9 формируется нулевой код. Предлагаемое арифметическое устройство работает с действительными числами, представлен ными в прямом или дополнительном двоичном коде. Два идентичны) устройства составляют комплексное арифметическое устройство процессора быстрого преобразования Фурье. Множимые В и О, а также число А представлены в модифицировакном дополнительном коде, т.е. знак числа записан в двух старщих разрядах. Множители С и S представлены в дополнительном коде и в каждом из них имеется еще один служебный разряд, расположенный левее знакового бита. Наличие единицы в служебном разряде говорит о том, что в операции (1) будет участвовать число А, в противном случае вьшолняется операция (2). Все числа, участвующие в опарации (1), по модулю меньше единицы и представлены в кодах с фиксированной запятой после знака. Перед началом вычислений производится одновременная загрузка операндов в регистры 1, 2, 7 и 8, и на управляющие входы устройства 10 и 11 поступают логические нули. Разряды множимых В и D из регистров 2 к 8, логически умноженные на значения битов множителей из регистров 1 и 7, передаются на входы сумматоров без инвертирования (здесь рассматривается работа, когда вычисляется выражение с верхними знаками). На входы переносов сумматоров 4 и 5 поступают логические нули. Одновременно с загрузкой операндов накапливающий сумматор 6 сбрасывается в нуль. На выходе сумматора 5 установится сумма содержимого накапливающего сумматора 6, частного произведения первого множимого и частного произведения второго множимого. Полученная сумма записывается в накапливающий, сумматор и сдвигается на один разряд вправо (в сторону младщих разрядов). Одновременно с этим производятся сдвиги на один разряд множителей вправо. Эти операции повторяются (М-1) раз, где М - число разрядов множителя. На М-м такте множимые В и D умножаются на значения знаковых битов множителей С и S. Поскольку устройство работает с дополнительными кодами, то в зтом такте из содержимого Накапливающего сумматора необходимо вычесть значение частных произведений множимых на знаки лягожителей, т.е. пронзвести коррекции произведений., Для зтого на М-м такте на управляющие входы устройства 10 и 11 поступают логические единицы, а на входы переносов сумматоров 4 и 5 - знаки соответствующих множителей. В момент записи скорректированного результата в накапливающий сумматор в регистр 2 первого множимого загружается число А, а в регистр 8 второго множимого числа 2А. Одновременно сдвигается содержимое регистров 1 и 7. При этом на входы управления выдачей информации блоков 9 поступают служебные ты, равные логическим единицам. На управляющий вход блока 3 подается логический нуль, а второго 9 - логическая единица. Одновременно на вход переноса первого сумматора 4 подается логический нуль, а второго 5 - логическая единица. На выходе первого сумматора 4 получается алгебраическая сумма числа А с содержанием накапливающего сумматора 6, т.е. Р, А + (ВС + DS) а на выходе второго сумматора 5 разность числа PI и числа 2А, Р А + (ВС + DS) + f 2А + 2 А -f (ВС + DS), представляющая собой поразрядную инверсию числа Р 2.

Время выполнейия операций (1) в предпага емом устройстве (Ti) и в известном устройстве (Tj) определяется выражением TI (М + 4) (N + 1) г Тг (М + 3) (N + 1) т где М, N - разрядность множителей и множимых;т - время получения суммы на один

разряд.

Относительный выигрыш в быстродействии - . выражением

llL - Ч

Tf

Формула изобретения

Арифметическое устройство для базовой операции быстрого преобразования Фурье, содержащее два регистра, два регистра сдвига, два блока преобразования прямого кода в инверсный первый сумматор, накапливающий сумматор, причем выход первого .и выход второго регистров подключены соответственно к информационным входам первого и второго блоков преобразования прямого кода в инверсный, управляющие входы которых являются управляющиМИ входами устройства, а входы управления выдачей информации первого и второго блоков преобразования прямого кода в инверсный подключены к выходам первого и второго регистров сдвига соответственно, выход иакапливакнцего сумматора подключен к первому входу первого сумматора, выход которого является первым выходом устройства, отличающееся тем, что, с целью повыщения быстродействия, оно содержит второй сумматор, вы0ход которого является вторым выходом устройства и подключен ко входу накапливающего сумматора, второй вход первого сумматора подключен к выходу первого блока преобразования прямого КОД9 в инверсный, выход

s первого сумматора подаглюченк первому, а выход второго блока преобразования прямого кода в инверсный - ко второму входу второ-; го сумматора.

Источники информации,

0 принятые во внимание при экспертизе

1.Рабинер Л. и Гаулд Б. Теория и применение цифровой обработки сигналов. М., Мир, 1978, с. 707, фиг. 11.5.

2.Авторское свидетельство СССР № 553613, кл. G 06 F 7/38, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Устройство для умножения п-разрядных чисел | 1978 |

|

SU734683A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Арифметическое устройство | 2016 |

|

RU2632411C1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

| Множительно-сдвиговое устройство | 1978 |

|

SU805307A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

iLJH

1

7 X

F

Авторы

Даты

1981-10-23—Публикация

1980-02-04—Подача