11287

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах центральных процессоров.

Целью изобретения является расши- 5 рение функциональных возможностей за счет нормализации чисел.

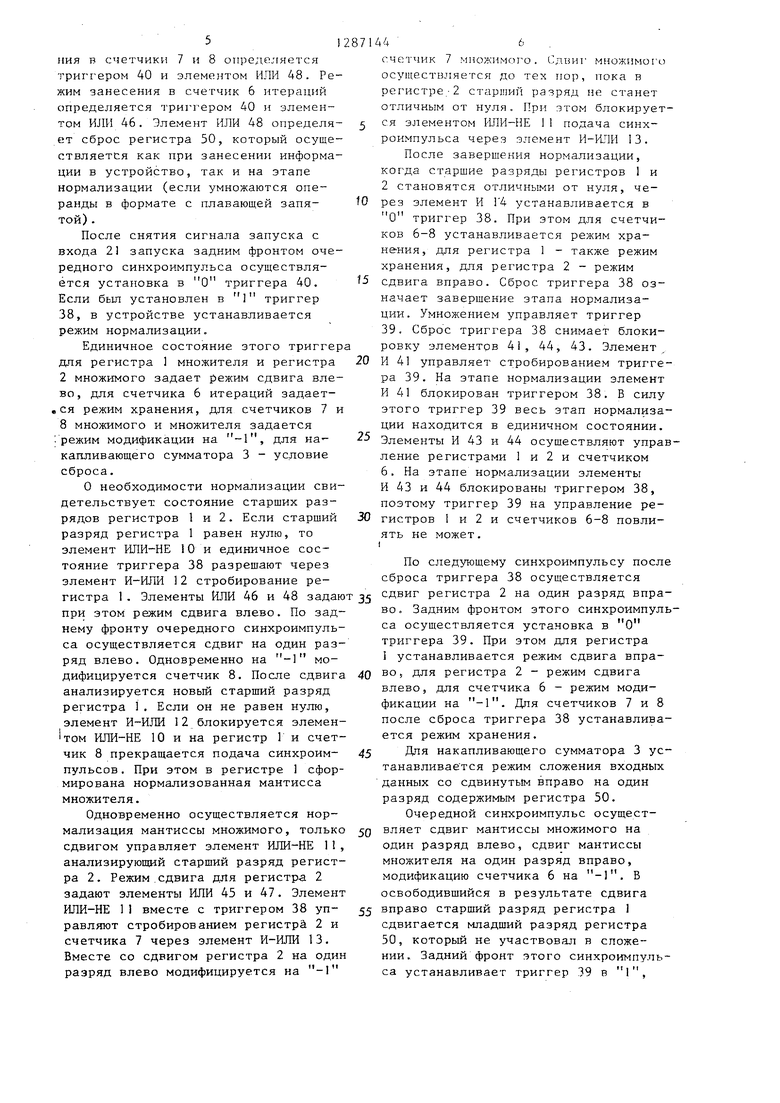

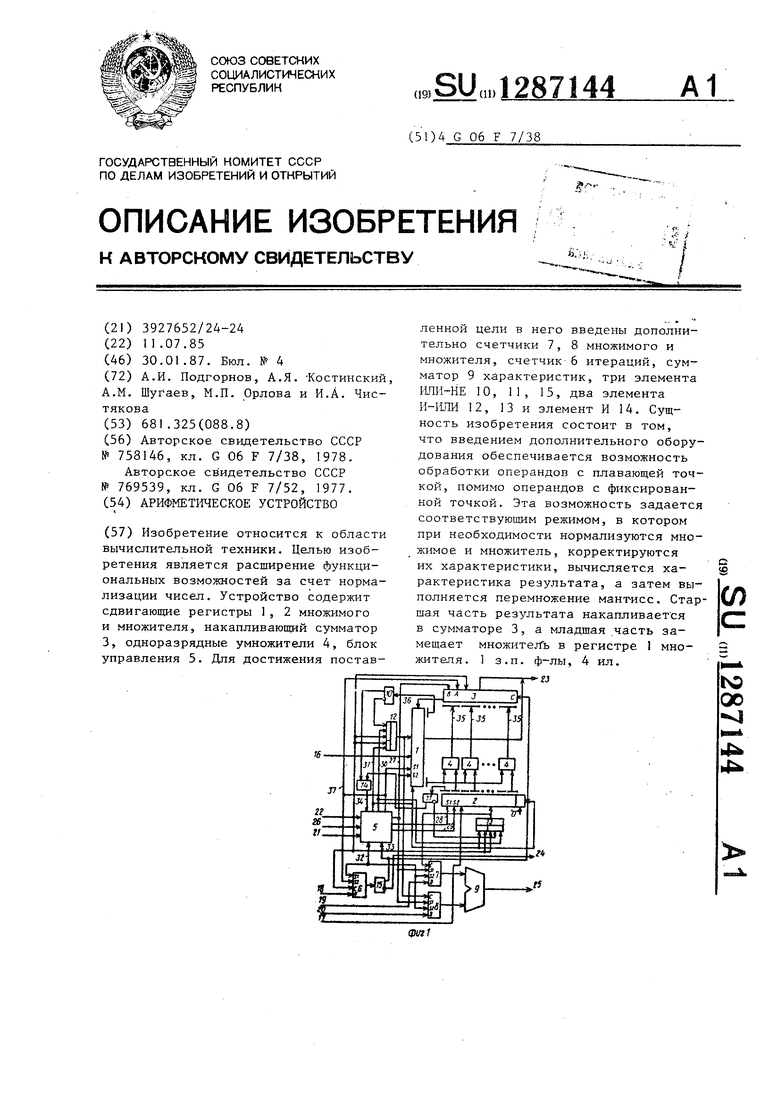

На фиг. 1 изображена схема устройства для умножения данных; на

Ю

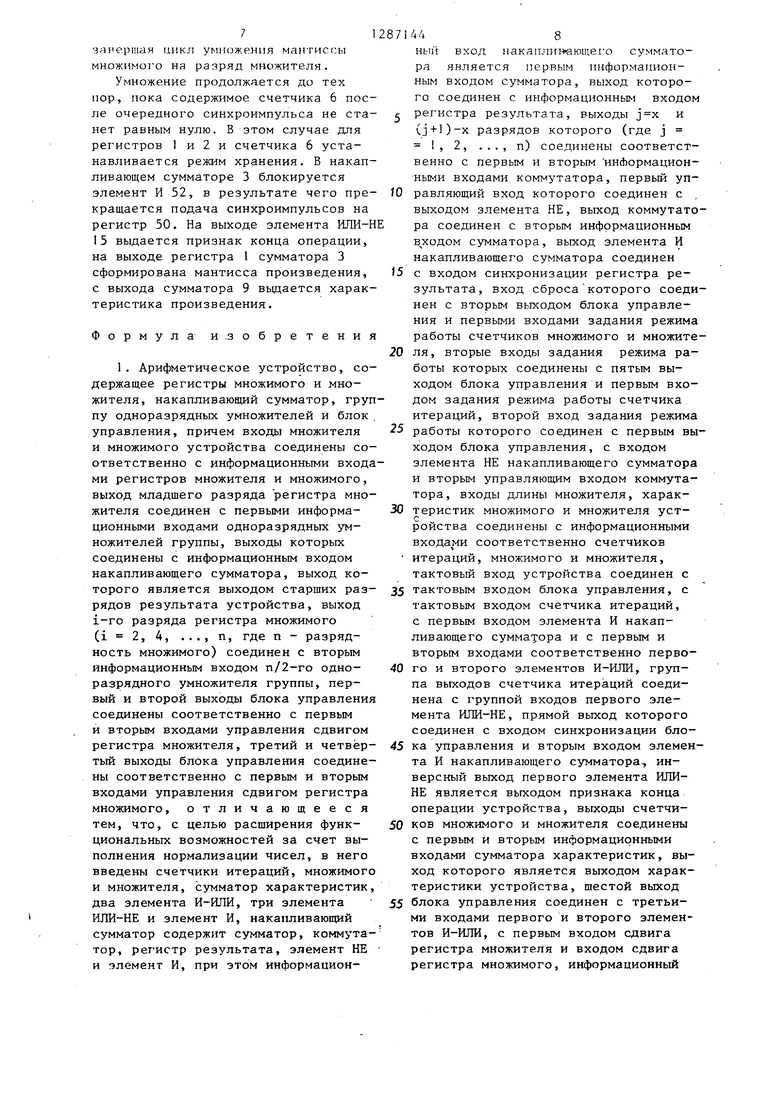

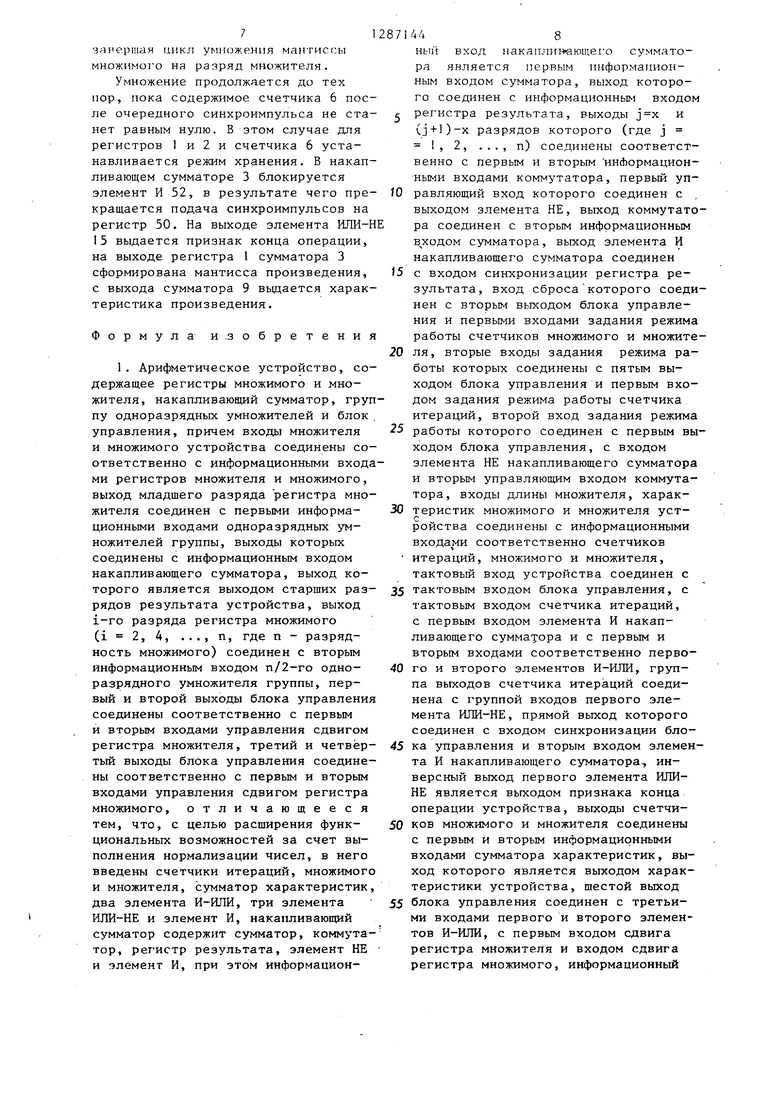

фиг. 2 - схема блока управления;

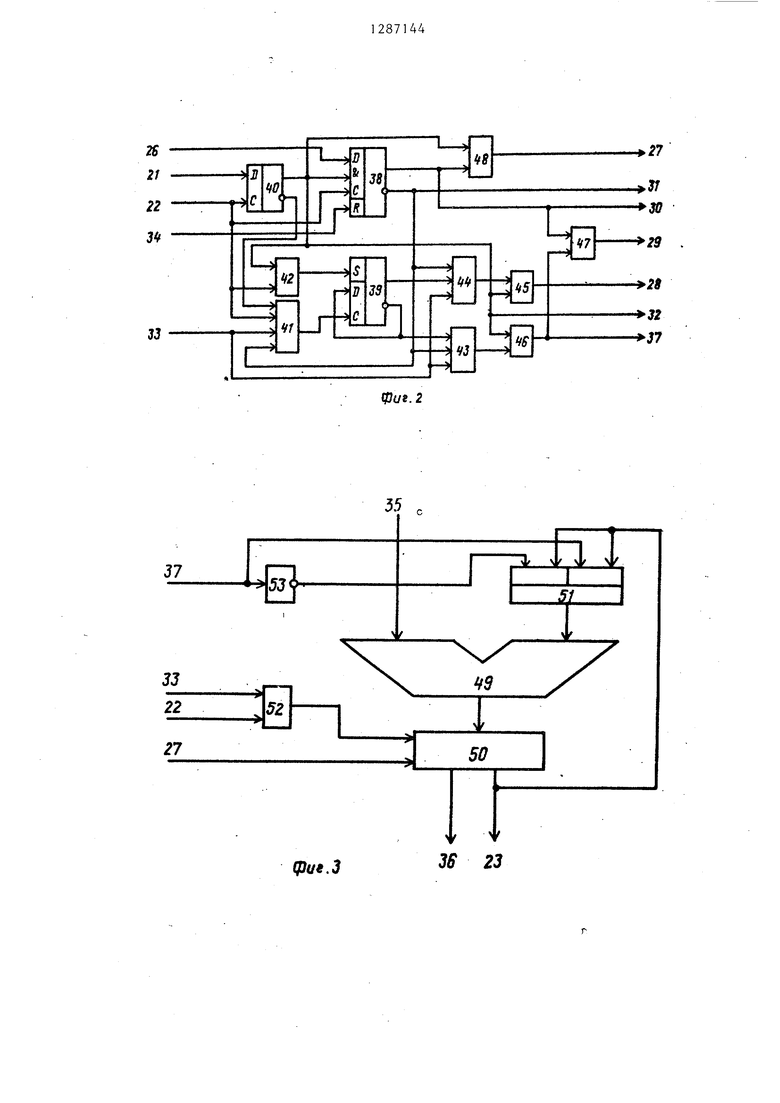

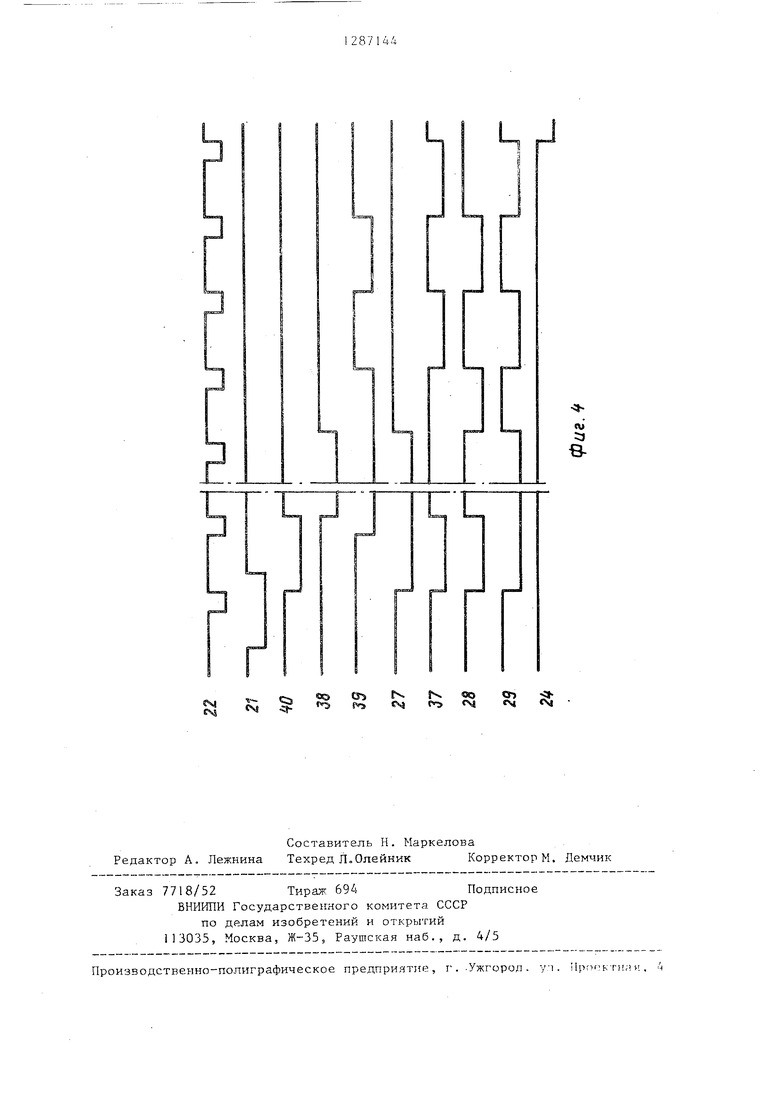

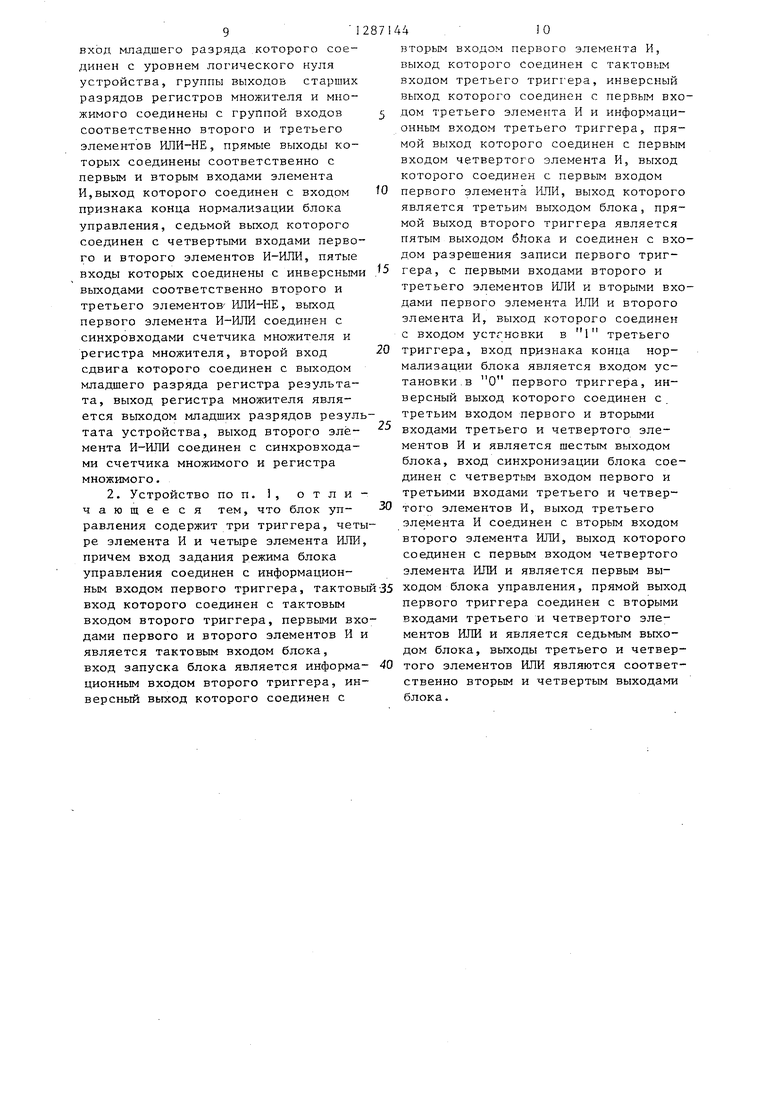

на фиг. 3,- накапливающий сумматор; на фиг. 4 - временные диаграммы работы арифметического устройства.

Арифметическое устройство (фиг.1) содержит регистр 1 множителя, регист 2 множимого, накапливающий сумматор

3,группу одноразрядных умножителей

4,блок 5 управления, счетчик 6 итераций, счетчик 7 множимого, счетчик 8 множителя, сумматор 9 характеристик, второй элемент ЙЛИ-НЕ 10, третий элемент ИЛИ-НЕ 11, первый эле.мент И-ИЛИ 12, второй элемент 13, элемент И 14, первый элемент ИЛИ-НЕ 15,. вход 16 множителя устройства, вход 17 множимого устройства, вход 18 длины множителя устройства, вход 19 характеристики множимого устройства, вход 20 характеристики мно- жителя устройства, вход 21 запуска устройства, тактовый вход 22 устройства, выход 23 результата устройства выход 24 признака конца операции устройства, выход 25 характеристики устройства, вход 26 режима устройст- ва, второй, третий и четвертый выходы 27, 28 и 29 блока 5, седьмой, шестой и пятый выходы 30-32 блока

5,вход 33 синхронизации блока 5, вход 34 признака конца нормализации блока 5, выход 35 умножителя 4, выход 36 младшего разряда регистра, первый выход 37 блока 5.

Блок управления (фиг. 2) содержит первый, третий и второй триггеры 38-40, четыре элемента И 41-44 и четыре элемента ИЛИ 45 и 48.

Накапливающий сумматор (фиг. 3) содержит сумматор 49, регистр 50 результата, коммутатор 51, элемент И 52 и элемент НЕ 53.

Устройство умножает данные, представленные и формате с фиксированной и плавающей запятой. Формат данных определяется состоянием входа 26 режима.

Регистр 1 множителя и регистр 2 множимого предназначены для хране

5

15

0

5 -з

40

45

50

55

44 2

имя исходных операндов. Если данные представлены в формате с плавающей запятой, рег истры 1 и 2 содержат мантиссы множителя и множимого.

Счетчик 7 множимого и счетчик 8 множителя г редназначены для хранения характеристик множимого и множителя. Сумматор 9 формирует результирующую характеристику произведения.

При нормализации мантисс содержимое соответствующих им счетчиков

7и 8 модифицируется. Нормализация мантиссы осуществляется до тех пор, пока ее старший разряд не станет отличным от нуля. Нормализация выполняется путем сдвига мантиссы влево. Если старший разряд мантиссы не равен нулю, то через соответ- ствуюш;ий элемент ИЛИ-НЕ (для множителя - элемент ИЛИ-НЕ 10 и для множимого - элемент ИЛИ-НЕ 11) блокируется соответствующий элемент И-ИЛИ, определяющий синхронизацию регистров I и 2 (для регистра 1 множителя - элемент И-ИЛИ 12, для регистра 2 множимого - элемент И-ИЛИ

13). При этом изменение соответствующей характеристики также прекращается. Когда нормализация множимого и множителя оказывается завершенной, то элементы ИЛИ-НЕ 10 и 11 через элемент И 14 осуществляют сброс режима нормализации в устройстве. При нормализации мантисс.ы множимого в регистре 2 множимого в освобождающиеся разряды вдвигается содержимое (п+1)-го разряда регистра 2 множимого, в который при занесении множимого записываются нули. При нормализации в (п+1)-й разряд регистра 2 множимого и в п-й разряд регистра 1 множителя вдвигаются нули.

Одноразрядные умножители 4 представляют собой ПЗУ, формирующие двухразрядное произведение.

Если регистр 2 множимого разбить на п/2 двухразрядных регистров, то выход младшего разряда каждого из этих регистров соединен с соответствующим одноразрядным умножителем 4.,

8общем случае, разряд мантиссы множимого и множителя содержит К бит (например, ). Исходя из этого

на выходе одноразрядного умножителя формируется 2К-разрядное произведение с

Умножение операндов осуществляется за п циклов, каждый длительностью

12871

в-два такта. В первом такте осуществляется умножение разряда множителя на младшие разряды двухразрядных регистров. После этого осуществляется сдвиг мантиссы множимого и в ре- с гистре 2 множимого на один разряд вправо. При этом разряд п мантиссы множимого вдвигается в разряд п+ регистра 2 множимого. На втором шаге в результате сдвига на входы од- Ю норазрядных умножителей 4 подаются старшие разряды двухразрядных регистров, содержащих мантиссу множимого. Новое произведение, как и пре- дьщущее, складывается на накапливаю- 15 щем сумматоре 3 с содержимым регистра 50. После этого осуществляется сдвиг мантиссы множимого влево на один разряд, а также сдвиг вправо мантиссы множителя на один разряд. 20 При этом в регистр 1 множителя вдвигается младший разряд произведения из накапливающего сумматора 3.

Счетчик 6 итераций определяет число циклов умножения. Эта величи- 25 на задается разрядностью мантиссы множителя. В каждом цикле содержимое счетчика 6 итераций модифицируется на -1. Когда счетчик 6 итераций обнулится, элемент ИЛИ-НЕ 15 блоки- 30 рует блок 5 управления, а на выход 24 выдается признак конца операции умножения.

Регистр 1 множителя, регистр 2 35 множимого, накапливающий сумматор 3, счетчик 6 итераций, счетчик 7 мно- жимого, счетчик 8 множителя, триггеры 38-40 являются двухтактными и переключаются по заднему фронту 40 синхроимпульса, поступающего на вход 22.

Режимы работы регистров 1 и 2 множителя и множимого, накапливающего сумматора 3, счетчиков 6-8 итераций, 45 множимого и множителя задаются блоком 5 управления и определяются состояниями триггеров 38-40.

Регистр 1 множителя и регистр 2 множимого имеют следующие режимы 50 работы: - хранение; S1S2 01 - сдвиг влево; - сдвиг вправо; - занесение, счетчик 6 итераций, счетчик 7 множимого и счетчик 8 множителя - 55 хранение; - занесение; - модификация на -1, а накапливающий сумматор 3 - - хранение: - сброс; 44

сложение без перекосов; - сложение с перекосом; X - состояние не определено.

Накапливание произведения осуществляется на регистре 50. Когда содержимое регистра 50 складывается с произведением, образованным на первом такте (при умножении разряда множителя на младшие разряды двухразрядных регистров, содержащих мантиссу множимого), на второй вход сумматора подаются п младших разрядов регистра 50 (разряды 2-п+1). На следующем такте умножения на второй вход с т матора 49 подаются п старших разрядов регистра 50. При этом младший разряд регистра 50 (разряд п+1) на вход сумматора 49 не подается. В его позиции поступает п-й разряд регистра 50, т.е. на вход сумматора 49 в этом случае подается сдвинутое вправо на один разряд содержимое регистра 50. На самый старший входной разряд сумматора 49 при этом подается первый разряд регистра 50.

Устройство для умножения данных работает следующим образом (фиг i. 4),

По сигналу запуска, поступающему на вход 21 запуска, задним фронтом очередного синхроимпульса устанавливается в 1 второй триггер 40. После установки этого триггера через элементы ИЛИ 45-48 устанавливаются режимы занесения для регистра 1 множителя и регистра 2 множимого. Единичное состояние триггера 40 разрешает установку триггера 38, а также триггера 39 через элемент И 42. Следующий синхроимпульс устанавливает в 1 триггер 39, а также в зависимости от входа 26 режима - триггер 38. Если триггер 40 определяет запуск устройства, то триггер 38 определяет наличие режима нормализации, а триггер 39 управляет, умножением. Этот синхроимпульс осуществляет занесение множителя (или его мантиссы дд1я операнда с плавающей запятой) в регистр 1 множителя, характеристики множителя (для операнда с плавающей запятой) в счетчик 8 множителя, множимого (или его мантиссы для операнда с плавающей запятой) в регистр 2 множимого, характеристики множимого (для операнда с плавающей запятой) в счетчик 7 множимого. В счетчик 6 итераций заносится число циклов. Режим занесе512871

ИЯ в счетчики 7 и 8 определяется риггером 40 и элементом ИЛИ 48. Реим занесения в счетчик 6 итераций пределяется триггером 40 и элементом ИЛИ 46. Элемент ИЛИ 48 определи- 5 т сброс регистра 50, который осуществляется как при занесении информации в устройство, так и на этапе нормализации (если умножаются операнды в формате с плавающей запя- 0 той).

После снятия сигнала запуска с входа 2 запуска задним фронтом очередного синхроимпульса осуществляется установка в О триггера 40. Если был установлен в 1 триггер 38, в устройстве устанавливается режим нормализации.

Единичное состояние зтого триггера для регистра 1 множителя и регистра 20 2 множимого задает режим сдвига влево, для счетчика 6 итераций задает- ся режим хранения, для счетчиков 7 и 8 множимого и множителя задается режим модификации на -1, для на - 25 капливающего сумматора 3 - условие сброса.

О необходимости нормализации свидетельствует состояние старших разрядов регистров 1 и 2. Если старший 30 разряд регистра 1 равен нулю, то элемент ИЛИ-НЕ 10 и единичное состояние триггера 38 разрешают через элемент И-ИЛИ 12 стробирование регистра 1. Элементы ИЛИ 46 и 48 задают 35 при этом режим сдвига влево. По заднему фронту очередного синхроимпульса осуществляется сдвиг на один разряд влево. Одновременно на - модифицируется счетчик 8. После сдвига 40 анализируется новый старщий разряд регистра 1. Если он не равен нулю, элемент И-ИЛИ 12 блокируется элемен- ITOM ИЛИ-НЕ 10 и на регистр Г и счетчик 8 прекращается подача синхроим- 45

пульсов. При этом в регистре 1 сформирована нормализованная мантисса

множителя.

Одновременно осуществляется нормализация мантиссы множимого, только 50 сдвигом управляет элемент ИЛИ-НЕ 11, анализирующий старщий разряд регистра 2. Режим.сдвига для регистра 2 задают элементы ИЛИ 45 и 47. Элемент ИЛИ-НЕ 11 вместе с триггером 38 уп- 55 равляют стробированием регистра 2 и счетчика 7 через элемент И-ИЛИ 13. Вместе со сдвигом регистра 2 на один разряд влево модифицируется на -1

44 6

счетчик 7 множимого. Сдвиг множимого осуществляется до тех нор, нока в регистре-2 старший разряд не станет отличным от нуля. При этом блокируется элементом ИЛИ-НЕ 11 нодача синхроимпульса через элемент И-ИЛИ 13.

После завершения нормализации, когда старшие разряды регистров 1 и 2 становятся отличными от нуля, через элемент И Г4 устанавливается в О триггер 38. При этом для счетчиков 6-8 устанавливается режим хранения, для регистра 1 - также режим хранения, для регистра 2 - режим сдвига вправо. Сброс триггера 38 означает заверщение этапа нормализации. Умножением управляет триггер 39. Сброс триггера 38 снимает блокировку элементов 4, 44, 43. Элемент, И 41 управляет стробированием триггера 39. На этапе нормализации элемент И 41 блокирован триггером 38. В силу этого триггер 39 весь этап нормализации находится в единичном состоянии. Элементы И 43 и 44 осуществляют упраление регистрами 1 и 2 и счетчиком 6. На этапе нормализации элементы И 43 и 44 блокированы триггером 38, поэтому триггер 39 на управление регистров 1 и 2 и счетчиков 6-8 повлиять не может. I

По следующему синхроимпульсу посл сброса триггера 38 осуществляется сдвиг регистра 2 на один разряд вправо. Задним фронтом этого синхроимпулса осуществляется установка в О триггера 39. При этом для регистра 1 устанавливается режим сдвига вправо, для регистра 2 - режим сдвига влево, для счетчика 6 - режим модификации на -1. Для счетчиков 7 и 8 после сброса триггера 38 устанавливается режим хранения.

Для накапливающего сумматора 3 ус танавливае тся режим сложения входных данных со сдвинутым вправо на один разряд содержимым регистра 50.

Очередной синхроимпульс осуществляет сдвиг мантиссы множимого на один разряд влево, сдвиг мантиссы множителя на один разряд вправо, модификацию счетчика 6 на -1. В освободившийся в результате сдвига вправо старщий разряд регистра I сдвигается младший разряд регистра 50, который не участвовал в сложении. Задний фронт этого синхроимпульса устанавливает триггер 39 в 1,

712

запертая цмкл умножения мантисс:ы множимо1 о на разряд множителя.

Умножение продолжается до тех пор, пока содержимое счетчика 6 после очередного синхроимпульса не ста- нет равным нулю. В этом случае для регистров 1 и 2 и счетчика 6 устанавливается режим хранения. В накапливающем сумматоре 3 блокируется элемент И 52, в результате чего пре- кращается подача синхроимпульсов на регистр 50, На выходе элемента ИЛИ-НЕ 15 выдается признак конца операции, на выходе регистра 1 сумматора 3 сформирована мантисса произведения, с выхода сумматора 9 выдается характеристика произведения.

Формула и.3 обретения

1. Арифметическое устройство, содержащее регистры множимого и множителя, накапливающий сумматор, группу одноразрядных умножителей и блок управления, причем входы множителя

и множимого устройства соединены соответственно с информационными входами регистров множителя и множимого, выход младшего разряда регистра множителя соединен с первыми информа- ционными входами одноразрядных умножителей группы, выходы которых соединены с информационным входом накапливающего сумматора, выход которого является выходом старших раз- рядов результата устройства, выход i-ro разряда регистра множимого (i 2, 4, ..., п, где п - разрядность множимого) соединен с вторым информационным входом п/2-го одно- разрядного умножителя группы, первый и второй выходы блока управления соединены соответственно с первым и вторым входами управления сдвигом регистра множителя, третий и четвёр- тый выходы блока управления соединены соответственно с первым и вторым входами управления сдвигом регистра множимого, отличающееся тем, что, с целью расширения функ- циональных возможностей за счет выполнения нормализации чисел, в него введены счетчики итераций, множимого и множителя, сумматор характеристик, два элемента И-ИЛИ, три элемента ИЛИ-НЕ и элемент И, накапливаюш 1й сумматор содержит сумматор, коммутатор, регистр результата, элемент НЕ и элемент И, при этом информацион

0 15

0

5

0 5 0 5 0 5

448

ный вход накапливающего сумматора является первым информационным входом сумматора, выход которого соединен с информационньи входом регистра результата, выходы и (j+)-x разрядов которого (где j 1, 2, ..., п) соединены соответственно с первым и вторым инАормацион- ными входами коммутатора, первый управляющий вход которого соединен с выходом элемента НЕ, выход коммутатора соединен с вторым информационным выходом сумматора, выход элемента И накапливающего сумматора соединен с входом синхронизации регистра результата, вход сброса которого соединен с вторым выходом блока управления и первыми входами задания режима работы счетчиков множимого и множителя, вторые входы задания режима работы которых соединены с пятым выходом блока управления и первым входом задания режима работы счетчика итераций, второй вход задания режима работы которого соединен с первым выходом блока управления, с входом элемента НЕ накапливающего сумматора и вторым управляющим входом коммутатора, входы длины множителя, характеристик множимого и множителя уст

ройства соединены с информационными входами соответственно счетчиков итераций, множимого и множителя, тактовый вход устройства соединен с тактовым входом блока управления, с тактовым входом счетчика итераций, с первым входом элемента И накапливающего сумматора и с первым и вторым входами соответственно первого и второго элементов И-ИЛИ, группа выходов счетчика итераций соединена с группой входов первого элемента ИЛИ-НЕ, прямой выход которого соединен с входом синхронизации блока управления и вторым входом элемента И накапливающего сумматора, инверсный выход первого элемента ШШ- НЕ является выходом признака конца операции устройства, выходы счетчиков множимого и множителя соединены с первым и вторым информационными входами сумматора характеристик, выход которого является выходом характеристики устройства, шестой выход блока управления соединен с третьими входами первого и второго элементов И-ШТИ, с первым входом сдвига регистра множителя и входом сдвига регистра множимого, информационный

вход младшего разряда которого соединен с уровнем логического нуля устройства, группы выходов старших разрядов регистров множителя и множимого соединены с группой входов соответственно второго и третьего элементов ИЛИ-НЕ, прямые выходы которых соединены соответственно с первым и вторым входами элемента И,выход которого соединен с входом признака конца нормализации блока управления, седьмой выход которого соединен с четвертыми входами первого и второго элементов И-ИЛИ, пятые входы которых соединены с инверсными выходами соответственно второго и третьего элементов ИЛИ-НЕ, выход первого элемента И-ИЛИ соединен с синхровходами счетчика множителя и регистра множителя, второй вход сдвига которого соединен с выходом младшего разряда регистра результата, выход регистра множителя является выходом младших разрядов результата устройства, выход второго элемента И-ИЛИ соединен с синхровходами счетчика множимого и регистра множимого,

2. Устройство по п. i, отличающее ся тем, что блок уп- равления содержит три триггера, четыре элемента И и четыре элемента ИЛИ, причем вход задания режима блока управления соединен с информационным входом первого триггера, тактовы вход которого соединен с тактовым входом второго триггера, первыми входами первого и второго элементов И и является тактовым входом блока, вход запуска блока является информа- ционным входом второго триггера, ин- версньй выход которого соединен с

5

0

O

5 0

вторым входом первого элемента И, выход которого Соединен с тактовым входом третьего триггера, инверсный выход которого соединен с первым входом третьего элемента И и информационным входом третьего триггера, прямой выход которого соединен с первым входом четвертого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого является третьим выходом блока, прямой выход второго триггера является пятым выходом бйока и соединен с входом разрешения записи первого триггера, с первыми входами второго и третьего элементов ИЛИ и вторыми входами первого элемента ИЛИ и второго элемента И, выход которого соединен с входом устгновки в 1 третьего триггера, вход признака конца нормализации блока является входом установки, в О первого триггера, инверсный выход которого соединен с третьим входом первого и вторыми входами третьего и четвертого элементов И и является шестым выходом блока, вход синхронизации блока соединен с четвертым входом первого и третьими входами третьего и четвертого элементов И, выход третьего эле мента И соединен с вторым входом второго элемента ИЛИ, выход которого соединен с первым входом четвертого элемента ИЛИ и является первым выходом блока управления, прямой выход первого триггера соединен с вторыми входами третьего и четвертого элементов ИЛИ и является седьмым выходом блока, выходы третьего и четвертого элементов ИЛИ являются соответственно вторым и четвертым выходами блока.

2S 21

22

3«

фиг. 2

JSl

ess

fOPo«MfO«M fVltM

Составитель H. Маркелова Редактор A. Лежнина Техред Л,Олейкик КорректорМ, Демчик

Заказ 7718/52 Тираж 694Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-ЗЗ, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г..Ужгород, yi. Пргх кп ; и. А

L.rJ

«u ::з

e

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для умножения данных переменной длины | 1985 |

|

SU1291972A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

Изобретение относится к области вычислительной техники. Целью изобретения является расширение функциональных возможностей за счет нормализации чисел. Устройство содержит сдвигающие регистры 1, 2 множимого и множителя, накапливающий сумматор 3, одноразрядные умножители 4, блок управления 5. Для достижения поставленной цели в него введены дополнительно счетчики 7, 8 множимого и множителя, счетчик 6 итераций, сумматор 9 характеристик, три элемента ИЛИ-НЕ 10, 11, 15, два элемента И-ИЛИ 12, 13 и элемент И 14. Сущность изобретения состоит в том, что введением дополнительного оборудования обеспечивается возможность обработки операндов с плавающей точкой, помимо операндов с фиксированной точкой. Эта возможность задается соответствующим режимом, в котором при необходимости нормализуются множимое и множитель, корректируются их характеристики, вычисляется характеристика результата, а затем выполняется перемножение мант-исс. Старшая часть результата накапливается в сумматоре 3, а младшая часть замещает множитесь в регистре 1 множителя. 1 з.п. ф-лы, 4 ил. 5 (Л -fj lN5 00 1 4 «

| Авторское свидетельство СССР № 758146, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1977 |

|

SU769539A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-30—Публикация

1985-07-11—Подача