(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОБЬЕКТОМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления объектом | 1989 |

|

SU1798804A1 |

| Устройство для управления объектом | 1984 |

|

SU1234850A2 |

| Устройство для дешифрации команд | 1987 |

|

SU1532932A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

1

Изобретение относится к цифровым командно-программным временным устройствам и может быть использовано в устройствах, осуществлянмщх управп ление автономными объектами.

Известно устройство программного управления, содержащее блок ввода программы, блок логических вычислений, бло1с оперативного запоминакхцего устройства (ОЗУ), блок управления, блок хранения алгоритма, блок коррекций, блок диспетчера, а также таймеры по числу каналов управленияD j«

Однако в устройстве отсутствует узел контроля вводимой информации. Обработке подпрограмме надлежат команды однорядной структуры и отсутствует разделение команд на виды команды непосредственно исполняемые после ввода, т.е. разовые команды; команды, исполняемые в моменты времени регламентированные программой - программные команды. Наличие таймера на.каждый канал управления пои многоадресной структуре устройства технически мало оправдано, например,.при последовательной отработке программных команд. Кроме того, в устройстве блоки можно резервировать, например, по узловым методам не меняя структуры, кроме, блока ОЗУ, поскольку затруднено разбиение матрицы накопителя ОЗУ на мелкие узлы..резервирования.

10

Наиболее близким по технической сущности к предлагаемому является устройство для передачи информации, содержащее анализатор существенности информации, преобразователь анаtsлог-код, буферное запоминающее устройство, .коммутатор опроса, регистр адреса, буферный регистр, счетчик адресов, схему сравнения, пусковую схему, коммутатор сигналов от дат20чиков информации и элементыИ 2.

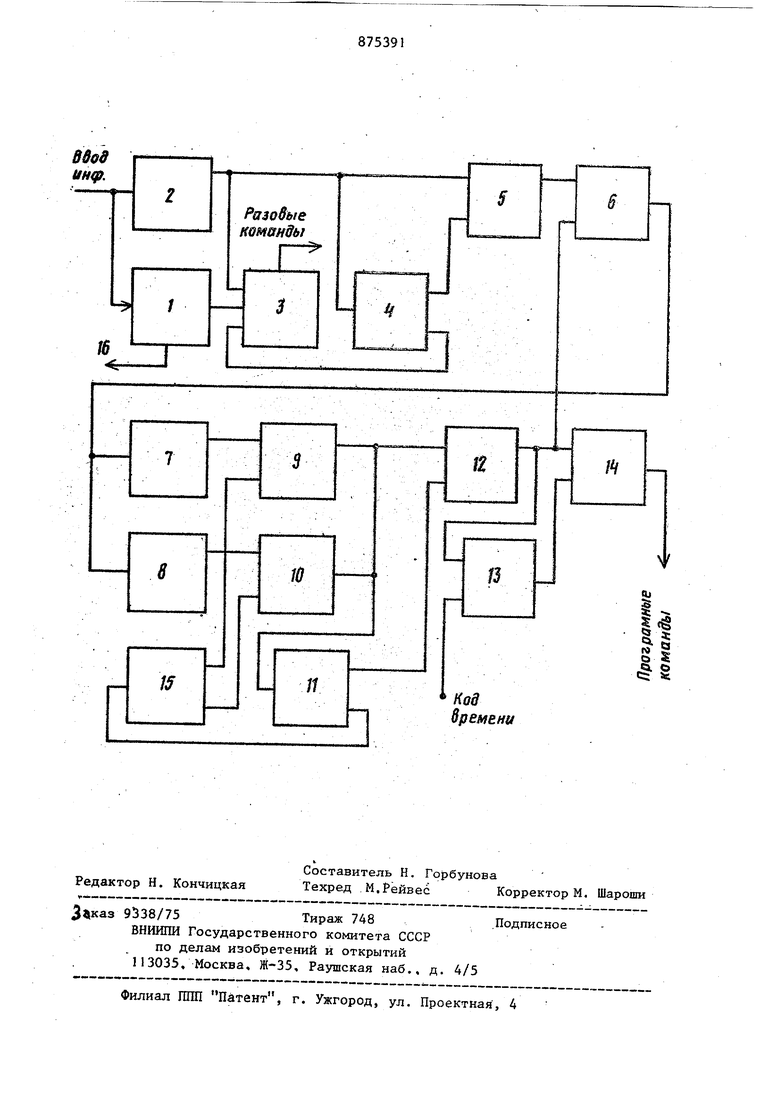

Недостатком этого устройства является отсутствие в нем возможности обеспечения управления объектом. как по разовым, так и по программным командам. Цель изобретения - увеличение нал дежйости устройства и обеспечение управления oбъeктo 4 как по разовым, так и по программным командам. Поставленная цель достигается тем, что в устройство для управления объектом, содержащее первый блок памяти три элемента И, регистр адреса, соединенный выходом со входом блока сравнения, введены элемент ИЛИ, второй блок памяти, счетчик, три дешифратора, два блока контроля и вход ной регистр, подключенш й входом к выходу первого блока контроля, а выходом - к первому входу первого деошфратора, ко входу второго дешифратора и через вршюченные последовател но первый элемент И, элемент ИЛИ - к входу первого и второго блоков памяти, соедияеяных в| 1ходами с первыми г входами второго я третьего элементов И подключенных выходами к первому входу регистра адреса, ко входу второго блока контроля, подключенного первым выходом через счетчик ко вторым входам второго и третьего злементов И, а вторым выходом - ко втор му входу регистра адреса соединенного выходом со вторым входом элемента ИШ я с первым входом элемента ИЛИ и с первым входом третьего дешифратора, связанного вторым входом с выходом блока сравнения, при чем выход -первого бдока контроля со единен со вторым входом первого дешифратора, подключенного третьим вхо дом к первому выходу второго девшфра тора, второй выход которого подключе ко второму входу первого элемента И На чертеже приведена блок-схема предлагаемого устройства. Устройство содержит первый блок контроля, входной регистр 2, первый и второй дешифраторы 3 и 4, первый элемент И 5, элемент ИЛИ 6, первый и второй блок памяти 7 и 8, второй и третий элементы И 9 и 10, второй блок 11 контроля, регистр 12 адреса блок 13 сравнения, третий дешифратор 14, счетчик 15, выход 16 устройстваУстройство работает следующим образом. На вход устройства вводится инфор мация в виде двоичнокодйрованных сло постоянной разрядности, содержащих как контрольную, так и информацион14ную част. Контрольная часть слова является производной от информационной части и служит для обеспечения прове.рки информационной части по принятым критериям (например, по модулю 2, модулю 3 и т.д.). В инфо|)мационной части слова кодируется информация признака команды и ее характеристика. По признакам команда подразделяются на следующие виды. Разовая команда (р. К.) - команда, подлежащая исполнению вслед за ее приемом, программная ЧР. К.) - команда, подлежащая исполнению в момент времени, определяемый программой. В характеристической части разовой команду кодируется адрес абонента, которому эта команда должна быть выдана. В характеристической части программной команды кодируется как адрес абонента, так и текущее время по программе, когда эта команда должна быть выдана абоненту. Слова команд вводятся в первый блок I контроля и входной регистр 2. Если результаты контроля слова отрицательные, то на выход 16 поступает сигнал, свидетельствуюш 1Й о необходимости повторного ввода слова. В случае, если правильно принятое слово является разовой командой, то со второго дешифратора 4 признаков выдается разрешающий сигнал на первый дешифратор 3 разовой команды, с выхода которого вьщается разовая команда соответствующему абоненту. В случае, если принятое слово является программной командой, то со второго дешифратора 4 выдается запрещающий сигнал на первый дешифратор 3 и разрешакмдий сигнал на второй вход первого элемента И и слово через элемент ИЛИ 6 записывается в оба (Злока , 7 и 8 памяти. Считывание пословно информации из блоков 7 и 8 памяти производится одновременно, однако она проходит либо через второй элемент И 9, либо через третий элемент И 10 в зависимости от состояния счетчиков 15 сбоев и поступает на вход второго блока 11 контроля. При поло(сительном результате контроля с прямого выхода второго блока 11 контроля ныдается разрешающий сигнал на регистр 12 адреса и в него вводится считанное слово, которое затем через элемент ИЛИ вновь перезаписывается в оба блока 7 и 8 памяти. При отри|цательном результате контроля со вто роге блока 11 контроля въедается запрещающий сигнал и считанное слово в регистр 12 адреса не вводится. Одновременно с первого выхода второго блока 11 контроля выдается сигнал на счетчик помощью которого взаимноменяются запрещакяцие и разрешакг щие сигналы на второй и третий элементы И 9 и 10 и считывание очередно го слова блоков 7 и 8 памяти повторяется. Введенное в регистр 12 адрес .подвергается отработке. Адресная часть слова хранимого в регистре 12 дешифрируется с помощью третьего девшфратора t4 программных команд при условии совпадения кора Т временной части слова с кодом и на вход третьего дешифратора 14 в момен равенства кодов подается разрешающий Сигнал. Сочетание счить1вае в 1Х слов, переключения выходов блока па мяти с перезаписью считанных слов и регистра I2 вновь в блоки 7 и 8 памяти обеспечивает возможность как повторного циклического исполнения всего массива записанных программны команд, так и восстановление инфррмации в случае ее искажения в одном из оперативных запоминающих устройс что снижает интенсивность отказов устройства в 3 раза, ,, Формула изобретения YcTpohcTBO для управления объектом, содержащее первый блок памяти, три элемента И, регистр адреса, сое диненный выходом со входом блока сравнения, отличающееся тем, что, с целью увеличения надежности устройства и обеспечения управления объектом как по разовым, так и по программным командам, в него введены злемент НПИ, второй блок памяти, счетчик,/три дешифратора, два блока контроля и входной регистр, подключенный входом к выходу первого блока контроля, а выходом - к пер-вому входу первого дешифратора, ко входу второго дешифратора, и через включенные последовательно первый злемент И, элемент ИЛИ - ко входу первого и второго блоков, памяти, соединенных выходами с первыми входами соответственно второго и третьего элементов.И, подключенных выходами к первому входу регистра адреса и ко входу второго блока контроля, подключенного первым выходом через счетчик ко вторым входам второго и третьего элементов И, а вто{илм выходом - ко второму входу регистра адреса, соединенного выходом со вторым входом элемента ИЛИ и с первым входом третьего дешифратора, связанного вторым входом с выходом блока сравнения причем выход первого блока контроля соединен со вторым входом первого дешифратора, подключенного третьим входом к первому выходу второго дешифратора, второй выход которого подключен ко второму входу первого элемента И. Источники информации, принятые во внимание при,экспертизе 1,Авторское свидетельство СССР 466492, кл. G 05 В 19/18, 1974. 2.Авторское свидетельство СССР 239079, кл. G 06 F 15/46 ,1967 (прототип).

Авторы

Даты

1981-10-23—Публикация

1980-02-22—Подача