формации в блоки памяти ;|р(5изво;и тся только при отрицательном результате проверки информации и именно в тот блок памяти, где она записана неверно, а правильная информация остается

I

Изобретение относится к цифровым командно-программным временным устройствам, осуществляющим управление автономными объектами, и является усовершенствованием известного устройства для управления объектом по авт. св. № 875391.

Цель изобретения - повышение надежности устройства для управления. объектом.

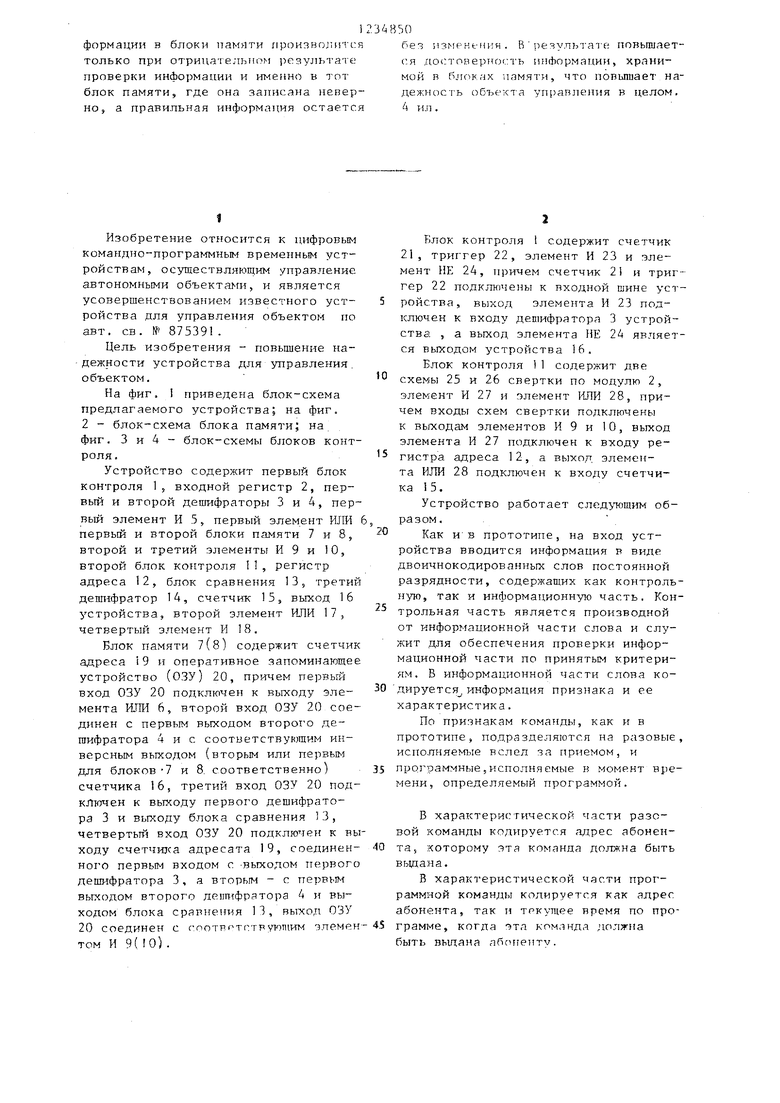

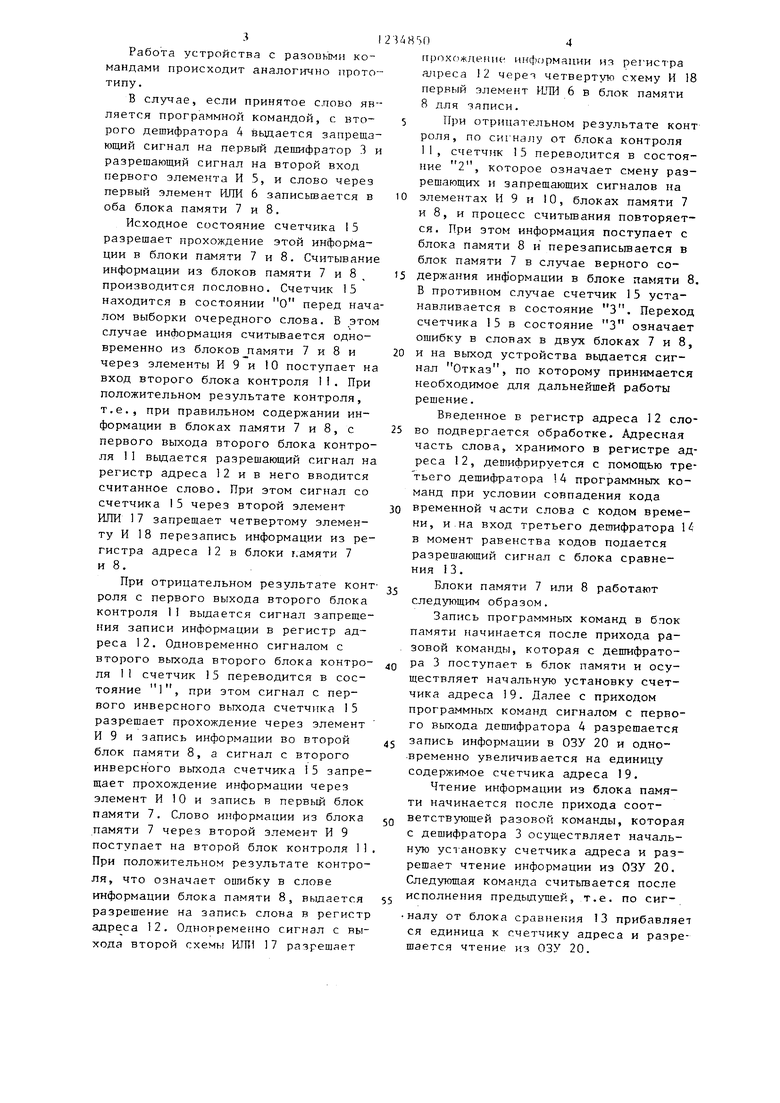

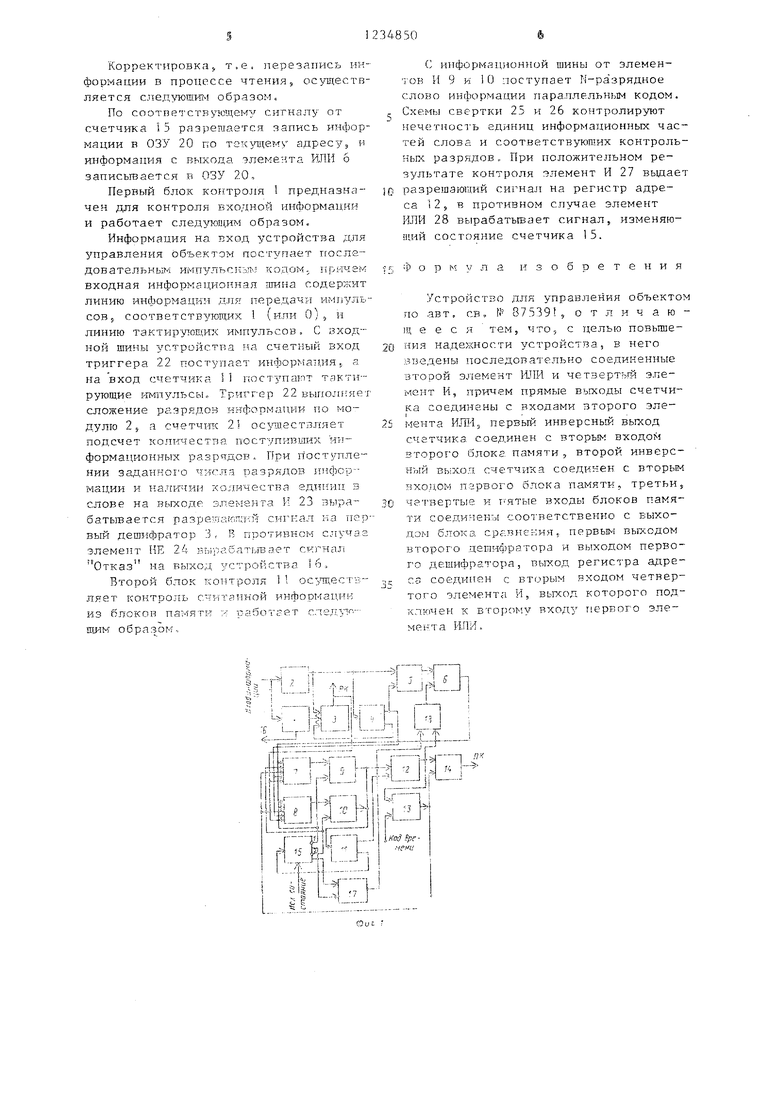

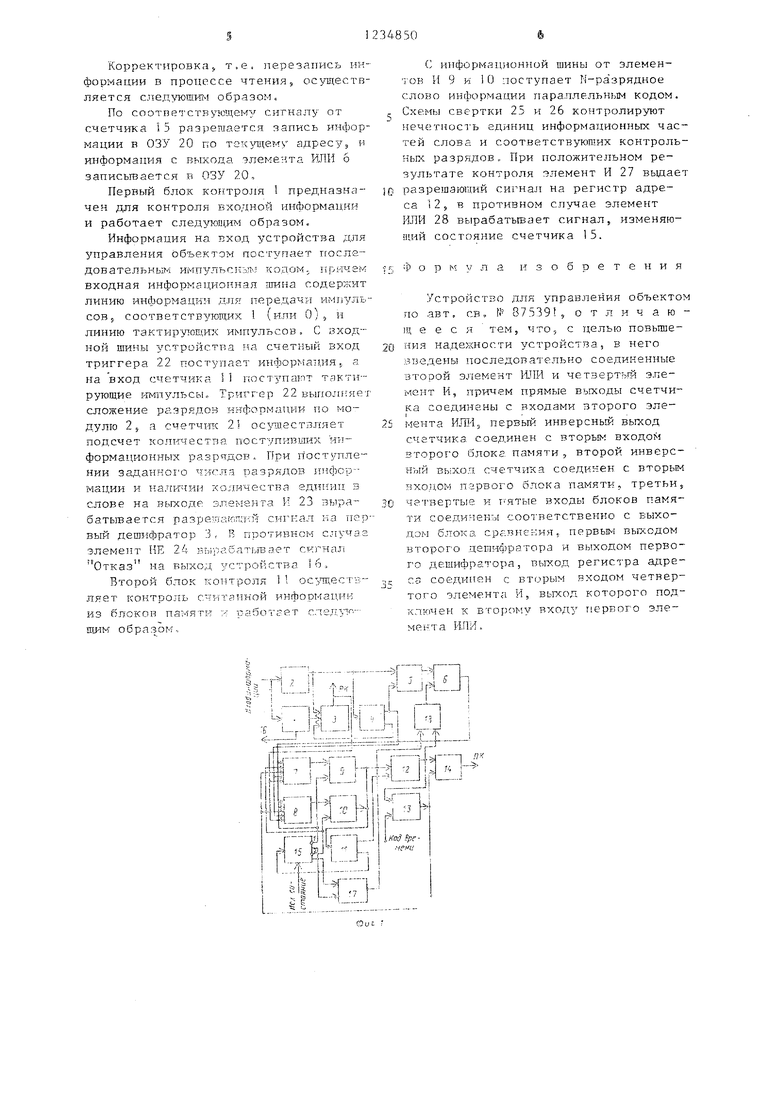

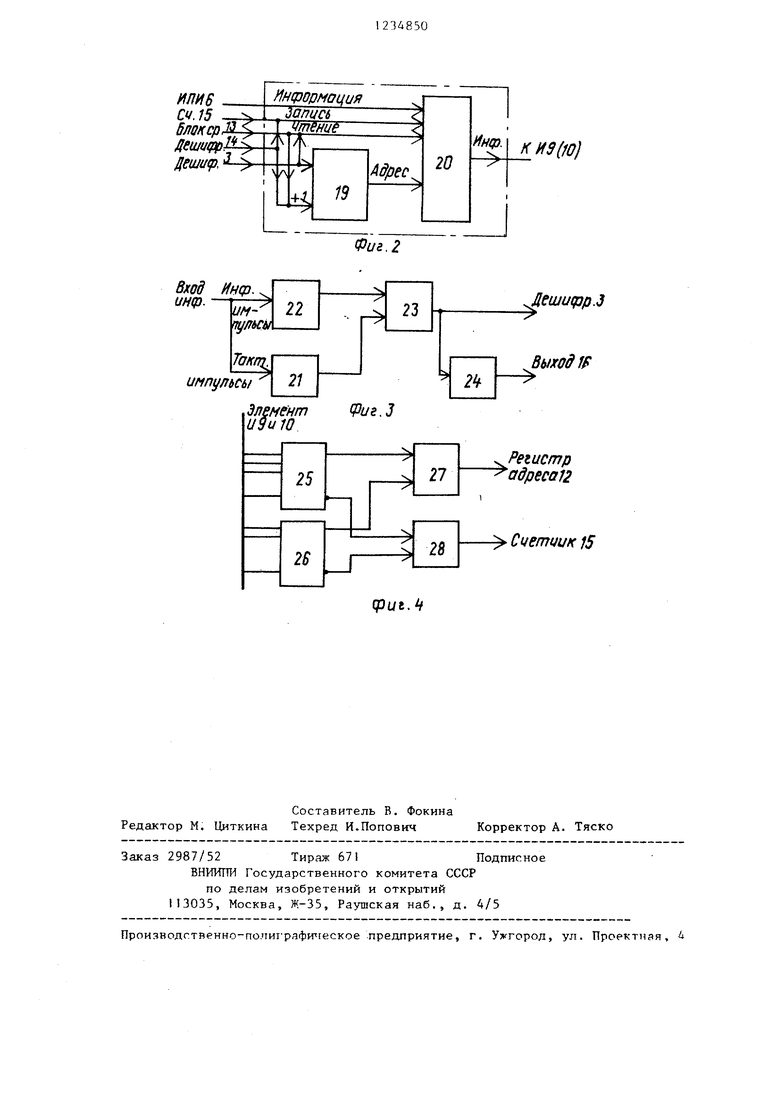

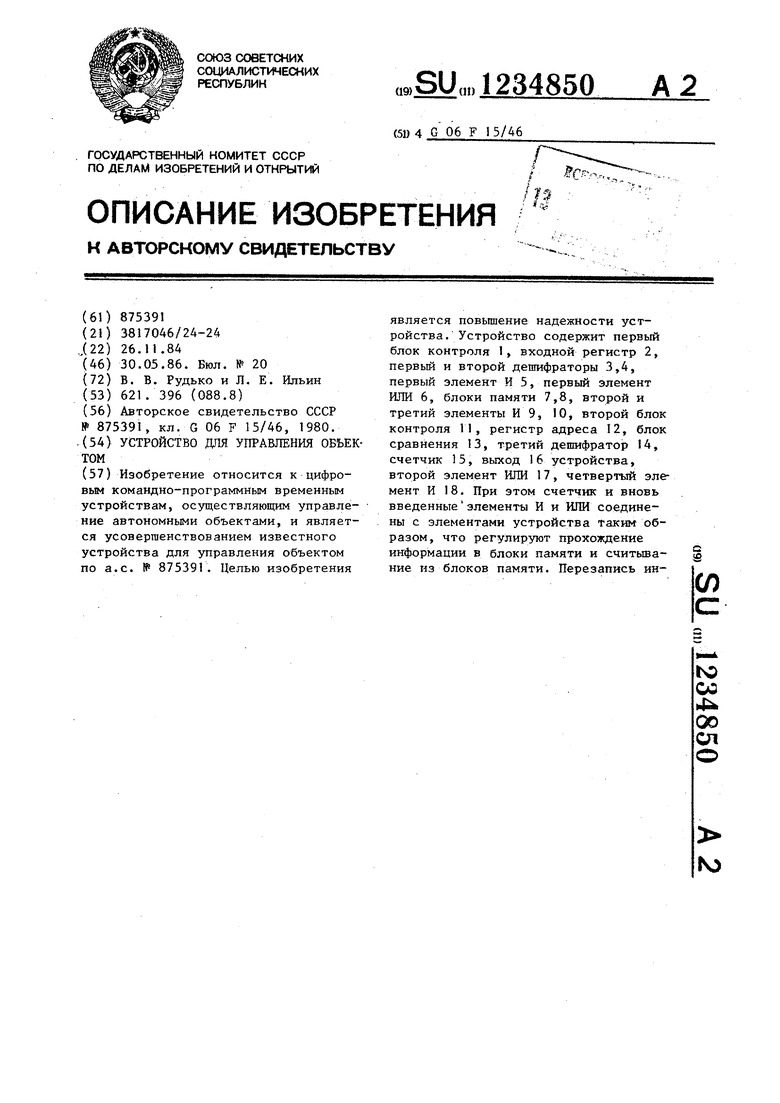

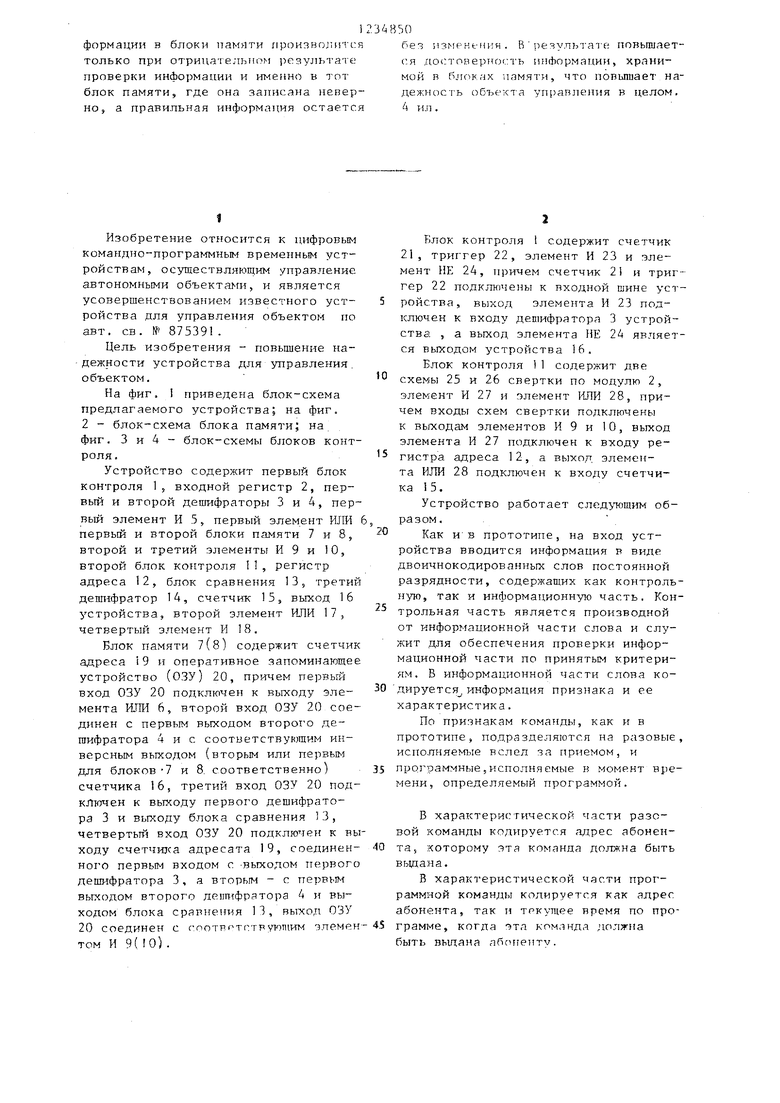

На фиг. I приведена блок-схема предлагаемого устройства; на фиг. 2 - блок-схема блока памяти; на фиг. 3 и 4 - блок-схемы блоков контроля.

Устройство содержит первый блок контроля 1, входной регистр 2, первый и второй дешифраторы 3 и 4, первый элемент И 5, первый элемент ИЛИ первый и второй блоки памяти 7 и 8, второй и третий элементы И 9 и 10, второй блок контроля I1, регистр адреса 12, блок сравнения 13, третий дешифратор 14, счетчик 15, выход 16 устройства, второй элемент ИЛИ 17, четвертый элемент И 18.

Блок памяти 7(8) содержит счетчик адреса 19 и оперативное запоминающее устройство (ОЗУ) 20, причем первый вход ОЗУ 20 подключен к выходу элемента ИЛИ 6, второй вход ОЗУ 20 соединен с первым выходом второго дешифратора 4 и с соответствующим инверсным выходом (вторым или первым для блоков -7 и 8. соответственно) счетчика 16, третий вход ОЗУ 20 подключен к выходу первого дешифратора 3 и выходу блока сравнения 13, четвертьпТ вход ОЗУ 20 подключен к выходу счетчшса адресата 19, соединенного первым входом с -выходом первого дешифратора 3, а вторым - с первьм выходом второго дептфратора 4 и выходом блока сравнения 13, выход ОЗУ 20 соединен с спотяртгтрутотним элементом И 9(10).

без H3MPHffiHH. R резул1 тате повышается до( товерт{о(.:ть информации, хранимой в блоках памяти, что повышает надежность объекта управле}1ия в целом. А ил.

0

5

5

0

5

.S

Блок контроля 1 содержит счетчик 21, триггер 22, элемент И 23 и элемент НЕ 24, причем счетчик 21 и триггер 22 подклн1чены к входной шине устройства, выход элемента И 23 подключен к входу дешифратора 3 устройства 5 а выход элемента НЕ 24 является выходом устройства 16.

Блок контроля 11 содержит две схемы 25 и 26 свертки по модулю 2, элемент Ц 27 и элемент 11ПИ 28, причем входы схем свертки подключены к выходам элементов И 9 и 10, выход элемента И 27 подключен к входу регистра адреса 12, а выход элемента ИЛИ 28 подключен к входу счетчика 1 5 .

Устройство работает следующим образом.

Как ив прототипе, на вход устройства вводится информация в виде двоичнокодированных слов постоянной разрядности, содержащих как контрольную, так и информационную часть. Контрольная часть является производной от информационной части слова и служит для обеспечения проверки информационной части по принятым критериям, В информационной части слова ко- дируется информация признака и ее характеристика.

По признакам команды, как и в прототипе, подразделяются на разовые, исполняемые вслед за приемом, и программные,исполняемые в момент времени, определяемый программой.

В характеристической части разовой команды кодируется адрес абонента, которому эта команда должна быть вьщана.

В характеристической части программной команды кодируется как адрес абонента, так и тркутцее время по программе, когда этл команда должна быть выдана абсшеиту.

31

Работа устройства с разо1зь 1мн командами происходит аналогично прототипу.

В случае, если принятое слово является программной командой, с второго дешифратора 4 йыдается запрещающий сигнал на первый дешифратор 3 и разрешающий сигнал на второй вход первого элемента И 5, и слово через первый элемент ИЛИ 6 записьшается в оба блока памяти 7 и 8.

Исходное состояние счетчика I5 разрешает прохождение этой информации в блоки памяти 7 и 8. Считывание информации из блоков памяти 7 и 8 производится пословно. Счетчик 15 находится в состоянии О перед началом выборки очередного слова. В этом случае информация считывается одновременно из блоков памяти 7 и 8 и через элементы И 9 и 10 поступает на вход второго блока контроля 1I. При положительном результате контроля, т.е., при правильном содержании информации в блоках памяти 7 и 8, с первого выхода второго блока контроля 1 вьщается разрешающий сигнал на регистр адреса 12 и в него вводится считанное слово. При этом сигнал со счетчика I5 через второй элемент ИЛИ 7 запрещает четвертому элементу И 1 8 перезапись информации из регистра адреса 12 в блоки г.амяти 7 и 8.

При отрицательном результате контроля с первого выхода второго блока контроля 1I выдается сигнал запрещения записи информации в регистр адреса 12. Одновременно сигналом с второго выхода второго блока контроля I1 счетчик 15 переводится в состояние 1, при этом сигнал с первого инверсного выхода счетчика 15 разрешает прохождение через элемент И 9 и запись информации во второй блок памяти 8, а сигнал с второго инверсного выхода счетчика 15 запрещает прохождение информации через элемент И 10 и запись в первый блок памяти 7. Слово информации из блока памяти 7 через второй элемент И 9 поступает на второй блок контроля 1 При положительном результате контроля, что означает ошибку в слове информации блока памяти 8, выдается разрешение на запись слова в регистр адреса 12. Одновременно сигнал с выхода второй схемь И.Ш1 17 разрешает

48Sn4

гтрохождение информации из регистра ajipeca 12 черет четвертую схему И 18 первый элемент ШТИ 6 в блок памяти В для записи.

5 При отрицательном результате конт роля, по сигналу от блока контроля 11, счетчик 15 переводится в состояние 2, которое означает смену разрешающих и запрещающих сигналов на

0 элементах И 9 и 10, блоках памяти 7 и 8, и процесс считьшания повторяется. При этом информация поступает с блока памяти 8 и перезаписьтается в блок памяти 7 в случае верного со5 держания информации в блоке памяти 8. В противном случае счетчик 15 устанавливается в состояние 3. Переход счетчика 5 в состояние 3 означает ошибку в словах в двух блоках 7 и 8,

0 и на выход устройства выдается си1- нал Отказ, по которому принимается необходимое для дальнейшей работы решение.

Введенное в регистр адреса 12 сло5 во подвергается обработке. Адресная часть слова, хранимого в регистре адреса 12, дешифрируется с помощью тре- тьего дешифратора 4 программных команд при условии совпадения кода

0 временной части слова с кодом времени, и на вход третьего дешифратора К- в момент равенства кодов подается разрешающий сигнал с блока сравнения I 3.

Блоки памяти 7 или 8 работают следующим образом.

Запись программных команд в бпок памяти начинается после прихода разовой команды, которая с дешифратоQ pa 3 поступает Б блок памяти и осуществляет начальную установку счетчика адреса 19. Далее с приходом программных команд сигналом с первого выхода дешифратора 4 разрешается

5 запись информации в ОЗУ 20 и одновременно увеличивается на единицу содержимое счетчика адреса 19.

Чтение информации из блока памяти начинается после прихода соотQ ветствующей разовой команды, которая с дешифратора 3 осуществляет начальную установку счетчика адреса и разрешает чтение информации из ОЗУ 20. Следующая команда считьшается после

, исполнения предьщушей, т.е. по сиг налу от блока сравне1;ия 13 прибавляет ся единица к счетчику адреса и разрешается чтение из ОЗУ 20.

5

Корректировка 5 т.е. перезапись информации в процессе чтения, осуществляется следлтощиь образом

По соответствующему сигналу от счетчика 15 раэрешс.ется запись информации в ОЗУ 20 по текущему адресу, и информация с выхоца элемента ИПН 6 записьгоается в ОЗУ 20,

Первый блок контроля 1 предназначен для контроля Бхо. шой информации и работает следующим образом.

Информация на вход устройства для управления объектом поступает коследов ательньм импульснъ;ъ; кодом примам входная информационная шина содержит линию информации для передачи импульсов j соответствующих 1 (, или 0), и линию тактир у70Е(ИХ импульсов , С входной шины устройства на счетный вход триггера 22 поступает информатщя, а на вход счетчика I 1 постунатпт тактирующие импульсы. Триггер 22 выполняет сложение разрядов информации по модулю 2s а счетчик 21 осхапествляет подсчет копичестза поступивших информационных разрядов,. При поступлении заданног о числа разрядов 1пк)ср-- мации и количества едигп-ш з слове на выходе элеьгента И 23 вырабатывается разре1чавдп;|-:й сигнал ка пер-- вый дешифратор 3, В противном случае элемент НЕ 24 вырабатывает cnrRaJi Отказ на выход устройства I 6 .

Второй блок кот1Троля i 1 ос ущестз- ляет контроль с итаиной информации из блоков памяти ; чзаботает следу -- щик образом.

,-ff

%

H-ri,447llrn-С информационной шины от элементов И 9 и 10 поступает М-разрядное слово информации параллельным кодом.

Схемы свертки 25 и 26 контролируют нечетность единиц информационных частей слова и соответствующих контрольных разрядов. При положительном результате контроля элемент И 27 выдает

разрешающий сигнал на регистр адреса 12, в противном случае элемент ИЛИ 28 вырабатьгоает сигнал, изменяющий состояние счетчика 15.

изобретения

Устройство для управления объектом по авт, ев о № 8753915 о т л и ч а ю - щ е е с я тем 5 что, с целью повыше- -НИН надежности устройства, в него введены последовательно соединенные второй э.лемент ШШ и четверт гй элемент И, причем прямые выходы счетчика соединены с входами второго эле- мента HJIi ij первый инверсный выход счетчика, соединен с вторым входом второго блока памяти , второй инверсный Bbixo i. счетчика соединен с вторым входом парвого блока памяти, третьи, четвертые и пятые входь блоков памя- - ги соединены соответственно с выходом блока сравнения, первьы выходом второго дешифратора и выходом первого дешифратора, выход регистра адресз соед-ццан с вторым входом четвертого элемента И, выход которого под- -ключен к второь :у входз первого зле мекта ИЛИ.

-5 --: J iJ J

f- iJ гНI

}1нсрормоция

запись

WfeHue

л

А

7

13

Элемент uz. US и 10

20

Инф. -

К ИЗ (10}

Фиг. 2

Деши(рр.з

Выход If

.etucmp adpecal2

Сметчик 15

дэие.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дешифрации команд | 1987 |

|

SU1532932A1 |

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Устройство для управления объектом | 1980 |

|

SU875391A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для управления объектом | 1989 |

|

SU1798804A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

Изобретение относится к цифро- вым командно-программным временным устройствам, осуществляющим управление автономными объектами, и является усовершенствованием известного устройства для управления объектом по а.с. № 875391. Целью изобретения является повышение надежности устройства. Устройство содержит первый блок контроля 1, входной регистр 2, первый и второй дешифраторы 3,4, первый элемент И 5, первый элемент ИЛИ 6, блоки памяти 7,8, второй и третий элементы И 9, 10, второй блок контроля 11, регистр адреса 12, блок сравнения 13, третий дешифратор 14, счетчик 15, выход 16 устройства, второй элемент ИЛИ 17, четвертый элемент И 18. При этом счетчик и вновь введенные элементы И и ИЛИ соединены с элементами устройства таким образом, что регулируют прохождение информации в блоки памяти и считьша- ние из блоков памяти. Перезапись иню (Л с к со NU 00 01

| Устройство для управления объектом | 1980 |

|

SU875391A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-05-30—Публикация

1984-11-26—Подача