Изобретение относится к экспериментальной ядерной физике и может быть применено в электронных схемах регистрации ядерного излучения и в других регистрирующих годоскопических системах.

Цель изобретения - повышение точности путем подсчета количества зарегистрированных частиц независимо от количества сработавших датчиков и увеличение быстродействия.

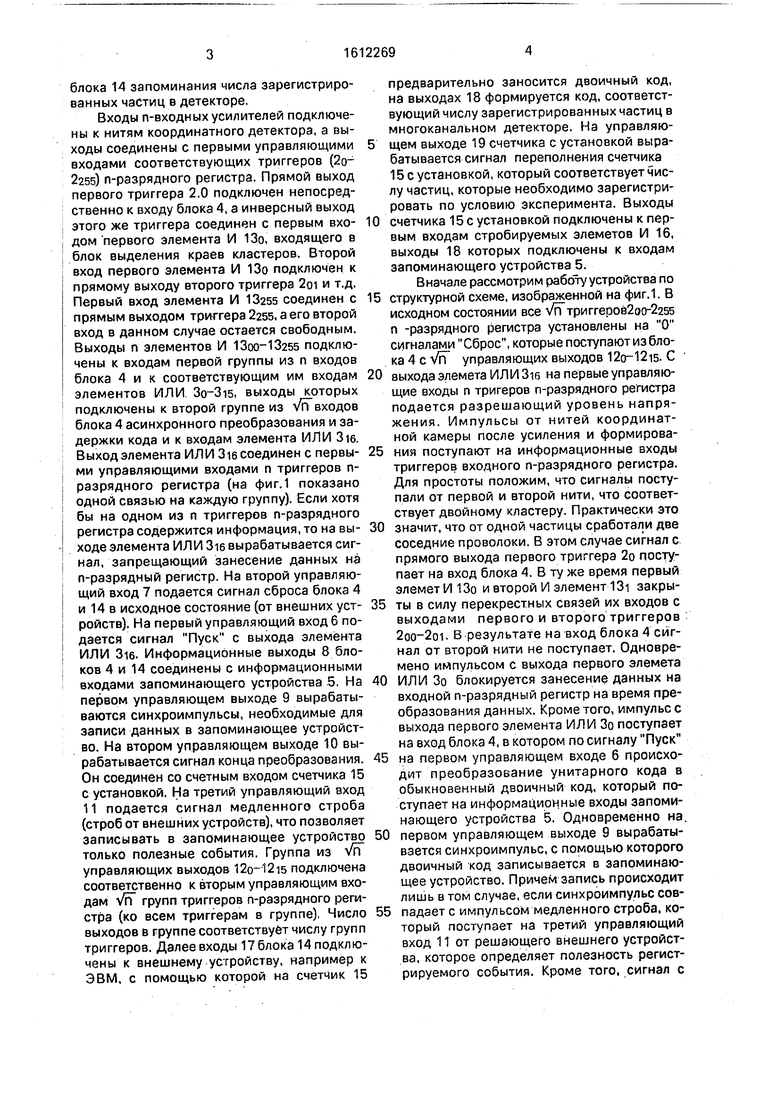

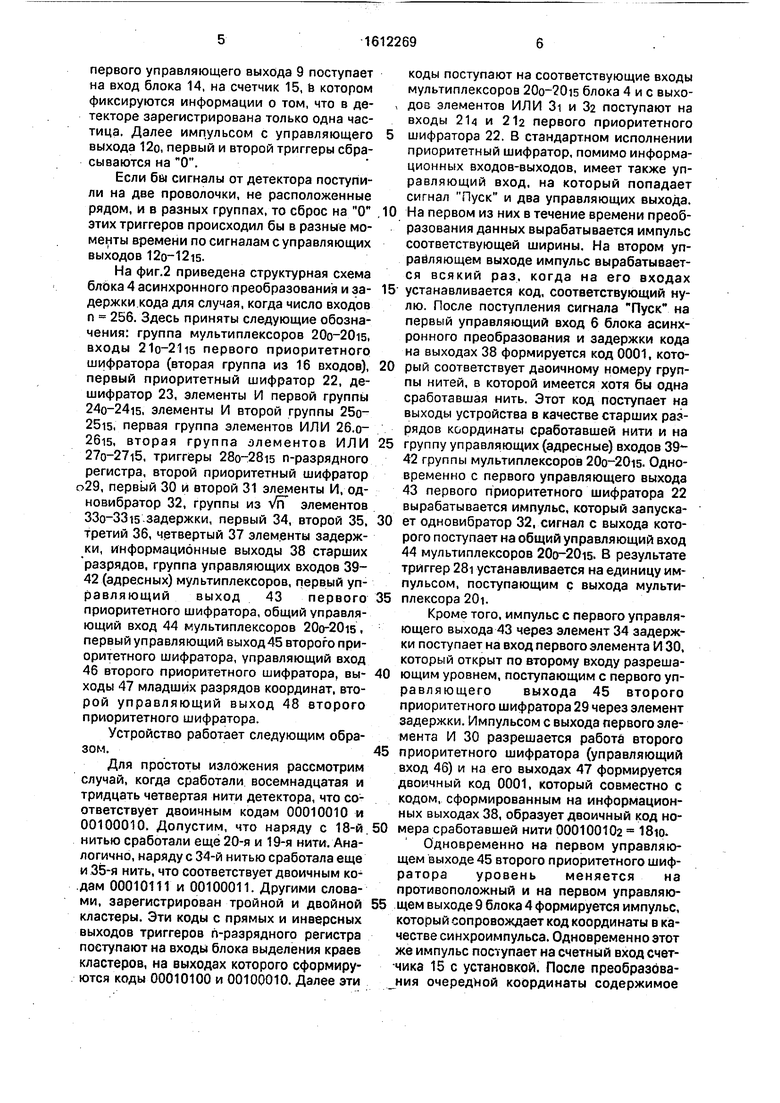

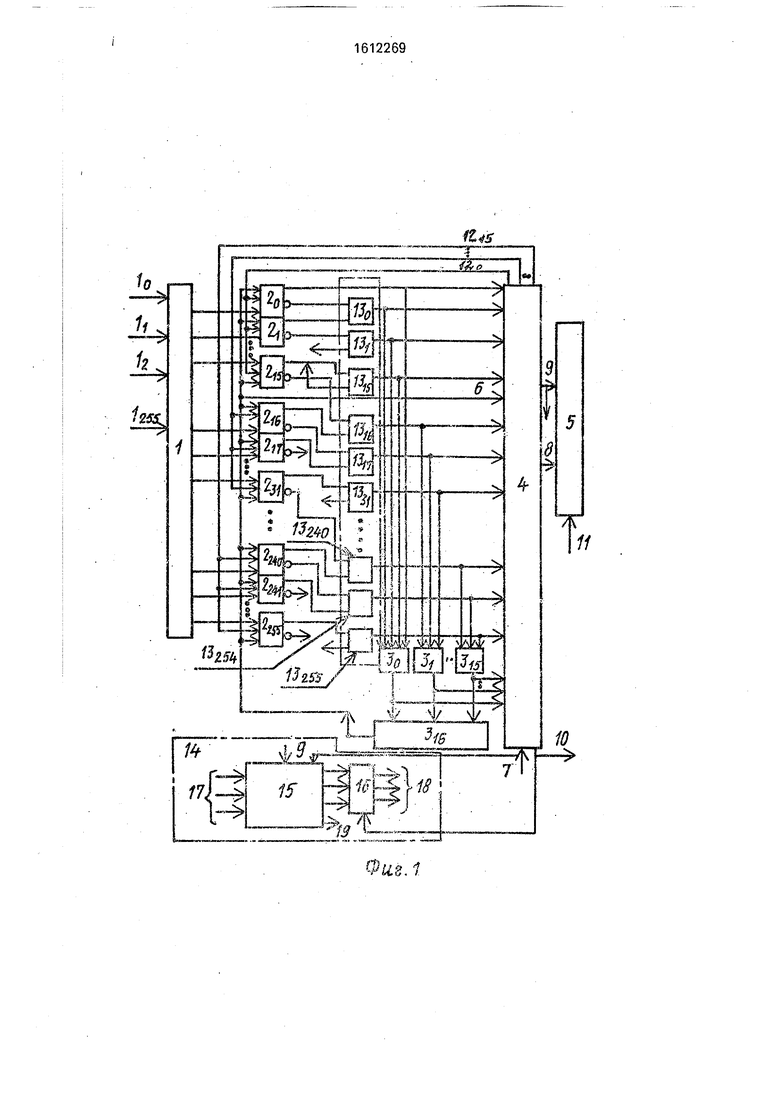

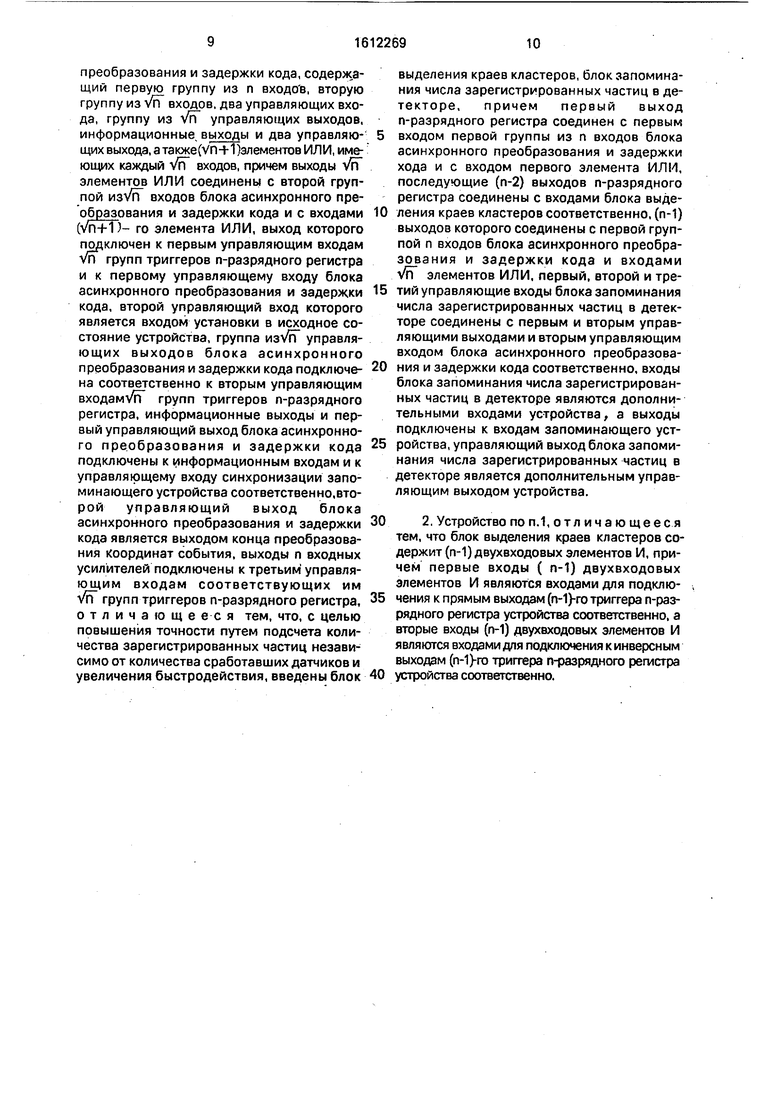

На фиг.1 приведена структурная схема устройства регистрации информации с координатной камеры; на фиг.2 - структурная схема асинхронного преобразования и задержки кода.

Структурная схема устройства для случая, когда число входов п 256. Входы пронумерованы от О до 255. Здесь приняты следующие обозначения: входы lo-lass, устройства, п входных усилителей, п-разряд- ный регистр, содержащий п триггеров

20-2255. разделенный на УпГ групп по VrT триггеров в группе, Vn-fl элементов ИЛИ 3o-3i6, блок4 асинхронного преобразования и задержки кода, запоминающее устройство.5, первый 6 и второй 7 управляющие входы блока асинхронного преобразования и задержки кода, информационные выходы 8, первый 9 и второй 10 управляющие выходы блока асинхронного преобразования и задержки кода, третий управляющий вход 11 устройства (управляющий вход стробирования блока записи), группа из управляющих выходов 12о- -12i5 блока асинхронного преобразования и задержка кода.блок выделения краев кластеров, состоящий из п элементов И ТЗо- 13255, блок 14 запоминания числа зарегистрированных частиц в детекторе, состоящий из счетчика.15 с установкой, группы стробируемых элементов И 16, входов 17, выходов 18 и управляющего выхода 19

СО

с

чэ о о о

блока 1-4 запоминания числа зарегистрированных частиц в детекторе.

Входы п-входных усилителей подключены к нитям координатного детектора, а выходы соединены с первыми управляющими входами соответствующих триггеров (2о- 2255) п-разрядного регистра. Прямой выход первого триггера 2.0 подключен непосредственно к входу блока 4, а инверсный выход этого же триггера соединен с первым входом первого элемента И 13о, входящего в блок выделения краев кластеров. Второй вход первого элемента И 13о подключен к прямому выходу второго триггера 2oi и т.д. Первый вход элемента И 13255 соединен с прямым выходом триггера 2255, а его второй вход в данном случае остается свободным. Выходы п элементов И 13оо-13255 подключены к входам первой группы из п входов блока 4 и к соответствующим им входам элементов ИЛИ. 3o-3i5. выходы которых подключены к второй группе из Vn входов блока 4 асинхронного преобразования и задержки кода и к входам элемента ИЛИ 3i6. Выход элемента ИЛИ 3i6 соединен с первыми управляющими входами п триггеров п- разрядного регистра (на фиг.1 показано одной связью на каждую группу). Если хотя бы на одном из п триггеров п-разрядного регистра содержится информация, то на выходе элемента ИЛИ 3i6 вырабатывается сигнал, запрещающий занесение данных на п-разрядный регистр. На второй управляющий вход 7 подается сигнал сброса блока 4 и 14 в исходное состояние (от внешних устройств). На первый управляющий вход 6 подается сигнал Пуск с выхода элемента ИЛИ 3i6. Информационные выходы 8 блоков 4 и 14 соединены с информационными входами запоминающего устройства 5, На первом управляющем выходе 9 вырабатываются синхроимпульсы, необходимые для записи данных в запоминающее устройство. На втором управляющем выходе 10 вырабатывается сигнал конца преобразования. Он соединен со счетным входом счетчика 15 с установкой. На третий управляющий вход 11 подается сигнал медленного строба (строб от внешних устройств), что позволяет записывать в запоминающее устройство только полезные события. Группа из Vn управляющих выходов 12o-12i5 подключена соответственно к вторым управляющим входам Vn групп триггеров п-разрядного регистра (ко всем триггерам в группе), Число выходов в группе соответствует числу групп триггеров. Далее входы 17 блока 14 подключены к внешнему устройству, например к ЭВМ, с помощью которой на счетчик 15

предварительно заносится двоичный код, на выходах 18 формируется код, соответствующий числу зарегистрированных частиц в многоканальном детекторе. На управляю- щем выходе 19 счетчика с установкой вырабатывается сигнал переполнения счетчика 15с установкой, который соответствует числу частиц, которые необходимо зарегистрировать по условию эксперимента. Выходы 0 счетчика 15с установкой подключены к первым входам стробируемых элеметов И 16, выходы 18 которых подключены к входам запоминающего устройства 5.

Вначале рассмотрим работу устройства по 5 структурной схеме, изображенной на фиг.1. В исходном состоянии все VгГтpиггepo82oo-2255 п -разрядного регистра установлены на О сигналами Сброс, которые поступают из блока 4с V управляющихвыходов 12o-12i5. С 0 выхода элемета ИЛ И Зш на первые управляющие входы п тригеров п-разрядного регистра подается разрешающий уровень напряжения. Импульсы от нитей координатной камеры после усиления и формирова- 5 ния поступают на информационные входы триггеров входного п-разрядного регистра. Для простоты положим, что сигналы поступали от первой и второй нити, что соответствует двойному кластеру. Практически это 0 значит, что от одной частицы сработали две соседние проволоки. В этом случае сигнал с прямого выхода первого триггера 2о поступает на вход блока 4. В ту же время первый элемет И 13о и второй И элемент 13i закры- 5 ты в силу перекрестных связей их входов с выходами первого и второго триггеров 2оо-2о1. В результате на вход блока 4 сигнал от второй нити не поступает. Одновре- мено импульсом с выхода первого элемета 40 ИЛИ Зо блокируется занесение данных на входной п-разрядный регистр на время преобразования данных. Кроме того, импульсе выхода первого элемента ИЛИ Зо поступает на вход блока 4, в котором по сигналу Пуск 45 на первом управляющем входе 6 происходит преобразование унитарного кода в обыкновенный двоичный код, который поступает на информационные входы запоминающего устройства 5. Одновременно на. 50 первом управляющем выходе 9 вырабатывается синхроимпульс, с помощью которого двоичный код записывается в запоминающее устройство. Причем запись происходит лишь в том случае, если синхроимпульс сов- 55 падает с импульсом медленного строба, который поступает на третий управляющий вход 1Т от решающего внешнего устройства, которое определяет полезность регистрируемого события. Кроме того, сигнал с

первого управляющего выхода 9 поступает на вход блока 14, на счетчик 15, и котором фиксируются информации о том, что в детекторе зарегистрирована только одна частица. Далее имп.ульсом с управляющего выхода 12о, первый и второй триггеры сбрасываются на О.

Если бш сигналы от детектора поступили на две проволочки, не расположенные рядом, и в разных группах, то сброс на О этих триггеров происходил бы в разные мо- ме1;1ты времени по сигналам с управляющих выходов 12o-12i5.

На фиг.2 приведена структурная схема блока 4 асинхронного преобразовани:я и задержки.кода для случая, когда число входов п 256. Здесь приняты следующие обозначения: группа мультиплексоров 20o-20i5t входы 21o-21i5 первого приоритетного шифратора (вторая группа из 16 входов), первый приоритетный шифратор 22, дешифратор 23, элементы И первой группы 24o-24i5, элементы И второй группы 25о- 25i5, первая группа элементов ИЛИ 26.о- 26i5, вторая группа элементов ИЛИ 27o-27i5, триггеры 28o-28i5 п-разрядного регистра, второй приоритетный шифратор о29, первый 30 и второй 31 элементы И, од- новибратор 32, группы из А/гГ элементов ЗЗо-ЗЗ 15 задержки, первый 34, второй 35, третий 36, четвертый 37 элементы задержки, информационные выходы 38 старших разрядов, группа управляющих входов 39- 42 (адресных) мультиплексоров, первый управляющий выход 43 первого приоритетного шифратора, общий управляющий вход 44 мультиплексоров 20cr20i5 , первый управляющий выход 45 второго приоритетного шифратора, управляющий вход 46 второго приоритетного шифратора, выходы 47 младших разрядов координат, второй управляющий выход 48 второго приоритетного шифратора.

Устройство работает следующим образом.

Для простоты изложения рассмотрим случай, когда сработали восемнадцатая и тридцать четвертая нити детектора, что соответствует двоичным кодам 00010010 и 00100010. Допустим, что наряду с 18-й нитью сработали еще 20-я и 19-я нити. Аналогично, наряду с 34-й нитью сработала еще и 35-я нить, что соответствует двоичным ко- .дам 00010111 и 00100011. Другими словами, зарегистрирован тройной и двойной кластеры. Эти коды с прямых и инверсных выходов триггеров п-разрядного регистра поступают на входы блока выделения краев кластеров, на выходах которого сформируются коды 00010100 и 00100010. Далее эти

коды поступают на соответствующие входы мультиплексоров 20o-20i5 блока 4 и с выхо- , дов элементов ИЛИ 3i и За поступают на входы 214 и 212 первого приоритетного 5 шифратора 22. В стандартном исполнении приоритетный шифратор, помимо информационных входов-выходов, имеет также управляющий вход, на который попадает сигнал Пуск и два управляющих выхода.

, 10 На первом из них в течение времени преобразования данных вырабатывается импульс соответствующей ширины. На втором уп- раёляющем выходе импульс вырабатывается всякий раз. когда на его входах

15 устанавливается код, соответствующий нулю. После поступления сигнала Пуск на первый управляющий вход 6 блока асинхронного преобразования и задержки кода на выходах 38 формируется код 0001, кото20 рый соответствует двоичному номеру группы нитей, в которой имеется хотя бы одна сработавшая нить. Этот код поступает на выходы устройства в качестве старших разрядов координаты сработавшей нити и на

25 группу управляющих (адресные) входов 3942группы мультиплексоров 20o-20i5. Одновременно с первого управляющего выхода

43первого приоритетного шифратора 22 вырабатывается импульс, который запуска0 ет одновибратор 32, сигнал с выхода которого поступает на общий управляющий вход

44мультиплексоров 20o-20i5. В результате триггер 28i устанавливается на единицу импульсом, поступающим с выхода мульти5 плексора 20i.

Кроме того, импульс с первого управляющего выхода 43 через элемент 34 задержки поступает на вход первого элемента И 30, который открыт по второму входу разреша0 ющим уровнем, поступающим с первого уп- равляющего выхода 45 второго приоритетного шифратора 29 через элемент задержки. Импульсом с выхода первого элемента И 30 разрешается работа второго

5 приоритетного шифратора (управляющий вход 46) и на его выходах 47 формируется двоичный код 0001, который совместно с кодом, сформированным на информационных выходах 38, образует двоичный код но0 мера сработавшей нити 000100102 18io.

Одновременно на первом управляющем выходе 45 второго приоритетного шиф- ратора уровень меняется на противоположный и на первом управляю5 щем выходе 9 блока 4 формируется импульс, который сопровождает код координаты в качестве синхроимпульса. Одновременно этот же импульс поступает на счетный вход счет- чика 15 с установкой. После преобразбва- ния очередной координаты содержимое

счетчика увеличивается нэ единицу. Импульсом конца преобразования, поступающим с второго управляющего выхода 10 блока 4 асинхронного упраг лешуш и задержки кода, содермсимое счетчика 15 строби- руется, и на выходах 18 блока 14 получается двоичный код, равный числу частиц,зареги- стрированнь х в детекторе, Этот код поступает на входы запоминаюидего ycrpovicTBa 5, где хранятся также коды координат. Триггер 28,1 п-разрядного регисгра находится в состоянии Единица, поэтому импульс проходит элемент И 24.i первой группы, проходит первую группу элементов ИЛИ и устаназливает на О триггер 28i. Изменение состояния триггера 28i происходит с задержкой на величину задержки элемента группы элементов задержки ЗЗо, поэтому импульс, поступающий с выхода элемента И второй группы 25о, дальше по цепи не проходит. Поскольку все триггеры установлены в О, то на втором управляющем выходе 48 второго приоритетного шифратора 29 вырабатывается импульс, который че- , рез элемент 37 задержки поступает на вход второго элемента И 31. На втором входе этого элемента поддержиЕгается разрешающий уровень, поступающий с первого управляющего выхода 43 первого приоритетного шифратора, С выхода второго элемента И 31 импульс поступает на управляющий вход дешифратора 23, на выходе группы из Vn управляющих выходов 12.1 которого вырабатывается импуль-с, с помощью которого устанавливаются в О триггеры первой группы входного регистра. Сигнал Пуск на первом управляющем входе б присутствует все время, пока идег регистрация всех коорд /,нат одного соб;.-.ггия. Поэтому после установки в О триггеров первой группы на информационных выходах 38 формируется код 0010, соответствующий наличию единицы,во второй группе триггеров входного регистра. Этот код поступает также на группу управляющих вхо дов 39-42 мультиплексоров.

Несколько ранее после установки в О триггера 28i на втором управляющм.1 выходе 48 второго приоритетного шифратора 29 вырабатывается импульс, который через элемент 37 задержки поступает на управляющий вход одковибратор :: 32,

В результате сигнал на выходе о.о.нозиб- ратора модулируется по амплитуде и фронтом этого сигнала, поступающего на общий управляющий вход 44 мультиплексороо 20р-2015,натриггер 28. заносг.тся единице. За счет задержки на элементе 36 на управляющем входе 46 второго приоритетного

п-

, . . з -о о

шифратора продолжает оставаться разре- шаюш,ий уровень и на выходах 47 младших разрядов координат формируется код 0100. который совместно с кодом 0010 образует 5 код001001002 341осле.дующейсработавшей ,. - нити. Одновременно на первом управляю- щем выходе 45 второго приоритетного шифратора изменяется уровень напряжения и на первом управляющем выходе 9 блока 4 10 формируется импульс, который проходит элементы И второй группы 25o-25i и 242, элемент ИЛИ 2б2 и устанавл шает в О триггер 282, Аналогично описанному на выходе второго элемента И 31 формируется им- 15 пульс, который разрешает работу дешифратора 23, на выходе которого (группа управляющих выходов 122 блока 4) формируется импульс, с помощью которого устанавливается в О вторая группа триггеров 20 входного регистра. В результате на втором управляющем выходе 48 второго приоритетного шифратора 29 вырабатывается импульс Конец регистрацией координат одного события.

25Одновременно снимается разрешающий уровень на первом управляющем выходе 43 первого приоритетного шифратора и на первом управляющем входе 6 блока 4, Далее цикл регистрации координат события 30 повторяются. На зторой управляющий вход 7 блока 4 перед началом работы устройства подается сигнал установки в О. С помощью элемента задержки имеется возможность плавно р.егулировать время поступления 35 двоичных координат с информационных выходов 38 и выходов 47 на запоминающее устройство, где с помощью сигнала медленного строба происходит регистрация только координат по.лезных событий. 40 С помощью блока выделения краев кластеров выделяются только крайние позиции в тех местах, где имеются кластеры, в то время как одиночные сигналы проходят без изменений. В результате с помощью блока счета числа зарегистрированных частиц в детекторе в каждом такте преобразования координат подсчитывается не число сработавших датчиков, а число зарегистрированных частиц, В свою очередь, это приводит к. 50 увеличению быстродействия устройства. Формула изобретения 1. Устройство регистрации информации с координатной камеры, содержащее п входных усилителей, п-разрядный регистр, 55 содержащий п триггеров, разделенных на-Уп групп триггеров, запоминающее уст- оой ство, содержащее информационные входы Л два управляющих входа: синхронизации и строб ироаания, блок асинхронного

- Л

преобразования и задержки кода, содержащий первую группу из п входо в, вторую группу из VnT входов, два управляющих входа, группу из VrT управляющих выходов, информационные, выходы и два управляю- щих выхода, а также()элементов ИЛИ, имеющих каждый VPT входов, причем выходы VfT элементов ИЛИ соединены с второй группой изУгГ входов блока асинхронного преобразования и задержки кода и с входами (Vn+1)- го элемента ИЛИ, выход которого

Гключен к первым управляющим входам групп триггеров п-разрядного регистра и к первому управляющему входу блока асинхронного преобразования и задержки кода, второй управляющий вход которого является входом установки в исходное состояние устройства, группа управляющих выходов блока асинхронного преобразования и задержки кода подключе- на соответственно к вторым управляющим входамУТГ групп триггеров п-разрядного регистра, информационные выходы и первый управляющий выход блока асинхронного преобразования и задержки кода подключены к информационным входам и к управляющему входу синхронизации запоминающего устройства соответственно,вто- рой управляющий выход блока асинхронного преобразования и задержки кода является выходом конца преобразования координат события, выходы п входных усилителей подключены к третьим управляющим входам соответствующих им VrT групп триггеров п-разрядного регистра, отличаю ще ее я тем, что, с целью повышения точности путем подсчета количества зарегистрированных частиц независимо от количества сработавших датчиков и увеличения быстродействия, введены блок

выделения краев кластеров, блок запоминания числа зарегистрированных частиц в детекторе, причем первый выход п-разрядного регистра соединен с первым входом первой группы из п входов блока асинхронного преобразования и задержки хода и с входом первого элемента ИЛИ, последующие (п-2) выходов п-разрядного регистра соединены с входами блока выделения краев кластеров соответственно, (п-1) выходов которого соединены с первой группой п входов блока асинхронного преобразования и задержки кода и входами элементов ИЛИ, первый, второй и третий управляющие входы блока запоминания числа зарегистрированных частиц в детекторе соединены с первым и вторым управляющими выходами и вторым управляющим входом блока асинхронного преобразования и задержки кода соответственно, входы блока запоминания числа зарегистрированных частиц в детекторе являются дополнительными входами устройства, а выходы подключены к входам запоминающего устройства, управляющий выход блока запоминания числа зарегистрированных частиц в детекторе является дополнительным управляющим выходом устройства.

2, Устройство по П.1, отличающееся тем, что блок выделения краев кластеров содержит (п-1) двухвходовых элементов И, причем первые входы ( п-1) двухвходовых элементов И являются входами для подключения к прямым выходам (п-1)-го триггера п-разрядного регистра устройства соответственно, а вторые входы (п-1) двухвходовых элементов И являются входами для подключения к инверсным выходам (п-1)-го триггера п-разрядного ретстра устройства соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство регистрации информации с координатной камеры | 1983 |

|

SU1172381A1 |

| Устройство для ввода информации | 1983 |

|

SU1108427A1 |

| Устройство ассоциативного кодирования и объемного сжатия информации | 1987 |

|

SU1441484A1 |

| Устройство для регистрации аналогового процесса | 1989 |

|

SU1774379A1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Устройство для моделирования систем массового обслуживания | 1984 |

|

SU1229771A1 |

| Устройство для ввода информации | 1979 |

|

SU840870A1 |

| Многоканальный измеритель интенсивности импульсов | 1991 |

|

SU1807423A1 |

| Устройство для моделирования гибких производных систем | 1988 |

|

SU1631551A1 |

| Многоканальный коммутатор | 1980 |

|

SU869033A1 |

Изобретение относится к экспериментальной ядерной физике и может применяться в электронных схемах регистрации ядерного излучения. Цель изобретения - повышение точности путем подсчета количества зарегистрированных частиц независимо от количества сработавших датчиков и увеличение быстродействия. В устройство введены блок выделения краев кластеров и блок запоминания числа зарегистрированных частиц в детекторе. Указанные блоки содержат группу элементов И и счетчик с установкой. Включение группы элементов И позволяет регистрировать только количество частиц, зарегистрированных в детекторе. Использование счетчика с установкой создает возможность останавливать работу устройства в момент регистрации напередзаданного количества частиц. 1 з.п. ф-лы, 2 ил.

Фив.1.

Фиг. 2

Составитель л.Тало ни на Редактор С.Патрушева Техред М.Моргентал

Корректор А.Обручар

| Устройство регистрации информации с координатной камеры | 1983 |

|

SU1172381A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-12-07—Публикация

1989-01-27—Подача