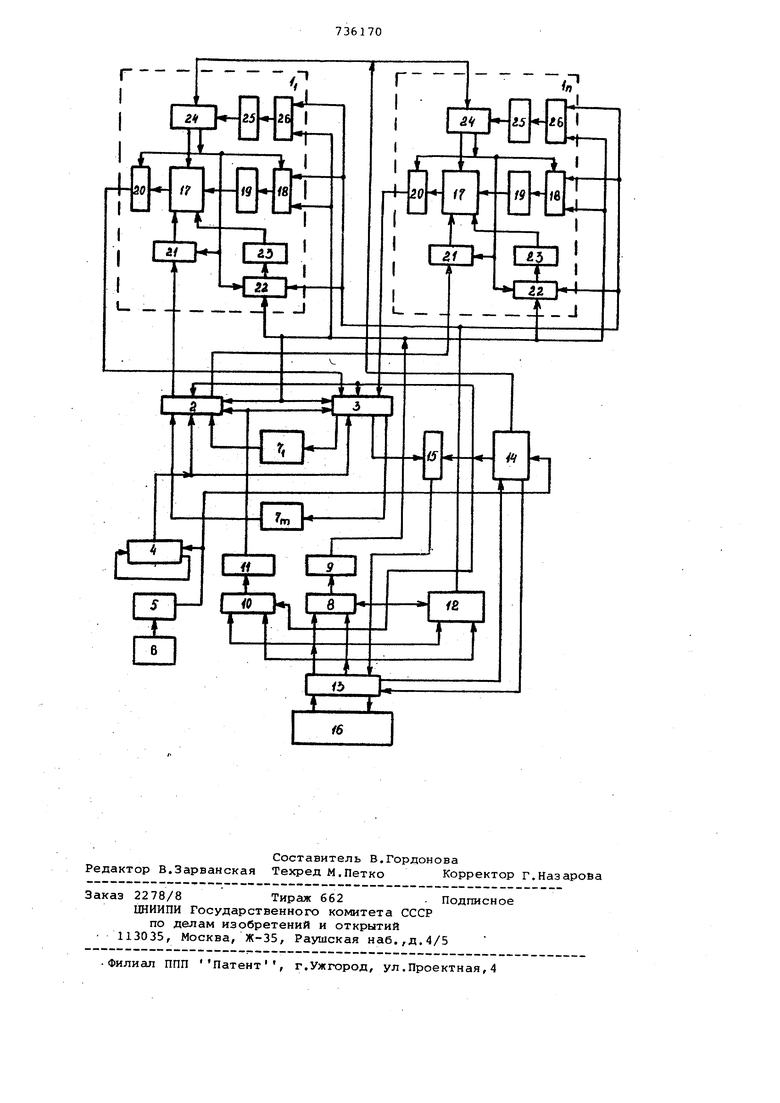

Изобретение .относится к вычислительной технике и может быть исполь зовано в вычислительных систем&х с аппаратурной реализацией мультипрограммного режима обработки инфор мации для быстрой смены программы коммутации peuiaroiwx блоков. Известно устройство коммутации выходов и входов решающих блоков цифрового дифференциального анализа содержащее последовательно соединен ные счетчик и дешифратор адреса, накопитель, два регистра числа, блок связи и блок управления 1. Недостаток этого устройства г ни кое быстродействие при смене програ мы коммутации в накопителе. Наиболее близким по своему техни ческому решению к предлагаемому является запоминающее устпойство, содержащее блок сопряжени-я,управ-. ляющим выходом подключенный через последовательно соединенные регистр и дешифратор кода операции к блоку управления,информационным выходом к буферному регистру, информационны входом - к выходу цифровой вычисли ной маютны (ЦВМ) обшего назначения или к выходу Ънаинего устройства и управляющей связью - к блоку управления, выход которого соединен с первым регистром числа, подключенным выходом к информационному входу накопителя, а входом - к выходам решающих блоков,со вторым регистром числа, подключенным входом к информационному выходу накопителя, а выходом - ко входам решающих блоков, с буферным регистром, подк.гаоченным первым выходом через последовательно соединенные первые регистр и дешифратор адреса к адресному входу накопителя, а вторым выходом через последовательно соединенные вторые . регистр и дешифратор адреса - к другому адресному входу накопителя 2. Недостатком известного устройства является низкое быстродействие и ограниченные Функциональные возможности, связанные с медленной -сменой в блоке памяти программы коммутации решающих блоков при вычислении пакета различных задач. Цель изобретения - повышение быстродействия и расзиирение функциональных возможностей запоминающего устройства. Поставленная цель достигается тем, что в него введены дополнитель ные блоки памяти, коммутатор ввода, соединенный выходом с первыми инфор ционными входами дополнительных бло ков памяти,коммутатор вывода,вход к торого подключен к информационным в ходам дополнительных блоков памяти, последовательно соединенные генератор синусоидального сигнала, формирователь тактовых импульсов и кольцевой регистр, выход которого подключен к первым управляю1цим входам коммутатора ввода и коммутатора выв да, соединенных соответственно вход И выходом с выходами и входами реша щих блоков, последовательно, соединё ные регистр номера блока памяти и дешифратор номера блока памяти, выход которого подключен к управляющи входам дополнительных блоков памяти И ко вторым управляющим входам комм татора ввода и коммутатора вывода, последовательно соединенные регистр признака и дешифратор признака, выход которого подключен к третьим управляю1щм входам коммутатора ввода и коммутатора вывода, буферный блок памяти, информационный и управ ЛЯЮ1ГЩЙ входы которого соединены соответственно с.информационным и упра ляющим выходами блока сопряжения информационными и первыми управляющими входами регистра признака и регистра номера блока памяти, информацион ный выход буферного блока памяти сое динен с первыми, вторыми и третьими информационными входами дополнительных блоков памяти, другой управляющий вход - с выходом блока управления, подключенного входом к выходу формирователя тактовых импульсов и двусторонней связью к блоку сопряжения, третий вход - со вторыми управляющими входа1«1и регистра признака, регистра номера блока памяти и управляю1чим входом буферного регис ра, информационный вход которого под ключен к выходу коммутатора вывода, а выход - к блоку сопряжения. Это позволяет расширить функциональные возможности и повысить быстродействие устройства, так как смена программы коммутации выходов и входов решающих блоков выполняется за такт работы кольцевого регистра,. Кро ме того, становится возможным одновременное осуществление ввода программы коммутации в какой-либо блок памяти со стороны ЦВМ и циклическое подключение всех остальных блоков памяти через коммутаторы ввода и вывода для смены программ коммутации решаю111их блоков при мультипрограммном режиме их работы. На чертеже представлена структурная схема запоминающего устройства. Она содержит блоки ( памяти, коммутатор 2 ввода, выход КОТОРОГО подключен к первым информационным входам блоков 1 -1 , памяти, комму татор 3 вывода, соединенный входом с информационными выходами блоков , памяти, кольцевой регистр 4, вход которого подключен через юрмирователь 5 тактовых импульсов к выходу генератора 6 синусоидального сигнала, а выход - к первым управляюгчим входам KOMMiTaTopa 2 ввода и коммутатора 3 вывода, соединенных соответственно входом и выходом с выходами и входами раиаюших блоков 7 -7,, последовательно соединенные регистр 8номера блока памяти и дешифратор 9номера блока памяти, выход которого подключен к управляющими входам блоков 1 -Ij памяти и ко вторым управляющим входам коммутатора 2 ввода и коммутатора 3 вывода, последовательно соединенные регистр 10 признака и дешифратор 11 признака, выход которого подключен, к третьим упоавляющим входам коммутатора ввода и коммутатора вывода, буферный- блок 12памяти, выход которого соединен с первыми, вторыми и третьими информационными входами блоков памяти, информационный и управляющий входы соединены соответственно с информационным и управляющим выходами блока 13 сопряжения,информационными и первыми управляющими входами регистра 10 признака и регистра 8 номера блока памяти и другим управляю1г1лм входом буферный блок памяти соединен с выходом блока 14 управления, подключенного входом к выходу формирователя 5 тактовых импульсов и двусторонней связью к блоку 13 сопряжения, третий вход - со вторыми управляющими входами регистра 10 признака, регистра 8 номера блока памяти и управляющим входом буферного регистра 15, информационный вход которого подключен к выходу коммутатора 3 вывода, а выход - к блоку 13сопряжения, имеющего двустороннюю связь с ЦВМ 16, В состав каждого блока l(,n) памяти входит накопитель 17, первый регистр 18 адреса, информационный и управляющий входы которого подключены соответственно ко второму информационному и упоавляющему входам блока ii памяти, а выход - через первый дешифратор 19 адреса к первому адресному входу накопителя 17, информационные выход и вход которого соответственно соединены через первый регистр 20 числа с информационным выходом блока 11 памяти и через второй регистр 21 числа с третьим информационным входом блока 11 памяти, второй регистр 22 адреса, информационный и управляющий входы которого подключены соответственно к первому иН(1)Ормационно; 1у и управляющему входам блока 11 памяти, а выход - через ВТОРОЙ дешифратор 23 адреса ко второму адресному входу накопителя 17, управляющий вход которого соединен с первым выходом блока 24 местного управления, подключенного вторым выходом к двум регистрам 20 и 21 числа и к двум регистрам 18 и 22 адреса, а входом через дешифратор 25 кода операции с выходом регистра 26 кода операции информационнр-;й и управляющий выходы которого подключены.соответственно к четвертому инЛормационному и упра ляющему входам блока памяти. Работа запоминающего устройства происходит в двух режимах: в режиме ввода (вывода) программ коммутации в соответствующие блоки ., памяти со стороны ЦВМ 16 и в режиме раб ты решающих блоков 7 когда происходит последовательное подключение блоков памяти через коммутатор 2 ввода и коммутатор 3 вывода ко входам и выходам решающих блоков 7 -7т. В первом режиме из ЦВМ 16 через блок 13 сопряжения, буферный блок 12 памяти осугпествляется ввод в тре буемый блок памяти кодов, состав ляющих программу коммутации выходов входов решаю1чих блоков . Форма кодов программы коммутации состоит из кода операции и кода адреса. В зависимости от кода операции код адреса может быть использован или для организации продольного, или дл организации поперечнох о обращения к накопителю 17 блока 11 памяти. Таким образом, в соответствии с код операции, принятым из буферного бло 12 памяти в регистр 26, блок 24 местного управления вырабатывает сигналы, по которым код адреса из буферного блока 12 памяти поступает в первый регистр 18 адреса или во второй Регистр 22 адреса. Кроме того код операции определяет формировани блоком местного управления сигналов для организации одновременного сбро ячеек памяти, сброса продольной или поперечной ячейки памяти и сброса элемента памяти накопителя 17. Так как матрица программы коммутации, хранящаяся в накопителе 17, имеет разреженный характер (в одной строке или столбце матрицы может находиться только одна единица) связанный с тем, что два или более выхода решающих блоков не могут быть подключены к одному входу.какого-либо решающего блока,.то в нако питель 17 выполняется с помошью регистра 18, дешифратора 19 и регистр 22, дешифратора 23 поразрядная запись ее единиц (наличие единицы в 1,- J -элементе этой матрицы означает соединение i-ro выхода решаю щего блока с j -ым входом решающего блока, а наличие нуля - отсутствие соединения). Выбор определенного блока памяти Ij выполняется сигналом с выхода дешифратора 9 номера блока памяти в соответствии с кодом номера блока памяти, принятым из ЦВМ 16 чеоез блок 13 сопряжения в регистр 8 номера блока памяти. Для проверки правильности ввода кодов программы коммутации в накопитель 17 осуществляется их вывод через регистр 20 числа, коммутатор 3 вывода, буферный регистр 15, блок 13сопряжения в ЦВМ 16. При этом подключение требуемого блока памяти через коммутатор 3 вывода к буферному регистру 15 выполняется сигналами, сформированными на 1выходе дешифратора 11, признака и на входе дешифратора 9 номера блока памяти 9. Код признака аналогично коду номера блока памяти и коду программы коммутации передается из ЦВМ 16 через блок 13 сопряжения в регистр 10 признака при наличии соответствующего сигналаидентификатора блока 13 сопряжения. Во втором режиме работа запоминающего устройства происходит таким образом, что на первом шаге решения коммутируются выходы и входы решающих блоков относящихся к первой задаче, на втором шаге - ко второй задаче и т.д. Это достигается благодаря последовательному подключению информационных выходов и входов блоков памяти ко входам и выходам решаю1чих блоков 7 f через коммутатор 3 вывода и коммутатор 2 ввода, управляемые сигналами блока 14управления и кольцевого регистра 4, циклическое продвижение единицы в котором обеспечивается сигналами формирователя 5 тактовых импульсов 5 и генератора 6. На каждом шаге решения приращения с выходов решающих блоков поступают через коммутатор 2 ввода 2 в регистр 21 числа блока памяти соответствующего шагу решения (номера задачи). С выходов регистра 21 усиленные сигналы единичных значений приращений производят одновременное неразрушаемое считывание информации в поперечных или прот доль-ных ячейках памяти накопителя 17, которое становится возможным благодаря тому, что в каждом столбце или строке матрицы накопителя может быть записана только одна единица. В том же шаге решения считываемая из накопителя 17 информация поступает через другой регистр 20 числа и коммутатор 3 вывода на входы только тех решающих блоков 7 лля которых в элементах памяти соответствующих строк (столбцах) матрицы накопителя 17 записаны единицы. Каждай шаг решения (такт работы кольцевого регистрй) состоит из нескольки циклов обрао(ення (считываний) к бло ку памяти. При иеобходиг-Юсти подключения только ОДКО1Х1 блока памяти (одно:ггоо раммный режим работы) ко входам и выходам решаюгаих блоков 7 т ЦВМ 16 осуществляет ввод соответствующего кода признака в регистр 10 признака и код номера в регистр 9 номера блока памяти, Так как первый и второй режим э1 работы запо гикаю1дего устройства могут происходить одновременно, то код HOf.tepa блока памяти через дешиф ратор номера блока памяти при наличия в регистре 10 соответств5ющего признака производит отключение от коммутаторов 2 и 3 того блока памяти, в который со стороны ЦВМ 16 до.п.кен быть ввод кодов програм Ы ком гутации, Использопакле в запоглинающем устройства- п блоков памяти, торов ввода и вывода, кольцевого регистра; регистра и дешифратора прнзкака и ,, позволяет значитель но уаелкчтгть быстродействие и раслии рит-Ъ функциональные возможности уст ройства, благодаря организации смены программ коммутации pemajotujSK блоков, работаюшдх в Ктультипрограм-мяом режиме, и совмещения процесса ввода кодов программы кохьмутации в какой-либо блок памяти с ггроцессо подключения .других блоков памяти ко входам к выходам решающих блоФор 1--1УЛ а изобретения Прогианмируемое э апог пшагощее уст ройство, содержашее блок сопряжения, подключенный информадионныг гя и упраклягэ.тсими вxoдa и и выходами ко Бхолу устройства,- буферный регис блок памяти и блок управления, о тл и ч а ю щ веся тем,что,с целью повыгиеник быстродействия устройства и рааиирения его области приме нения за счет смены програмз 1 решаю1цих блоков, в него введены допел нихелькые блоки памяти, комг татор ввода,, соединенный выходом с первы да ккформационными входами дополнительных блоков памяти, кoм yтaтop вывода, вход которого подключен к информационным выходам дополнительных блоков памяти, последовательно соединенные генератор синусоидального сигнала, формирователь тактовых и-1пульсов и кольцевой регистр, выхо.:ц которого подключен к первым управляющим входам комментатора ввода и ком:чутатора .вывода, регшаюшие блоки, входы - выходы которых подключены к соответствующим входам и выходам коммутаторов ввода и вывода, последовательно соединенные регистр номера блока памяти и дешифратор номера блока памяти, выход которого подключен к управлякидам входам дополнительных блоков памяти и ко вторым управляющим входам коммутатора ввода и ком.мутатора вывода, поспедовательно сое.диненные регистр признака и дешифратор признака, выход которого подключен к третьим управляющим входам коммутатора ввода и коммутатора вывода, буферный блок памяти, информационный и управляющий входы которого соединены соответственно с информационным и управляющим выходами блока сопряжения,информационными и первыми управляющими входами регистра признака и регистра номера блока памяти,информационный вывод буферного блока памяти соединен с первыми,вторыми и третьими информационными входами дополнительных блоков памяти, другой управляющий вход - с выходом блока управления,О.ДИН вход которого подключен к ВЫХО.ДУ формирователя тактовых импульсов, второй вход и. один из выходов - к блоку сопряжения третий вход - со вторыми yпpaвляюL шt- и вxoдa м регистра признака, регистра номера блока памяти и управляющим входом буферного ре истра, информационный вход которого подключен к .другому выходу ког 1мутатора вывода, а выХО.Ц - к блоку сопряжения. Источники информации, принятые во внимание при экспертизе 1, ОЕЕЕ Trans.Comput , 1973, NU , Р,41-46. 2„ Авторское свидетельство СССР по заявке f 2134167/18-24, кл.С 11 С 11/00, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения в многотерминальной вычислительной системе | 1984 |

|

SU1166124A1 |

| Устройство сопряжения | 1974 |

|

SU519704A1 |

| Устройство сопряжения интегрирующей машины с цифровой вычислительной машиной | 1974 |

|

SU599273A1 |

| Устройство для обмена информацией | 1977 |

|

SU741257A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Устройство для контроля цифровых интегральных схем | 1978 |

|

SU943747A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для сопряжения электроннойВычиСлиТЕльНОй МАшиНы C уСТРОйСТВОМВВОдА-ВыВОдА | 1979 |

|

SU809141A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

Авторы

Даты

1980-05-25—Публикация

1977-12-20—Подача