i. -., , . .

Изобретение отйосится к вычислитель ной технике и может быть использовано в качестве/программного устройства управленкя в периферических устройствах или других автономных устройствах.

Известны процессоры для применения в вычислительных машинах, для которых характерны большие объемы памяти, высокое быстродействие, большой пропент математических операций, поэтому процессоры сложны и, в то же время, не приспособлены для операций периферийных устройств.

Известно вычислительное устройство содержащее арифметический блок, память микрокоманд, схему формирования очередной микрокоманды, рабочие регистры, а.&е схемы выбора, поразрядную схему И, поразрядную схему ИЛИ. Это устройство обеспечивает выполнение операций слрже- ния, вычитания, сдвига, логического ум ножения, логического сложения и т.д., а также обмен информацией между регистрами 11/.

.Недостатком этого устройства, ограничивающюл возможность его применения в малых устройствах управления, периферийных устройствах, является большая разрядность памяти микрокоманд и отсутствие блоков связей, обеспечивающих по программе обмен данными непосредственно между внешними устройствами. .

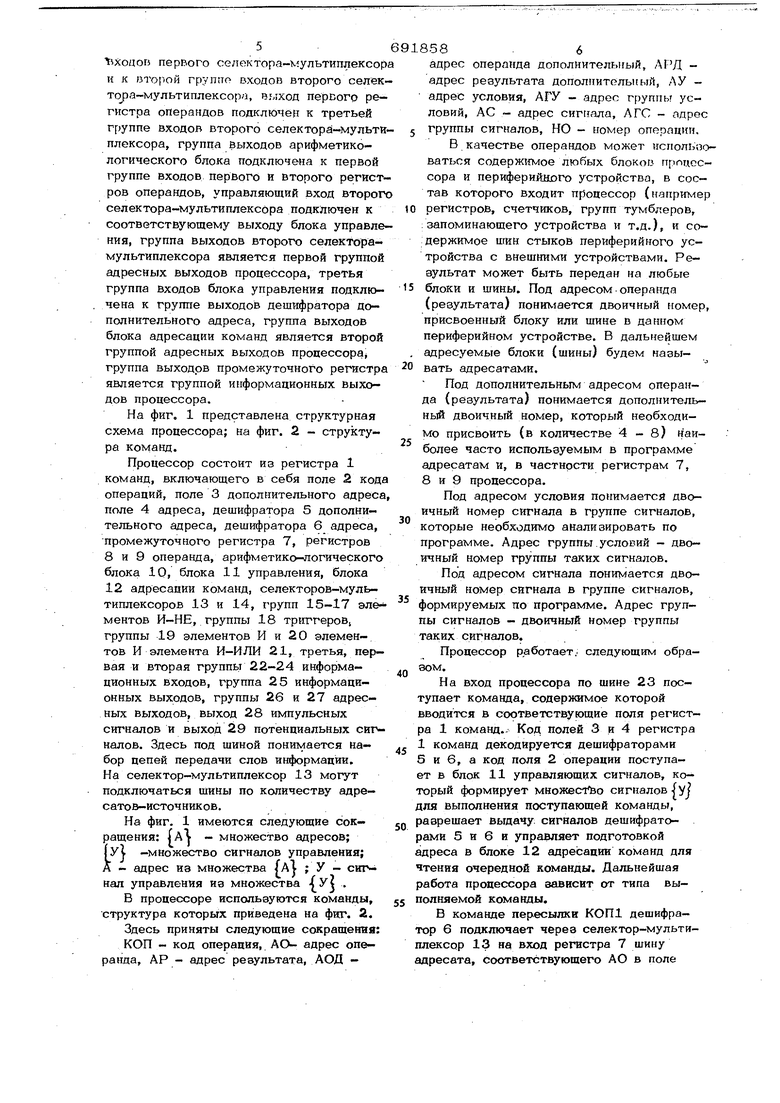

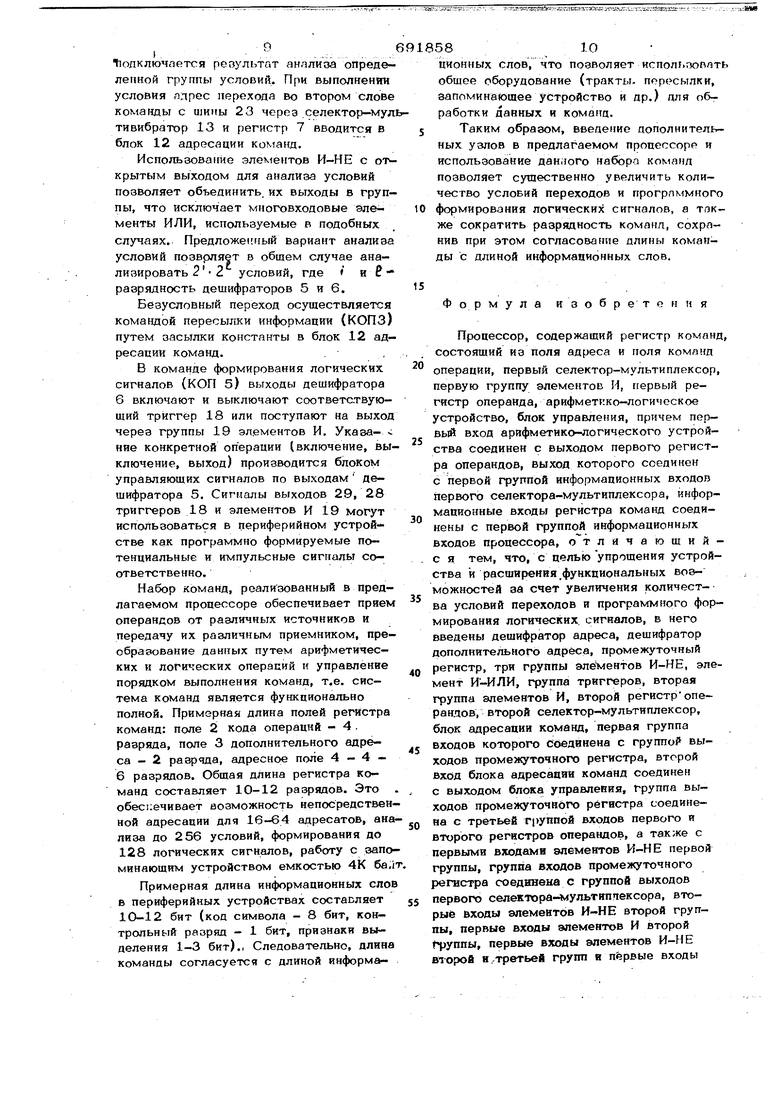

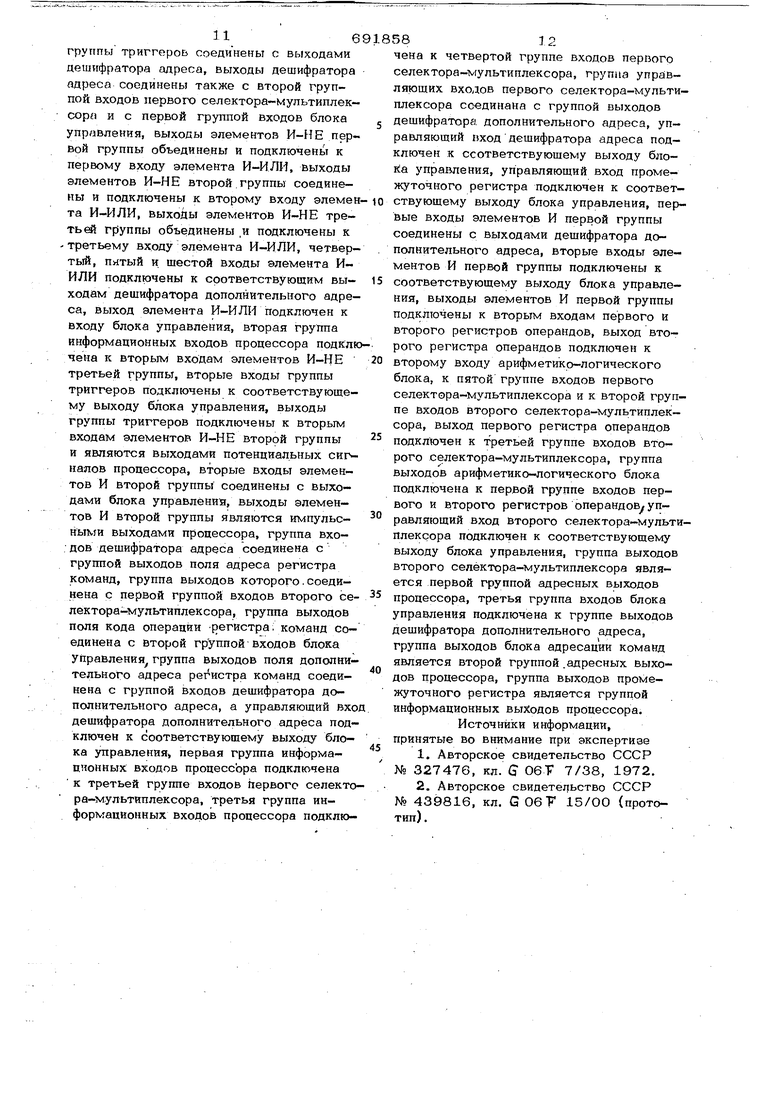

Наиболее близким к изобретению по технической сущности является вычислительное устройство, содержащее арифметико-логический блок, выходной коммутатор, регистр операнда, регистры общего иазначения, регистр кода операций, выходной коммутатор, блок управляющих сигналов, блок сопряжения с оперативным запоминающим устройством, адресный регистр, две группы элементов И, регистр микрокоманд, содержащий поле адреса микрокоманды, выходы которого соединены с входами управляющих сигналов, Поле приема, выходы которого соединены с входами входвого коммутатора., поле выдачи, выходы которого соединены с входами выходного коммутатора, поле ветвления, выходы которого соединены с вторым входом блока управляющих сигналов, поле адреса и триггер удлинения адреса 2j. Недостатком устройства является большая длина микрокоманд, что обусловлено большим количеством полей в регистре микрокоманд и непосредственным соединением выходов полей регистра микрокоманд с управляемыми блока 1И устройства. Вторым недостатком являет ся ограничение возможности по количест ву условий ветвления программ и програ ному формированию логических (управляющих) сигналов. Целью изобретения является упрощение устройства; и расширение функциональных возможностей аа счет увеличения количества условий переходов программного формирования логических сигналов. Поставленная цель достигается тем, что в процессор введены дешифратор адреса, дешифратор дополнительного адреса, промежуточный регистр, три группы элементов И-НЕ, елемент И-ИЛИ, группа триггеров, вторая группа элемен тов И, второй регистр операндов, второй селектор-мультиплексор, блок адресации команд, первая группа входов которого соединена с группой выходов промежуточного регистра, второй вход блока ад- ресации команд соединен с выходом бло ка управления, группа выходов промежуточного регистра соединена с третьей группой входов первого и второго регис ров операндов, а также с первыми входами элементов И-НЕ первой группы, .группа входов промежуточного регистра соединена .с группой выходов первого с лектора-мультиплексора, вторые входы элементов Й-НЕ второй группы, первые входы элементов И второй группы, первые входы элементов И-НЕ второй и третьей групп и первые входы группы триггеров соединены с выходами дешиф ратора адреса, выходы которого соединены также с второй группой входов первого селектора-мультиплексора и с первой группой входов блока управления .выходы элементов И-НЕ первой группы объединены и подключены к первому входу элемента И-ИЛИ, выходы элементов И-НЕ второй группы объединены и подключены к второму входу элемента И-ИЛИ, выходы элементов И-НЕ третье группы объс динены и подключены к третьему входу элемента И-ИЛИ, четвертый, пятый и шестой входы элемента И-ИЛИ подключены к соответствующим выходам дешифратора дополнительного адреса, выход элемента И-ИЛИ подключен к входу блока управления, вторая группа информационных входов процессора подключена к вторым I входам элементов И-biE третьтьей группы, вторые входы группы триггеров подключены к соответстующему выходу блока управления, выходы группы триггеров подключены к вторым входам элементов И-НЕ второй группы и являются выходами потейцИальных сигналов процессора, вторые входы элементов И второй группы соединены с выходами блока управления, выходы элементов И второй группы являются импульсными выходами процессора, группа входов дешифратора адреса соединена с группой выходов поля адреса регистра команд, группа Выходов которого Соединена с первой группой входов второго селектора-мультиплексора, группа выходов поля кода операции регистра команд соединена с второй группой входов блока управления, группа выходов поля дополнительного адреса регистра команд соединена с группой входов дешифратора дополнительного адреса, а управляющий вход дешифратора дополнительного адреса подключен к соответствующему выходу блока управления, пербая группа информационных входов процессора подключена к третьей группе входов первого селектора-мультиплексора, третья группа информационных входов процессора подключена к четвертой группе входов -первого селектора-мультиплексора, группа управляющих входов которого соединена с группой выходов дешифратора дополнительного адреса, управляющий вход дешифратора адреса подключен к соответствующему выходу блока управления, управляющий вход промежуточного регистра подключен к соответствующему выходу блока управления, первые входы элементов И первой группы соединены с выходами дешифратора дополнительного адреса, вторые входы элементов И первой группы подключены к соответстующему выходу блока управления, выходы элементов И первой группы подключены к вторым входам первого и второго регистров операндов,, выход Рторого регистра операндов подключен к второму входу арифметико-логического блока, к пятой группе tixoaoB первого селектора-мультиплексо и к второй группо входов второго селек тора-мультиплексорЗ, в;лход первого ре гистра операндов подключен к третьей группе входов второго селектора-мульт плексора, группа выходов арифметикологического блока подключена к первой группе входов первого и второго регист ров операндов, управляющий вход второг селектора-мультиплексора подключен к соответствующему выходу блока управле ния, группа выходов второго селекторамультиплексора является первой группой адресных выходов процессора, третья группа входов блока управления подключена к группе выходов дешифратора дополнительного адреса, группа выходов блока адресации команд является второй группой адресных выходов процессора группа выходов промежуточного регистр является группой информационных выходов процессора. На фиг. 1 представлена структурная схема процессора; на фиг. 2 - структура команд. Процессор состоит из регистра 1 команд, включающего в себя поле 2 код операций, поле 3 дополнительного адрес поле 4 адреса, дешифратора 5 дополнительного адреса, дешифратора 6 адреса, промежуточного регистра 7, регистров 8 и 9 операнда, арифметико-логического блока 10, блока 11 управления, блока 12 адресации команд, селекторов-мультиплексоров 13 и 14, групп 15-17 эле ментов И-НЕ, группы 18 триггеров, группы 19 элементов И и 20 элементов И элемента И-ИЛИ 21, третья, первая и вторая группы 22-24 информационных входов, группа 25 информационных выходов, группы 26 и 27 адресных выходов, выход 28 импульсных сигналов и выход 29 потенциальных сиг налов. Здесь под щиной понимается набор цепей передачи слов информации. На селектор-мультиплексор 13 могут подключаться шины по количеству адресатов-источников. На фиг. 1 имеются следующие сокращения: (А - множество адресов; iy -множество сигналов управления; - адрес из множества /л ; У - сигнал управления из множества У . В процессоре используются команды, структура которых приведена на фнг. 2. Здесь приняты следующие сокращения: КОП - код операция, АО- адрес операнда, АР - адрес результата, АОД адрес операнда дополнительный, ЛГД адрес результата дополнительный, ЛУ адрес условия, АГУ - адрес группы условий, АС - адрес сигнала, А ГС - лдрес группы сигналов, НО - номер операции. В качестве операндов может испольооваться содерж1гмое любых блокогз процессора и периферийного устройства, в состав которого входит процессор (наприхчер регистров, счетчиков, групп тумблеров, запоминающего устройства и т.д.), и содержимое шин стыков периферийного устройства с внешними устройствами. Результат может быть передан на любые блоки и шины. Под адресом операнда (результата) понимается двоичный номер, присвоенный блоку или щине в данном периферийном устройстве. В дальнейшем адресуемые блоки (шины) будем называть адресатами. Под дополнительным адресом операнда (результата) понимается дополнительный двоичный номер, который необходимо присвоить (в количестве 4-8) наиболее часто используемым в программе адресатам и, в частности регистрам 7, 8 и 9 процессора. Под адресом условия понимается двоичный номер сигнала в группе сигналов, которые необходимо анализировать по программе. Адрес группы.условий - двоичный номер группы таких сигналов. Под адресом сигнала понимается двоичный номер сигнала в группе сигналов, формируемых по программе. Адрес группы сигналов - двоичный номер группы таких сигналов. Процессор работает., следующим образом. На вход процессора по шине 23 поступает команда, содержимое которой вводится в соответствующие поля регистра 1 команд.. Код полей 3 и 4 регистра 1 команд декодируется дешифраторами 5 и 6, а код поля 2 операции поступает в блок 11 управляющих сигналов, коорый формирует множество сигналов |yj ля выполнения поступающей команды, азрешает выдачу сигналов дешифратоами 5 и 6 и управляет подготовкой дреса в блоке 12 адресации команд для тения очередной комаиды. Дальнейшая работа процессора зависит от типа выолняемой команды. В команде пересылки КОП1 дешифраор 6 подключает через селектор-мультилексор 13 на вход регистра 7 шину дресата, соответствующего АО в поле 4 регистра, регистра 1 команд. По сигналу V с блока 11 управляюших сигналов содержимое данной шины вводится в регистр 7 и становится доступны 1 всем адресам, поскольку выход t регистра 7 соединены с входами всех адресатов. Сиг налом А с дешифратора 5 через элементы И 20 разрешается ввод операнда в соответствии с дополнительным адресом поля 3 регистра Г команд. Таким обра8ОМ, в данной команде пересылается с любого адресата (АО) адресату, имеющему дополнительный адрес. В команде пересылки КОП2 пересылается содержимое адресатов, имеющих дополнительный адрес (АОД) любому другому адресату. При этом на регистр 7 через селектор-мультиплексор 13 подключается шина адресата сигналом А с дешифратора 5, а с выхода регистра 7 - сигналами дешифратора 6 через элементы И 19. Поскольку селектором -мульти плексором 13 управляют дешифраторы 5 и 6, то чтобы Исключить одновременное подключение двух шин, дешифраторы вклю чаются в разное время. При этом после включения первого (по времени) дешифратора регистр 7 сохраняет выбранный операнд на время выполнения команды. В команде пересылки КОПЗ содержимое второго слова команды (константа) с входа 23 через селектор-мультиплексор 13 и регистр 7 вводится по сигналам с дешифратора 6 адресата, в соответствии с АР поля 4 регистар 1 коман Прием операнда из запоминающего устройства (на чертеже не показано) и ввод в запоминающее устройство производится рассмотренными командами пере сыл1:и КОП1 и КОП2 соответственно. При этом в качестве адресата ячейки запоминающего устройства Используется содержимое одного из регистров 8 или 9 Если операнд должен приниматься (пере даваться) в регистр 8, то адрес помещают в регистр 9 и наоборот. Коммутация адреса производится селектороммультиплексором 14 по сигналам с дешифратора 5. В этом варианте обращени . к запоминающему устройству адрес должен быть записан в регистр 8 (или 9) в предшествующих командах. Возможно обращение к запоминающему устройству с указанием адреса в этой же команде. Для этого в составе команды поступает сокращенный адрес, ко1ЬрыЙ вводит ся в поле 4 регистра 1 команд,откуда через селектор14 поступает в группу дресных выходов 26 в качестве млацших разрядов адреса. В качестве старших разрядов используется константа, ормируемая при этой кома1ще непосредственно в селекторе 14. Колич(ство непосредствецно адресуемых ячеек ЗУ определяется разр$шностью поля 4 регистра комавд. Возможность непосредственной адресации к ЗУ позволяет исключить из состава процессора традиционные оперативные регистры (сверхоперативное запоминающее устройство). В рассмотренных операциях пересылка информации производится или за одну команду (если один из адресатов имеет дополнительный адрес) или за две команды (при отсутствии дополнительных адресов). Адресация по дополнительному адресу позволяет, с одной стороны, сократить длину поля адреса одного из операндов (поскольку дополнительный адрес присвоен небольшому количеству адресов) и с другой стороны, выполнять большинство пересылок (поскольку дополнительный адрес присвоен наиболее часто используемьп адресатам) по двухадресной системе. В Команде приобразования информации КОП6 блок 11 управляющих сигналов управляет работой арифметико-логического блока 10, который в зависимости от номера операции на дешифраторе 6, производит одну из операций (сложение, логическое умножение и т.д.) над операндами регистров 8 и 9. Результат заносится по сигналам с дешифратора 5 и схем 20 И в один из регистров 8 и 9. Поле 4 адреса и адресный дешифратор 6 используются в этой команде для о&работки кода операции, что позволяет без дополнительных затрат оборудования на операционную час-.-ь реализовать достаточное количество операций преобра-, зования информации. Состояние арифметико- югического блока 10 при выполнении команды преобразования информация (переполнение, знак и др.) выдается на блок 11 управления и учитывается при завершении операции. В команде условного перехода (коп 4) адрес условия поступает в поле 4 регистра 1 Команд и дешифрируется дешифратором 6, выходы которого подключают для анализа через элементы 15-17 И-НЕ определенный сигнал в каждой группе условий. По сигналу с дешифратора 5 на вход блока 11 управляющих сигналов элемент И-ИЛИ 21 ,О Тюдключается результат анализа определепной группы условий. При выполнении условия алрес перехода во втором слове команды с шины 23 через .селектог.)-мул тивибратор 13 и регистр 7 вводится в блок 12 адресации . Использование элементов И-НЕ с открытым выходом для анализа условий Позволяет объединить, их выходы в группы, что исключает многовходовые элементы ИЛИ, используемые в подобных случаях. Пpeдлoжel F ый вариант анализа условий позврляет в общем случае анализировать 2 2 условий, где « и 8 разрядность дешифраторов 5 и 6. Безусловный переход осуществляется Командой пересылки информации (КОПЗ) путем засылки константы в блок 12 адресации команд. В команде формирования логических сигналов (КОП 5) выходы дешифратора б включают и выключают соответствующий триггер 18 или поступают на выход через группы 19 элементов И, Указа- -: ние конкретной операции (включение, выключение, выход) производится блоком управляющих сигналов по выходам дешифратора 5. Сигналы выходов 29, 28 триггеров 18 и элементов И 19 могут использоваться в периферийном устройстве как программно формируемые потенциальные и импульсные сигналы соответственно. Набор команд, реализованный в предлагаемом процессоре обеспечивает прием операндов от различных источников и передачу их различным приемником, преобразование данных путем арифметических и логических операций и управление порядком выполнения команд, т.е. система команд является функционально Полной. Примерная длина полей регистра команд: поле 2 кода операций - 4 , разряда, поле 3 дополнительного адреса - 2 разряда, адресное поле 4 - 4 6 разрадов. Общая длина регистра команд составляет 10-12 разрядов. Это . обеспечивает возможность непосредственной адресации для 16-64 адресатов, анализа до 256 условий, формирования до 128 логических сигналов, работу с запоминающим устройством емкостью 4К баЛт Примерная длина информационных слов в периферийных устройствах составляет 10-12 бит (код символа - 8 бит, контрольный разряд - 1 бит, признаки выделения 1-3 бит)., Следовательно, длина команды согласуется с длиной информа- 858 ционных слов, что позволяет испольгюппть общее оборудование (тракты. пор(: сылки, запоминающее устройство и др.) для обработки данных и команд. Таким образом, введение дополнительных узлов в предлагаемом процессоре и использование данного набора команд позволяет существенно увеличить количество условий переходов и программного формирования логических сигналов, а т,-экже сократить разрядность команд, сохранив при этом согласование длины команды с длиной информационных слов. Формула изобретения Процессор, содержащий регистр команд, состоящий из поля адреса и поля компяд операции, первый селектор-мультиплексор, первую группу элементов И, первый регистр операнда, арифметико-логическое устройство, блок управления, причем первый вход арифметико-логического устройства соединен с выходом первого регистра операндов, выход которого соединен с первой группой информационных входов первого селектора-мультиплексора, информационные входы регистра команд соединены с первой группой информационных входов процессора, отличающийс я тем, что, с цельюупрощения устройства и расширения функциональных вое- можностей за счет увеличения количества условий переходов и программного формирования логических сигналов, в него введены дешифратор адреса, дешифратор дополнительного адреса, промежуточный регистр, три группы элементов И-НЕ, элемент И-ИЛИ, группа триггеров, вторая группа элементов И, второй регистроперандов, второй селектор-мультиплексор, блок адресации команд, первая группа входов которого соединена с группой выходов промежуточного регистра, второй вход блока адресации команд соединен с выходом блока управления, группа выходов промежуточного регистра соединена с третьей групцой входов первого я второго регистров операндов, а также с первыми входами элементов И-НЕ первой группы, группа входов промежуточного регистра соединена с группой выходов первого селек-гора- мультиппексора, вторые входы элементов И-НЕ второй группы, первые входы элементов И второй группы, первые входы элементов И-НЕ второй н,-третьей групп и первые входы группы триггеров соединены с выходами дешифратора адреса, выходы дешифратора адреса соединены также с второй группой входов первого селектора-мультиплексора и с первой группой входов блока управления, выходы элементов И-НЕ первой группы объединены и подключены к первому входу элемента И-ИЛИ, выходы элементов И-НЕ второй. группы соединены и подключены к второму входу элемен та И-ИЛИ, выходы элементов И-НЕ третьей группы объединены ,и подключены к -третьему входу элемента И-ИЛИ, четвертый, пятый и шестой входы элемента ИИЛИ подключены к соответствующим выходам дешифратора дополнительного адреса, выход элемента И-ИЛИ подключен к входу блока управления, вторая группа информационных входов процессора подклю чена к вторым входам элементов И-НЕ третьей группы, вторые входы группы триггеров подключены к соответствующему выходу блока управления, выходы группы триггеров подключены к вторым входам элементов И-НЕ второй группы и являются выходами потенциальных сигналов процессора, вторые входы элементов И второй группы соединены с выходами блока управления, выходы элементов И второй группы являются импульсными выходами процессора, группа входов дешифратора адреса соединена с группой выходов поля адреса регистра команд, группа выходов которого.соединена с первой группой входов второго се лектора-мультиплексора, группа выходов поля кода операции -регистра: команд соединена с второй группой входов блока управления группа выходов поля дополнительного адреса регистра команд соединена с группой входов дешифратора дополнительного адреса, а управляющий вхо дешифратора дополнительного адреса под ключен к соответствующему выходу блока управления первая группа информационных входов процессора подключена к третьей группе входов Первого селекто ра-мультиплексора, третья группа информационных входов процессора подключена к четвертой группе входов первого селектора-мультиплексора, группа управляющих Входов первого селектора-мультиплексора сс-единана с группой выходов дешифратора дополнительного адреса, управляющий вход дешифратора адреса подключен к соответствующему выходу блока управления, управляющий вход промежуточного регистра подключен к соответствующему выходу блока управления, первые входы элементов И первой группы соединены с выходами дешифратора дополнительного адреса, вторые входы элементов И первой группы подключены к соответствующему выходу блока управления, выходы элементов И первой группы подключены к вторым входам первого и второго регистров операндов, выход второго регистра операндов подключен к второму входу арифметико-логического блока, к пятой группе входов первого селектора-мультиплексора и к второй группе входов второго селектора-мультиплексора, выход первого регистра операндов подключен к третьей группе входов второго селектора-мультиплексора, группа выходов арифметико-логического блока подключена к первой группе входов первого и второго регистров операндов управляющий вход второго селектора-мультиплексора подключен к соответствующему выходу блока управления, группа выходов второго селектора-мультиплексора является первой группой адресных выходов процессора, третья группа входов блока управления подключена к группе выходов дещифратора дополнительного адреса, группа выходов блока адресации команд является второй группой .адресных выходов процессора, группа выходов промежуточного регистра является группой информационных выходов процессора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 327476, кл. G ОбТ 7/38, 1972. 2,Авторское свидетельство СССР № 439816, кл. G06F 15/ОО (прототип) .

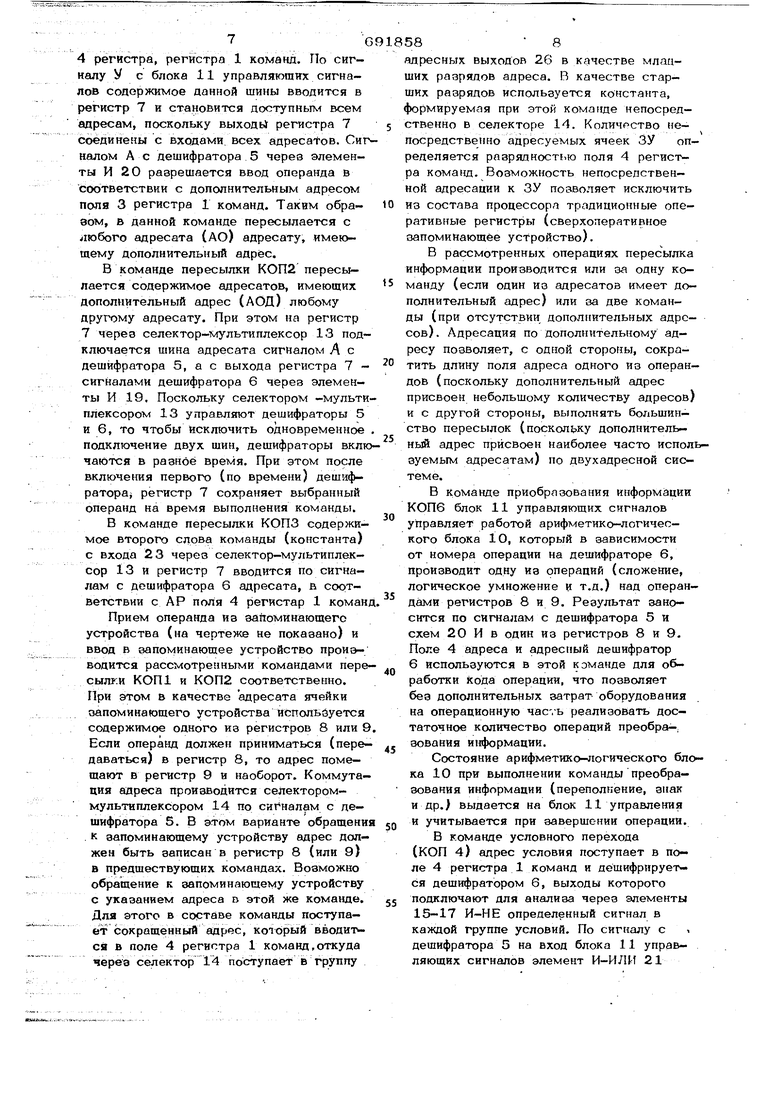

I КОП1 I АО АРД

АР AOa

КОП2

КОПЗ ДЯ I

Константа

КОП5 АС

но

KonsKoHOHdv пересыпки операндов

Копанда условною перехода

/Команда срорниообания логических си warns

Команда преобразования индзормации

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1247884A1 |

| Процессор цифровой вычислительной машины | 1979 |

|

SU1164723A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Процессор параллельной обработки | 1990 |

|

SU1797126A1 |

| Программируемый сопроцессор | 1988 |

|

SU1675880A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

Авторы

Даты

1979-10-15—Публикация

1977-06-17—Подача