3-94 циклических программ, содержащее блок адресной памяти, адресный вход которого является первым адресным входом устройства, счетчик номера сектора, первый управляющий вход которого соединеи с управляющим выходом 6JloKa адресной памяти, а первый разрядный выход - с управляющим входом блока адресной памяти, блок буферной па- мяти команд, блок памяти битов значимости, блок памяти битов ожидания, адресные входы которых соединены со вторым адресным входом устройства, информационный вход блока буферной памяти команд является информационным

входом устройства, первый коммутатор, счетчик считывания, первый, второй разрядные выходы которого соединены с первым входом первого коммутатора и с первыми входами считывания блоков 2о памяти битов значимости и ожидания соответственно, регистр очередного сектора, регистр адреса назначения, первые информационные входы которых соединены со вторым разрядным выходом 25 счетчика номера сектора, вторые информационные входы регистра очередного сектора и регистра адреса назначения и второй вход первого коммутатора соединены с информационным выходом блока адресной памяти, разрядный выход регистра очередного сектора соединен с третьим входом первого коммутатора, выход которого соединен со входом считывания блока буферной памя ти команд и с информационным входом счетчика считывания, а разрядный выход регистра адреса назначения соединен со вторыми входами считывания блоков памяти битов значимости и ожидания и с выходом адреса назначения устройства, первый, второй,третий и четвертый регистры команд, информационные входы которых соединены с первым выходом блока буферной памяти команд, узел распаковки командных слов, каждый информационный вход которого соединен с разрядным выходрм соответствующего регистра команд, блок триггеров значимости команд, нулевой вход которого соединен с блокировочным выходом блока буферной памяти команд, вход сброса блока триггеров значимости команд соединен с обнуляющим выходом узла распаковки командных слов. а выход соединен со входом значимости

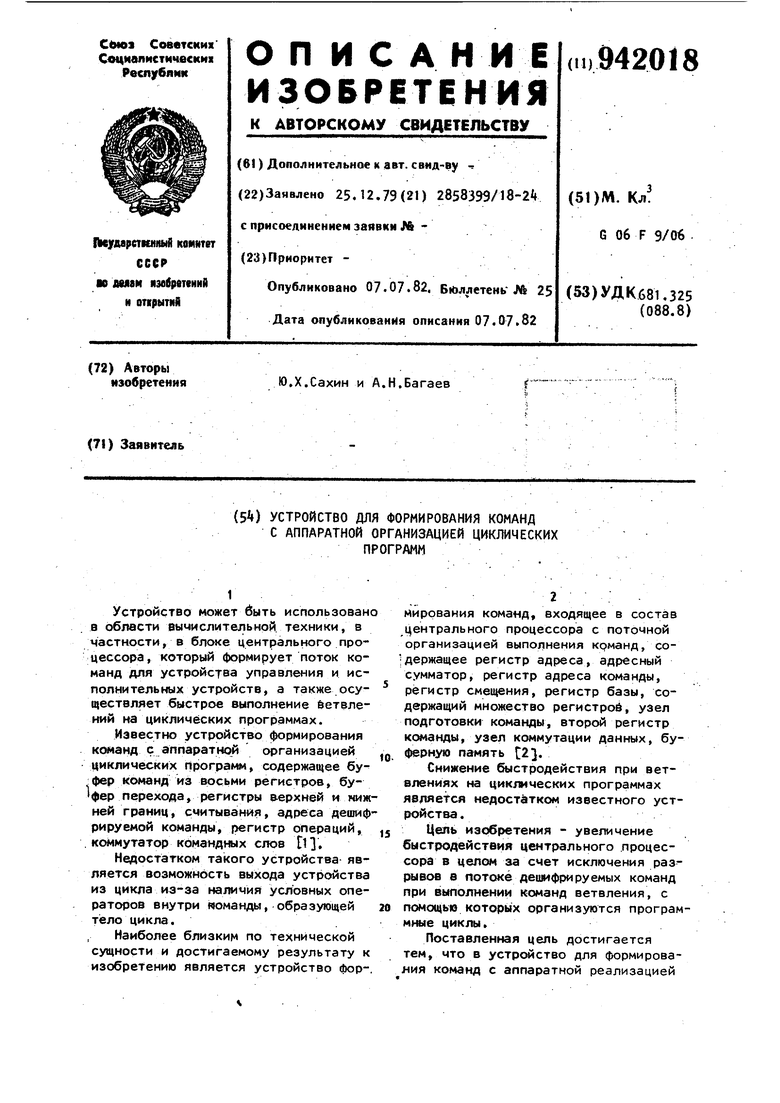

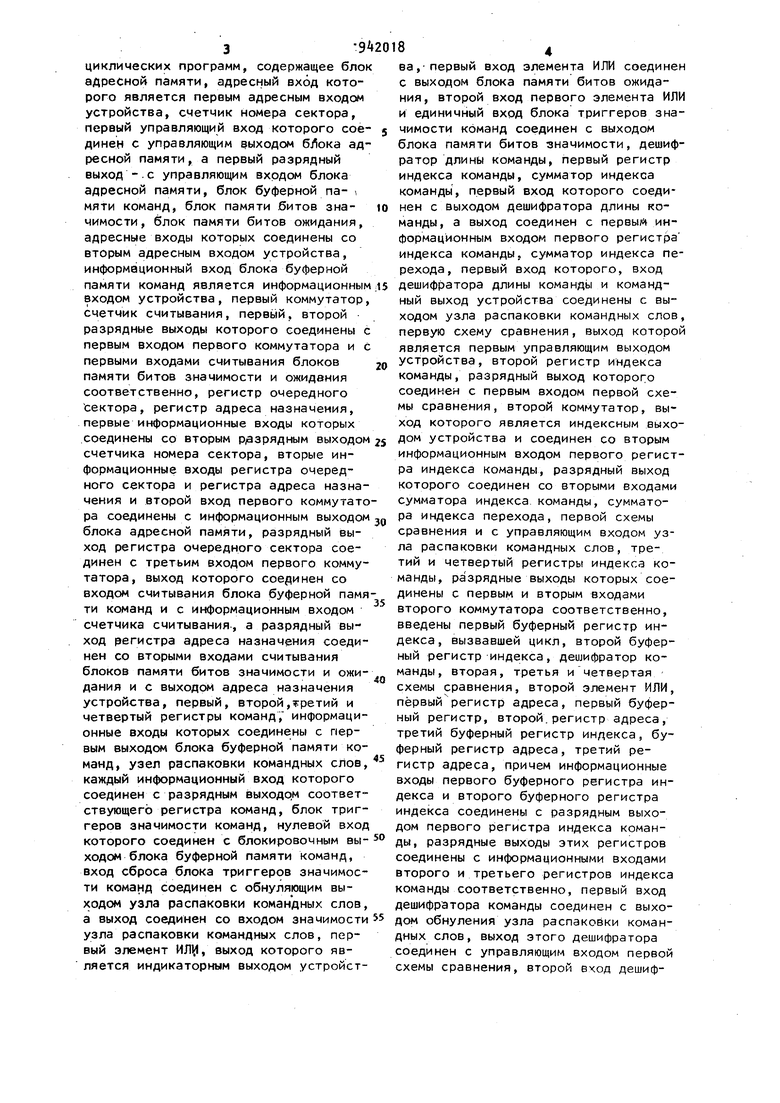

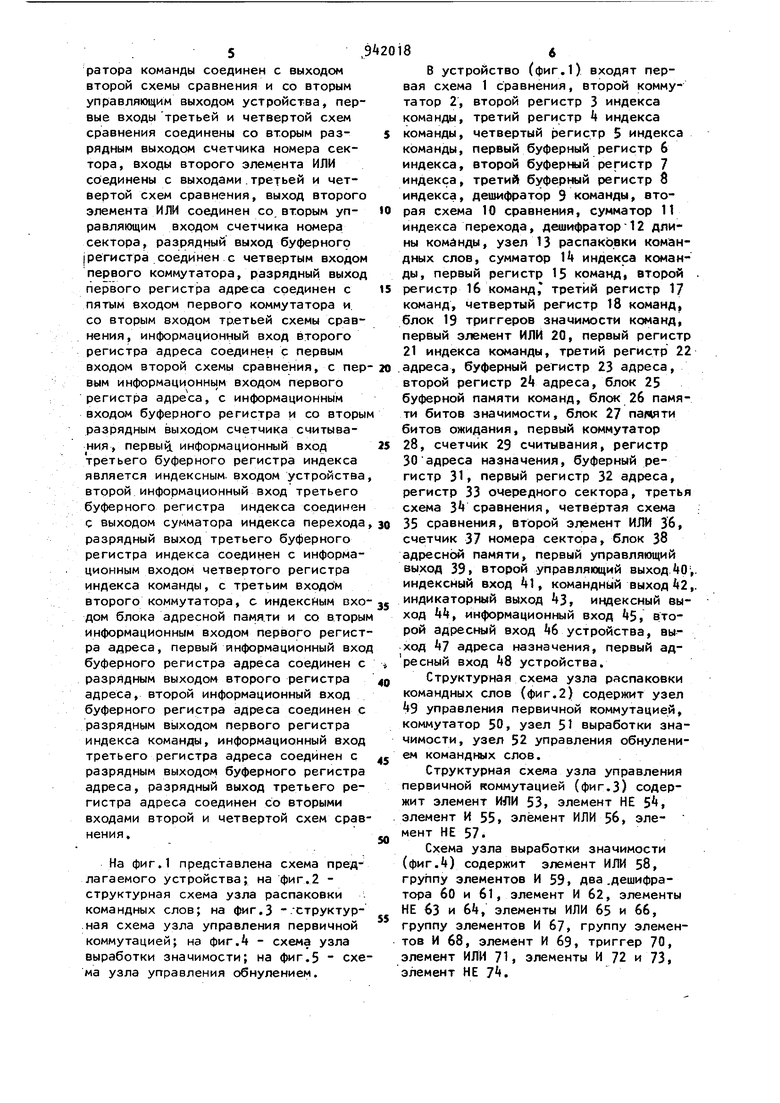

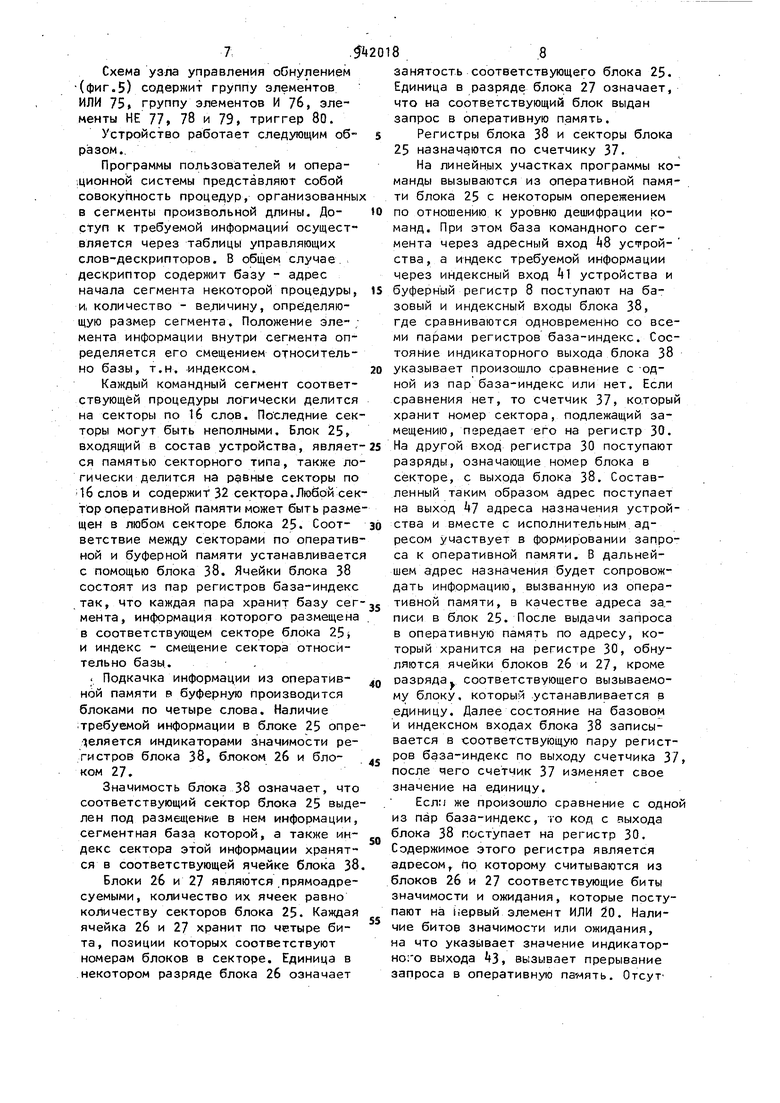

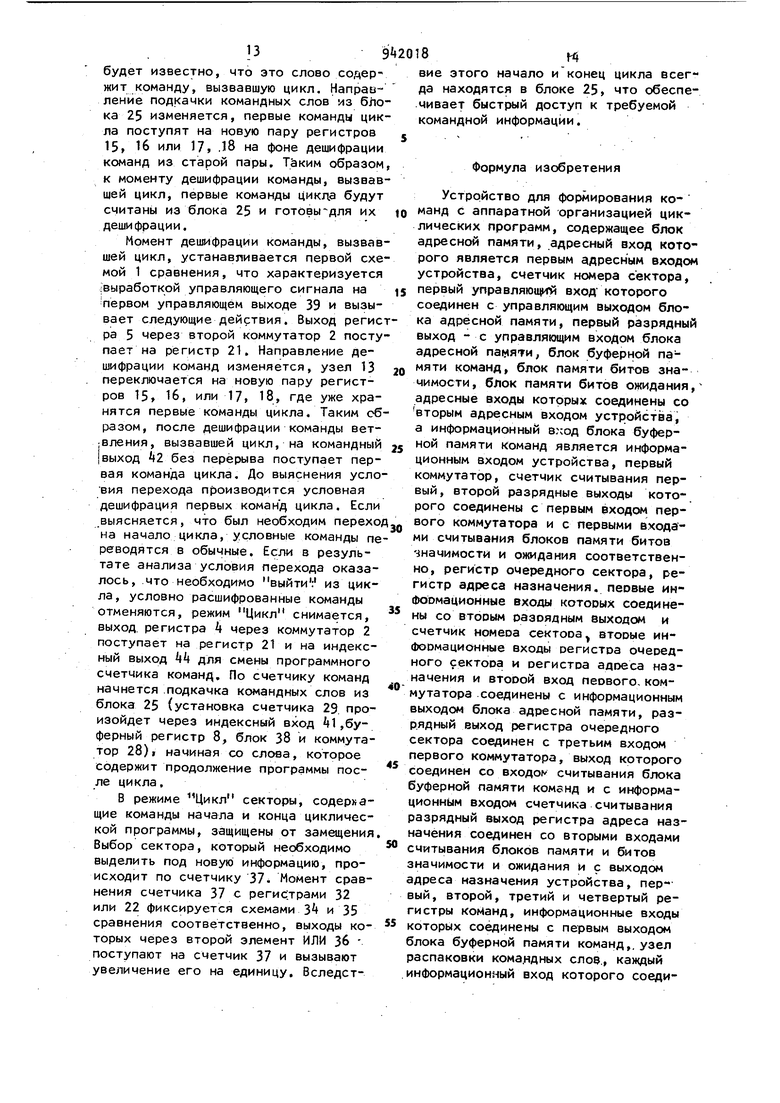

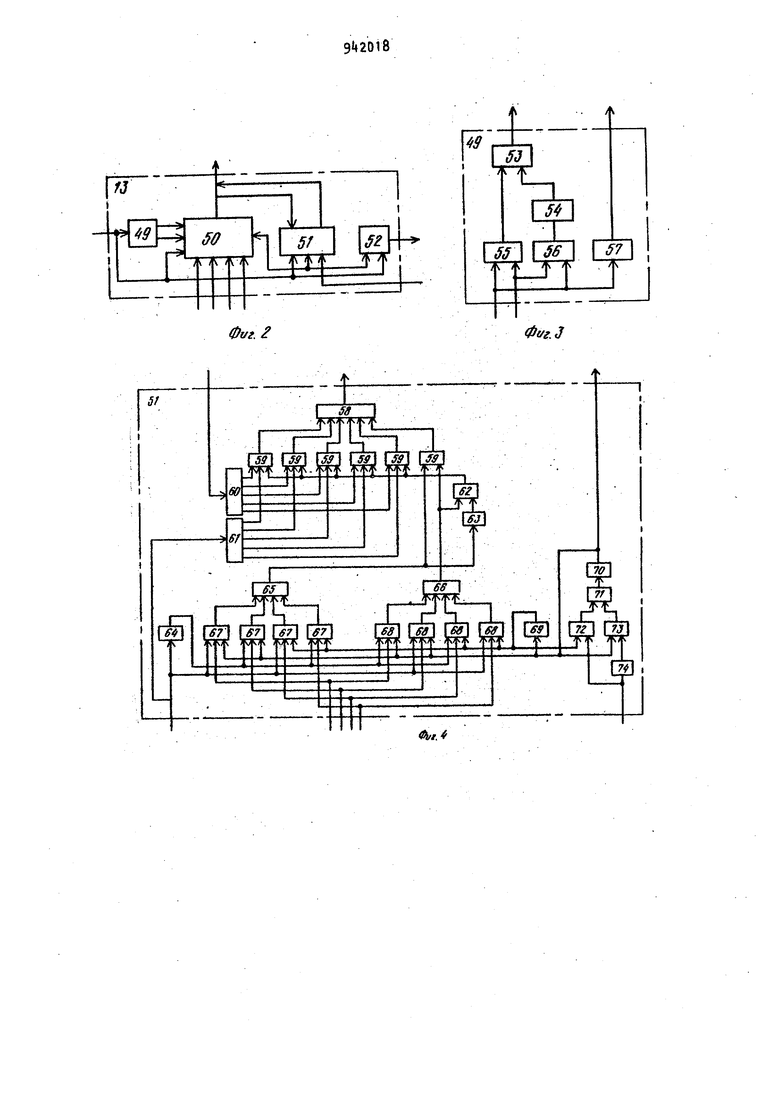

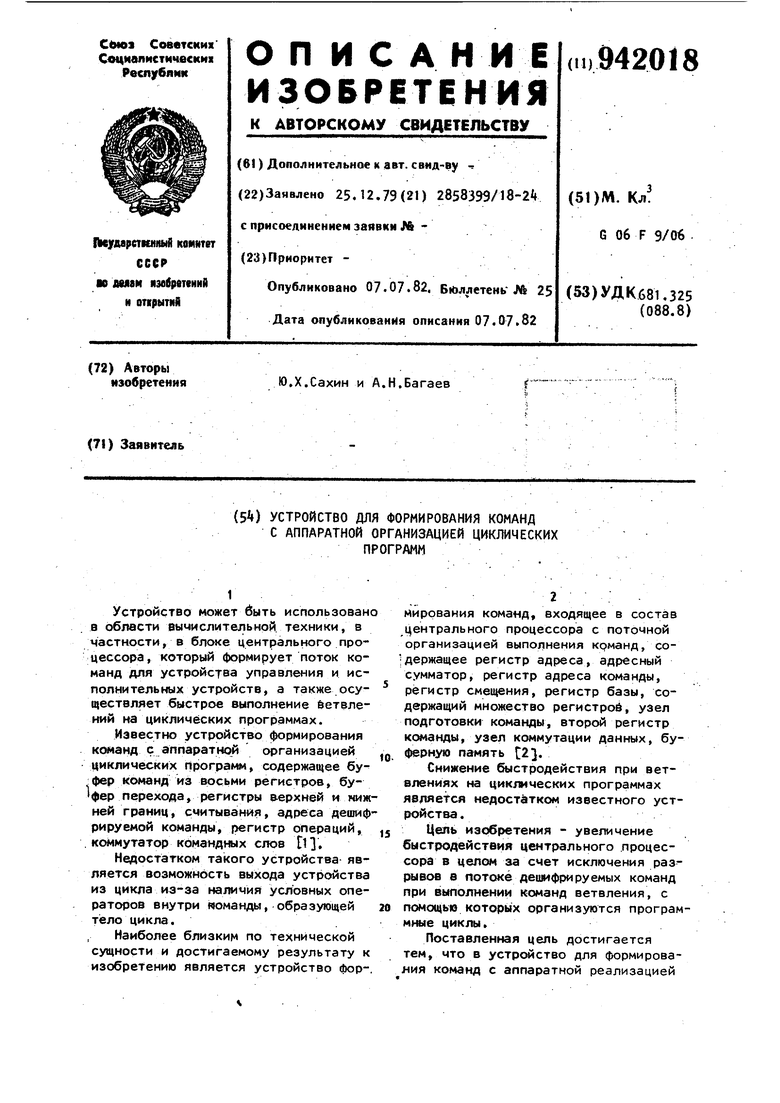

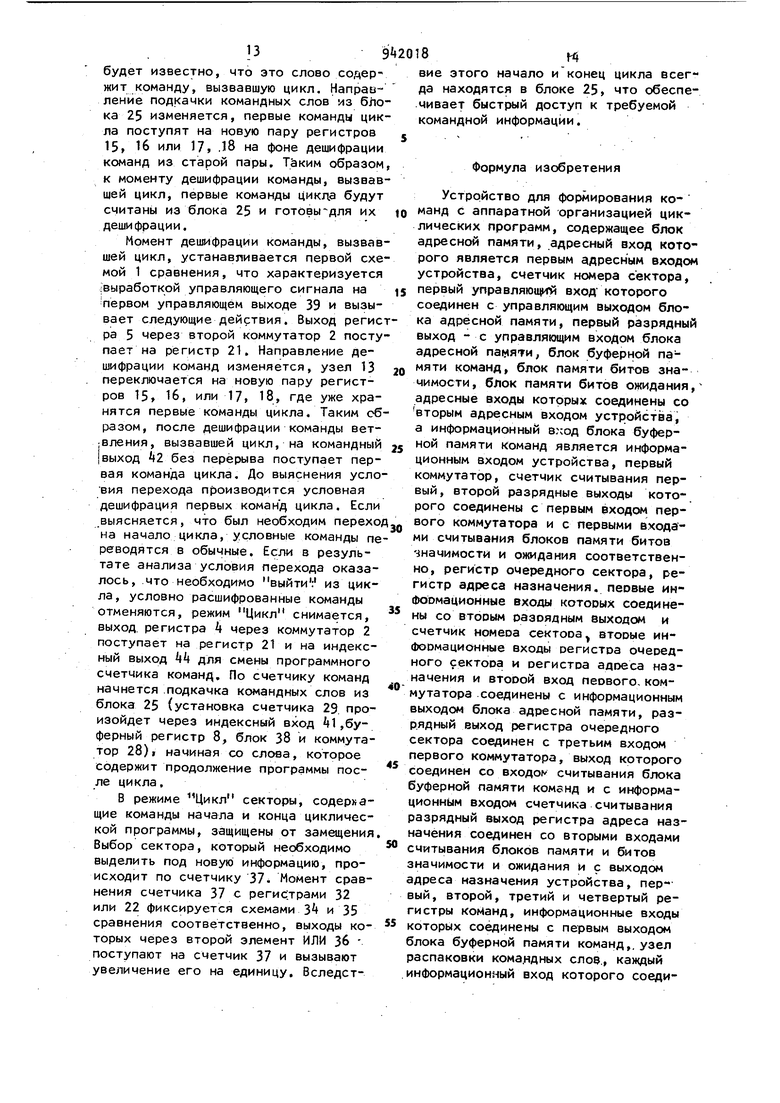

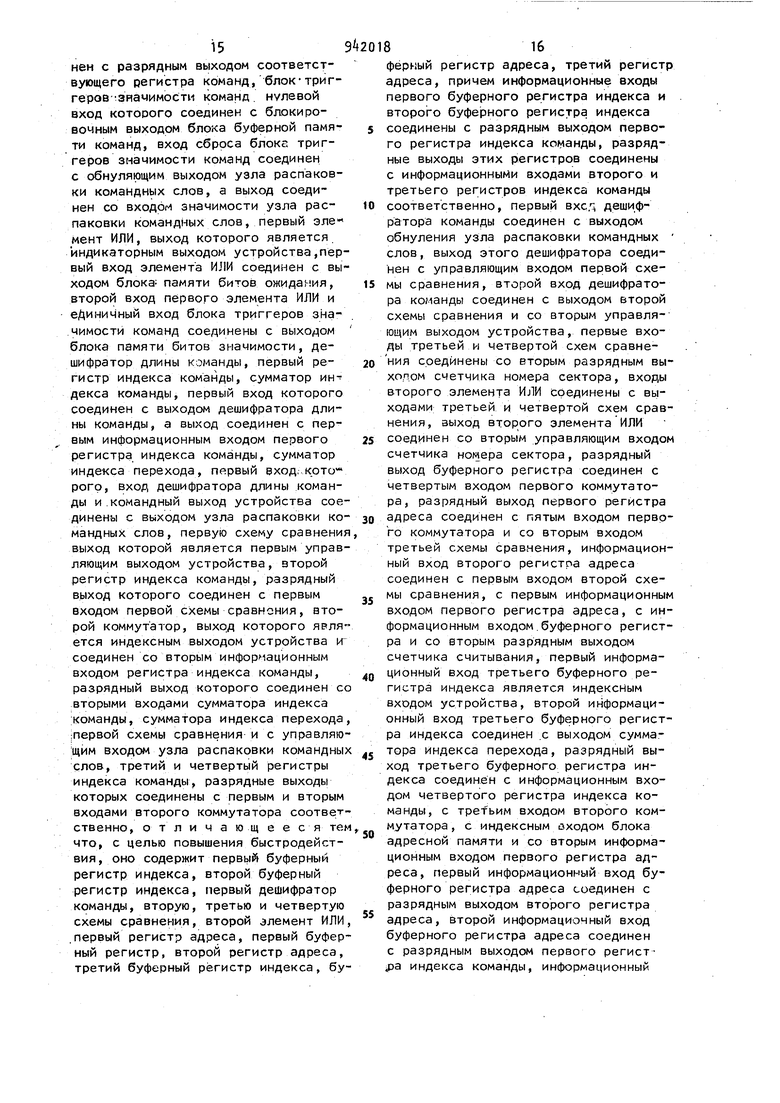

узла распаковки командных слов, первый элемент ИЛУ, выход которого является индикаторным выходом устройстный выход устройства соединены с выходом узла распаковки командных слов, первую схему сравнения, выход которой является первым управляющим выходом устройства, второй регистр индекса команды, разрядный выход которого соединен с первым входом первой схемы сравнения, второй коммутатор, выход которого является индексным выходом устройства и соединен со вторым информационным входом первого регистра индекса команды, разрядный выход которого соединен со вторыми входами сумматора индекса команды, сумматодных слов, выход этого дешифратора соединен с управляющим входом первой схемы сравнения, второй вход дешиф8ва,-первый вход элемента ИЛИ соединен с выходом блока памяти битов ожидания, второй вход первого элемента ИЛИ и единичный вход блока триггеров значимости команд соединен с выходом блока памяти битов значимости, дешифратор длины команды, первый регистр индекса команды, сумматор индекса команды, первый вход которого соединен с выходом дешифратора длины команды, а выход соединен с первый информационным входом первого регистра индекса команды, сумматор индекса перехода, первый вход которого, вход дешифратора длины команды и командра индекса перехода, первой схемы сравнения и с управляющим входом узла распаковки командных слов, третий и четвертый регистры индекса команды, разрядные выходы которых соединены с первым и вторым входами второго коммутатора соответственно, введены первый буферный регистр индекса, вызвавшей цикл, второй буферный регистр индекса, дешифратор команды, вторая, третья и четвертая схемы сравнения, второй элемент ИЛИ, пёрвый регистр адреса, первый буферный регистр, второй.регистр адреса, третий буферный регистр индекса, буферный регистр адреса, третий регистр адреса, причем информационные входы первого буферного регистра индекса и второго буферного регистра индекса соединены с разрядным выходом первого регистра индекса команды, разрядные выходы этих регистров соединены с информационными входами второго и третьего регистров индекса команды соответственно, первый вход дешифратора команды соединен с выходд обнуления узла распаковки команратора команды соединен с выходом второй схемы сравнения и со вторым управляющим выходом устройства, первые входы третьей и четвертой схем сравнения соединены со вторым разрядным выходом счетчика номера сектора, входы второго элемента ИЛИ соединены с выходами.третьей и четвертой схем сравнения, выход второго элемента ИЛИ соединен со. вторым управляющим входом счетчика номера сектора, разрядный выход буферного iрегистра соединен с четвертым входом первого коммутатора, разрядный выход первого регистра адреса соединен с пятым входом первого коммутатора и со вторым входом третьей схемы сравнения , информационный вход второго регистра адреса соединен с первым входом второй схемы сравнения, с пер вым информационным входом первого регистра адреса, с информационным входом буферного регистра и со вторы разрядным выходом счетчика считывания, первы11 информационный вход третьего буферного регистра индекса является индексным, входом устройства второй информационный вход третьего буферного регистра индекса соединен с выходом сумматора индекса перехода разрядный выход третьего буферного регистра индекса соединен с информационным входом четвертого регистра индекса команды, с третьим входом второго коммутатора, с индексным вхо дом блока адресной памяти и со вторы информационным входом первого регист ра адреса, первый информационный вхо буферного регистра адреса соединен с разрядным выходом второго регистра адреса, второй информационный вход буферного регистра адреса соединен с разрядным выходом первого регистра индекса команды, информационный вход третьего регистра адреса соединен с разрядным выходом буферного регистра адреса, разрядный выход третьего регистра адреса соединен со вторыми входами второй и четвертой схем срав нения. На фиг.1 представлена схема предлагаемого устройства; на фиг.2 структурная схема узла распаковки командных слов; на фиг.З -/структурная схема узла управления первичной коммутацией; на фиг.4 - схема узла выработки значимости; на фиг.5 - схе ма узла управления обнулением. В устройство (фиг.1) входят первая схема 1 сравнения, второй коммутатор 2, второй регистр 3 индекса команды, третий регистр 4 индекса команды, четвертый регистр 5 индекса команды, первый буферный регистр 6 индекса, второй буферный регистр 7 индекса, третий буферный регистр 8 индекса, дешифратор 9 команды, вторая схема 10 сравнения, сумматор 11 индекса перехода, дешифратор12 длины команды, узел 13 распаковки командных слов, сумматор И индекса команды, первый регистр 15 команд, второй . регистр 16 команд, третий регистр 1/ команд, четвертый регистр 18 команд, блок 19 триггеров значимости команд, первый элемент ИЛИ 20, первый регистр 21 индекса команды, третий регистр 22 адреса, буферный регистр 23 адреса, второй регистр 2k адреса, блок 25 буферной памяти команд, блок 2б памяти битов значимости, блок 27 па)чяти битов ожидания, первый коммутатор 28, счетчик 29 считывания, регистр 30адреса назначения, буферный регистр 31, первый регистр 32 адреса, регистр 33 очередного сектора, третья схема 3 сравнения, четвёртая схема 35 сравнения, второй элемент ИЛИ 36, счетчик 37 номера сектора, блок 38 адресной памяти, первый управляющий выход 39, второй управляющий выход 40,. индексный вход 1, команднь|й выход 42,. индикаторный выход 43, индексный выход 44, информационный вход 45, второй адресный вход 46 устройства, выход 47 адреса назначения, первый адресный вход 48 устройства. Структурная схема узла распаковки командных слов (фиг.2} содержит узел 49 управления первичной коммутацией, коммутатор 50, узел 51 выработки значимости, узел 52 управления обнулением командных слов. Структурная схема узла управления первичной коммутацией (фиг.З) содержит элемент ИЛИ 53, элемент НЕ 54, элемент И 55, элемент ИЛИ 56, элемент НЕ 57. Схема узла выработки значимости (фиг.4) содержит элемент ИЛИ 58, группу элементов И 59, два.дешифратора 60 и 61, элемент И б2, элементы НЕ 63 и 64, элементы ИЛИ б5 и 66, группу элементов И 67, группу элементов И 68, элемент И б9, триггер 70, элемент ИЛИ 71, элементы И 72 и 73, э.пемент НЕ 74.

Схема узла управления обнулением (фиг.5) содержит группу элементов ИЛИ 75 группу элементов И 7б, элементы НЕ 77, 78 и 79, триггер 80.

Устройство работает следующим образом..

Программы пользователей и операционной системы представляют собой совокупность процедур, организованны в сегменты произвольной длины. Доступ к требуемой информации осуществляется через таблицы управляющих слов-дескрипторов. В общем случае, дескриптор содержит базу - адрес начала сегмента некоторой процедуры, и, количество - ве.личину, определяющую размер сегмента. Положение эле-; мента информации внутри сегмента определяется его смещением относительно базы, т.н. индексом.

Каждый командный сегмент соответствующей процедуры логически делится на секторы по 1б слов. Последние секторы могут быть неполными. Блок 25, входящий в состав устройства, являет-25 На ся памятью секторного типа, также логически делится на равные секторы по 16 слов и содержит 32 сектора.Любой секtup оперативной памяти может быть размещен в любом секторе блока 25. Соответствие между секторами по оперативной и буферной памяти устанавливается с помощью блока 38. Ячейки блока 38 СОСТ.ОЯТ из пар регистров база-индекс так, что каждая пара хранит базу сегмента, информация которого размещена в соответствующем секторе блока 25i и индекс - смещение сектора относительно базы.. Подкачка информации из оперативной памяти в буферн по производится блоками по четыре слова. Наличие требуемой информации в блоке 25 определяется индикаторами значимости регистров блока 38, блоком 26 и блоком 27. Значимость блока 38 означает, что соответствующий сектор блока 25 выделен под размещение в нем информации, сегментная база которой, а также индекс сектора этой информации хранятся в соответствующей ячейке блока 33. Блоки 26 и 27 являются прямоадресуемыми, количество их ячеек равно количеству секторов блока 25. Каждая ячейка 26 и 27 хранит по четыре бита, позиции которых соответствуют номерам блоков в секторе. Единица в некотором разряде блока 26 означает

занятость соответствующего блока 25. Единица в разряде блока 27 означает, что на соответствующий блок выдан запрос в оперативную память.

Регистры блока 38 и секторы блока 25 назначаются по счетчику 37.

На линейных участках программы команды вызываются из оперативной памяти блока 25 с некоторым опережением

по отношению к уровню дешифрации команд. При этом база командного сегмента через адресный вход 48 устройства, а индекс требуемой информации через индексный вход 1 устройства и

буферный регистр 8 поступают на базовый и индексный входы блока 38, где сравниваются одновременно со всеми парами регистров база-индекс. Состояние индикаторного выхода блока 38

указывает произошло сравнение с -одной из пар база-индекс или нет. Если сравнения нет, то счетчик 37, ко.торый хранит номер сектора, подлежащий замещению, передает его на регистр 30. другой вход регистра 30 поступают разряды, означающие номер блока в секторе, с выхода блока 38. Составленный таким образом адрес поступает на выход 7 адреса назначения устройства и вместе с исполнительным адресом участвует в формировании запроса к оперативной памяти. В дальнейшем адрес назначения будет сопровождать информацию, вызванную из оперативной памяти, в качестве адреса записи в блок 25. После выдачи запроса в оперативную память по адресу, который хранится на регистре 30, обнуляются ячейки блоков 26 и 27, кроме разряда. соответствующего вызываемому блоку, который устанавливается в единицу. Далее состояние на базовом и индексном входах блока 38 записывается в соответствующую пару регистров база-индекс по выходу счетчика 37, после чего счетчик 37 изменяет свое значение на единицу. Если же произошло сравнение с одной из пар база-индекс, то код с выхода блока 38 поступает на регистр 30. Содержимое этого регистра является адресом, по которому считываются из блоков 26 и 27 соответствующие биты значимости и ожидания, которые поступают на I;ервый элемент ИЛИ 20. Наличие битов значимости или ожидания, на что указывает значение индикаторного выхода 3, вызывает прерывание запроса в оперативную память. Отсут ствие битов значимости и ожидания приводит к считыванию информации из оперативной памяти, при этом в качестве .адреса назначения используетс содержимое регистра 30, в соответствующие биты блоков 26 и 27 записываются нуль и единица соответственно. Создание необходимого запаса команд для дешифрации исключает разрывы в потоке команд, связанные с ожиданием информации на линейных участках программы. Четыре слова блока, вызванного из оперативной памяти, поступают через информационный вход 45 в последовательно друг за другом, причем каждое слово сопровождается адресом назначения, поступающим через адресный вход 46, Адресный вход 46 соединен также с адресными входами блоков 26 и 27, вследствие чего вместе с за писью последнего слова блока в блок 25 в соответствующий бит блока 26 за писывается единица, а в бит блока 27 нуль, . Считывание из блока 25 осуществля ется по управляющему счетчику 29, Один из выходов счетчика 29 через коммутатор 28 подключен ко входу адреса считывания из блока 25, а другой - ко входам считывания блоков 2б и 27. После очередного считывания слова из блока 25 значения счетчика 29 увеличивается на единицу. Когда все слова некоторого сектора блока 25 считаны на дешифрацию, часть счетчика 29, означающая номер сектора, обновляется с регистра 33 через коммутатор. Код на регистр 33 поступает с выхода счетчика 37 или с выхода блока 38 при предварительном считывании нулевого блока сектора. Таким образом, всегда заранее известен сектор, в котором размещается продолжение программы. Слова, считанные из блока 25 по.ступают поочередно на регистры 15, 16 или 17, 18, Обе пары регистров команд 15, 16 и 17, 1В равнозначны, выбор пары для приема командных слов меняется при выполнении ветвлений, Одновременно со считыванием командного слова из блока 25 из блока 26 считывается соответствующий бит и блок 19 триггеров устанавливается в положение, означающее занятость со ответствующих регистров 15-18, выход которых подключены к узлу 13. Длина слова в блоке 25, регистрах 15-18 , 1810 составляет восемь байтов. Команды представляют собой плотно упакованный байтовый массив, длина команд переменна и кратна байту. Узел 13 выделяет пять байтов из дешифрируемой пары регистров 15-18 так, что код (операции выделенной команды оказывагется прижатым влево. Номер левого (байта относительно базы командного сегмента определен регистром 21, Регистр 21 управляет распаковкой регистров 15-18 и формирует на командном выходе 42 поток команд с.плотностью одна команда за такт на линейных участках программы. Дешифратор 12 после анализа кода операции вырабатывает величину приращения, которую необходимо просуммировать на сумматоре 14 с регистром 21, чтобы перейти к распаковке следующей команды. После полной дешифрации одного из регистров 15, 1б или 17, 18 узел 13 по обнуляющему выходу изменяет состояние блока 19 триггеров что приводит к считыванию очередного командного слова из блока 25 на один из освободившихся регистров 15-18. Команды ветвления, в выполнении которых участвует предлагаемое устройство, можно разделить на три типа: 1)команды типа БП - безусловный переход, 2)команды типа УП - условный переход, 3)команды типа КЦ - конец цикла. Формат команд ветвления включает код операции и дельту перехода - величину, определяющую на какое количество команд (в байтах) от дешифрируемой команды ветвления необходимо перейти программе. Левый бит дельты перехода знаковый и указывает направление ветвлени1Я (вперед или назад по программе). По командам БП происходит безусловная передача управления, команды УП являются типичными кдмандш и переход по условию, команды КЦ используют так называемое индексное слово. Индексное слово содержит три значения: текущий индекс, шаг приращения и предел. Команды КЦ проверяют, не превосходит ли текущий индекс Предела и, если ответ удовлетворит тельный, модифицируют текущий индекс на шаг приращения и передают управление команде по адресу перехо-. да, заданному в команде КЦ. Если те-. кущйй индекс достиг предела, управление передается очередной команде. Команды КЦ удобно применять для организации циклов типа ДЛЯ А ШАГ В ДО С ЦИКЛ Д, команды УП для организа цми условных операторов и циклов типа ДЛЯ А ПОКА В ЦИКЛ Д. При появлении на выходе узла 13 команды ветвления на сумматоре 11 происходит формирование индекса перехода и прием его на буферный регистр 8. Выход буферного регистра 8 подключен к индексному входу блока 38 и вместе с базой текущей процедур поступающей на адресный вход 8, фор ммрует адрес обращения к буферной памяти. Далее происходит анализ на присутствие .требуемой информации в блок 25 и считывание ее, если резуль тат анализа положительный, на соответствующий регистр , назначенный под ветвление. При командах типа БП или КЦ происходит смена пары регистров 15 1б или 17, 18 не только по подкачке информации из блока 25, но и по дешифрации. При команде УП смена пары регистров 15, 16 или 17, 18 происходит лишь по подкачке. Старое значение счетчика 29 хранится на буферном регистре 31 во время подкач чи. двух слов команд по новой ветви. Это старое знамение указателя считывания потребуется для продолжения подкачки командных слов в направлени на провал до выяснения условия перехода, для чего адрес из счетчика 29 поступает на буферный регистр 31, а адрес с буферного регистра 31 поступает через коммутатор 28, счетчик 29 и таким образом, до выяснения услови ветвления непрерывно осуществляется условная дешифрация команд в направлении на пров.л. Если условие перехо да выполнилось, происходит отмена ус ловно расшифрованных команр, смена пары регистров 15, 16 или 17, 18 по дешифрации, и адрес с буферного регистра 31 вновь поступает через коммутатор 28 на счетчик 29« Таким образом, устройство начинает дешифраци команд в направлении на переход. В обычном режиме появление команды ветвления на командном выходе 2 приводит к разрыву в потоке де1ииф рируемых команд, минимальное время которого определяется временем обращения через блок 38 к §локу 25. Выполнение циклических участков программ характеризуется многократ-. нымповторением набора команд, образующих тело цикла. Команда, которая замыкает цикл, является обычно командой ветвления, анализирующей условие конца цикла. Такая команда (КЦ или УП) называется командой, вызвавшей цикл . Когда дешифрируется команда ветвления типа КЦ или УП с отрицательной дельтой перехода, делается предположение, что организуется цикл. При этом до выяснения условия перехода на буферном регистре 8 запоминается индекс перехода, на буферном регистр 6 - индекс самой команды ветвления, на буферном регистре 7 индекс команды, следующей за командой ветвления. Кроме того, на буферной регистре 23 запоминается адрес слова по блоку 25, содержащего команду ветвления. Младшие разряды, означающие номер слова в секторе, поступают с регистра 21, а старение, означающие номер сектора, выхода регистра 24, содержимое которого обновляется со счетчика 29 при переходе дешифрации на новый сектор. Если при анализе условия ветвления выясняется, что необходимо выполнить переход, происходит перепись информации с буферных регистров 6,7, 8 и 23 на регистры-3,,5 и 22 соответствен(о. Кроме того, после установки адреса ветвления на счетчик 29 происходит передача на регистр 32 пяти разрядов, означающих номер сектора, с счетчика 29 и разрядов, означающих номер слова в секторе, с регистра 8. При этом устройство переходит в режим работы Цикл, который включает в работу схемы 1, 10, 3 и 35 сравнения. В режиме Цикл происходят повторное выполнение команд, начиная с первой команды цикла, до команды, вызвавшей цикл. При считывании из блока 25 слова, которое содержит команду, вызвавшую цикл, срабатывает схема 10 сравнения, что характеризуется появлением сигнала на втором управляющем выходе 40 и вызнвает следующие действия. Содержимое регистра 32 передается на счетчик 29 через коммутатор 28, Одновременно с изменением значения триггера 19 при считывании последнего слова цикла выход схемы 10 сравнения вызывает изменение в дешифраторе 9, т.е. при йбшифрации соответствующего слова будет известно, что это слово содержит команду, вызвавшую цикл. Напраьление подкачки командных слов из 6rio ка 25 изменяется, первые команды цик ла поступят на новую пару регистров 15, 16 или 17 .18 на фоне дешифрации команд из старой пары. Таким образом к моменту дешифрации команды, вызвав шей цикл, первые команды цикла будут считаны из блока 25 и готовы для их дешифрации. Момент дешифрации команды, вызвав шей цикл, устанавливается первой схе мой 1 сравнения, что характеризуется {выработкой управляющего сигнала на первом управляющем выходе 39 и вызывает следующие действия. Выход регис ра 5 через второй коммутатор 2 посту пает на регистр 21. Направление дешифрации команд изменяется, узел 13 переключается на новую пару регистров 15, 16, или 17, 18, где уже хранятся первые команды цикла. Таким сб разом, после дешифрации команды вет-вления, вызвавшей цикл, на командный (выход 2 без перерыва поступает первая команда цикла. До выяснения усло вия перехода производится условная дешифрация первых команд цикла. Если выясняется, что был необходим перехо на начало цикла, условные команды пе реводятся в обычные. Если в результате анализа условия перехода оказалось, что необходимо выйти : из цикла, условно расшифрованные команды отменяются, режим Цикл снимается, выход регистра 4 через коммутатор 2 поступает на регистр 21 и на индексный выход Ц для смены программного счетчика команд,. По счетчику команд начнется подкачка командных слов из блока 25 (установка счетчика 29 произойдет через индексный вход 41,буферный регистр 8, блок 38 и коммутатор 28) начиная со слова, которое содержит продолжение программы после цикла. В режиме Цикл секторы, содеркащие команды начала и конца циклической программы, защищены от замещения Выбор сектора, который необходимо выделить под новую информацию, происходит по счетчику 37. Момент сравнения счетчика 37 с регис;трами 32 или 22 фиксируется схемами 34 и 35 сравнения соответственно, выходы ко торых через второй элемент ИЛИ 36 поступают на счетчик 37 и вызывают увеличение его на единицу, Вследствие этого начало и конец цикла всегда находятся в блоке 25, что обеспечивает быстрый доступ к требуемой командной информации. Формула изобретения Устройство для формирования команд с аппаратной организацией циклических программ, содержащее блок адресной памяти, адресный вход которого является первым адресным входом устройства, счетчик номера сектора, первый управляю вход которого соединен с управляющим выходом блока адресной памяти, первый разрядный выход - с управляющим входом блока адресной памяти, блок буферной памяти команд, блок памяти битов значимости, блок памяти битое ожидания, адресные входы которых соединены со вторым адресным входом устройства, а информационный вход блока буферной памяти команд является информационным входом устройства, первый коммутатор, счетчик считывания первый, второй разрядные выходы которого соединены с первым входом первого коммутатора и с первыми входами считывания блоков памяти битов значимости и ожидания соответственно, регистр очередного сектора, регистр адреса назначения, первые инфоомационные входы которых соединены со ВТОРЫМ оазоядным выходом и счетчик номеоа сектооа вторые информационные входы регистра очередного сектора и регистра адреса назначения и ВТОРОЙ вход первого,коммутатора соединены с информационным выходом блока адресной памяти, разрядный выход регистра очередного сектора соединен с третьим входом первого коммутатора, выход которого соединен со входов считывания блока буферной памяти комвнд и с информационным входом счетчика считывания разрядный выход регистра адреса назначения соединен со вторыми входами считывания блоков памяти и битов значимости и ожидания и с выходом адреса назначения устройства, первый, второй, третий и четвертый регистры команд, информационные входы которых соединены с первым выходом блока буферной памяти команд,, узел распаковки кома.ндных слов., каждый информационный вход которого соединен с разрядным выходом соответствующего регистра команд, блок-триггеров зиачимости команд, нулевой вход которого соединен с блокировочным выходом блока буферной памяти команд, вход сброса блока триггеров значимости команд соединен с обнуляющим выходом узла распаковки командных слов, а выход соединен со входом значимости узла распаковки командных слов, первый эле« мент ИЛИ, выход которого является, индикаторным выходом устройства,пер вый вход элемента ИЛИ соединен с вы ходом блока; памяти битов ожидания, второй вход первого элемента ИЛИ и единичный вход блока триггеров значимости команд соединены с выходом блока памяти битов значимости, дешифратор длины команды, первый регистр индекса команды, сумматор индекса команды, первый вход которого соединен с выходом дешифратора длины команды, а выход соединен с первым информационным входом первого регистра, индекса команды, сумматор индекса перехода, первый вход, крто« рогр, вход дешифратора длины команды и.командный выход устройства сое динены с выходом узла распаковки ко мандных слов, первую схему сравнени выход которой является первым управ ляющим выходом устройства, второй регистр индекса команды, разрядный выход которого соединен с первым входом первой схемы сравнения, второй коммутатор, ВЫХО.Д которого явля ется индексным выходом устройства И соединен со вторым информационным входом регистра индекса команды, разрядный выход которого соединен с вторыми входами сумматора индекса команды, сумматора индекса перехода ;первой схемы сравнения и с управляю щим входом узла распаковки командны слов, третий и четвертый регистры индекса команды, разрядные выходы которых соединены с первым и вторым входами второго коммутатора соответ ственно, отличающееся те что, с целью повышения быстродействия , оно содержит первый буферный регистр индекса, второй буферный регистр индекса, первый дешифратор команды, вторую, третью и четвертую схемы сравнения, второй элемент ИЛИ .первый регистр адреса, первый буфер ный регистр, второй регистр адреса, третий буферный регистр индекса, бу 816 фёркый регистр адреса, третий регистр адреса, причем информационные входы первого буферного регистра индекса и второго буферного регистра индекса соединены с разрядным выходом первого регистра индекса команды, разрядные выходы этих регистров соединены с информационными входами второго и третьего регистров индекса команды соответственно, первый вхсд дешифратора команды соединен с выходом обнуления узла распаковки командных слов, выход этого дешифратора соединен с управляющим входом первой схемы сравнения, второй вход дешифратора команды соединен с выходом второй схемы сравнения и со вторым управляющим выходом устройства, первые входы третьей и четвертой схем сравнения соединены со вторым разрядным выходом счетчика номера сектора, входы второго элемента ИЛИ соединены с выходами третьей и четвертой схем сравнения, выход второго элементаили соединен со вторым управляющим входом счетчика номера сектора, разрядный выход буферного регистра соединен с четвертым входом первого коммутатора, разрядный выход первого регистра адреса соединен с пятым входом первого коммутатора и со вторым входом третьей схемы сравнения, информационный вход второго регистра адреса соединен с первым входом второй схемы сравнения, с первым информационным входом первого регистра адреса, с информационным входом.буферного регистра и со вторым разрядным выходом счетчика считывания, первый информационный вход третьего буферного регистра индекса является индексным входом устройства, второй информационный вход третьего буферного регистра индекса соединен .с выходом сумматора индекса перехода, разрядный выход третьего буферного регистра индекса соединен с информационным входом четвертого регистра индекса команды, с тpefьим входом второго коммутатора , с индексным оходом блока адресной памяти и со вторым информационным входом первого регистра адреса, первый информационный вход буферного регистра адреса соединен с разрядным выходом второго регистра адреса, второй информационный вход буферного регистра адреса соединен с разрядным выходом первого регистра индекса команды, информационный

17 .SkZQiB18

вход третьего регистра адреса соеди-Источники информации,

нен с разрядным выходом буферногопринятые во внимание при экспертизе

регистра адреса, разрядный выход1. Патент США И 3 90005,

третьего регистра адреса соединенкл. ,172.5, опублик.1970.

со вторыми входами второй и четвер-s 2. Патент США If ЗвЮвбЬ

той схем сравнения.кл. 3Ю,172.5, 197 (прототип).

-К

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования команд | 1978 |

|

SU734686A1 |

| Устройство для адресации буферной памяти | 1978 |

|

SU717771A1 |

| Устройство управления буферной памятью | 1978 |

|

SU737952A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство для выборки команд | 1978 |

|

SU726533A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для формирования адресов команд и данных | 1985 |

|

SU1312573A1 |

| Устройство для управления буфер-НОй пАМяТью | 1979 |

|

SU840903A1 |

| Устройство для распаковки команд | 1984 |

|

SU1196865A1 |

W W 7ff l/fiWm

у w I/ г 7 I / W

A

ш

r

1Л У

f

/k

0fff.J

Авторы

Даты

1982-07-07—Публикация

1979-12-25—Подача