Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах управления технологическим оборудованием.

Цель изобретения - расширение области применения за счет увеличения области памяти микропрограмм.

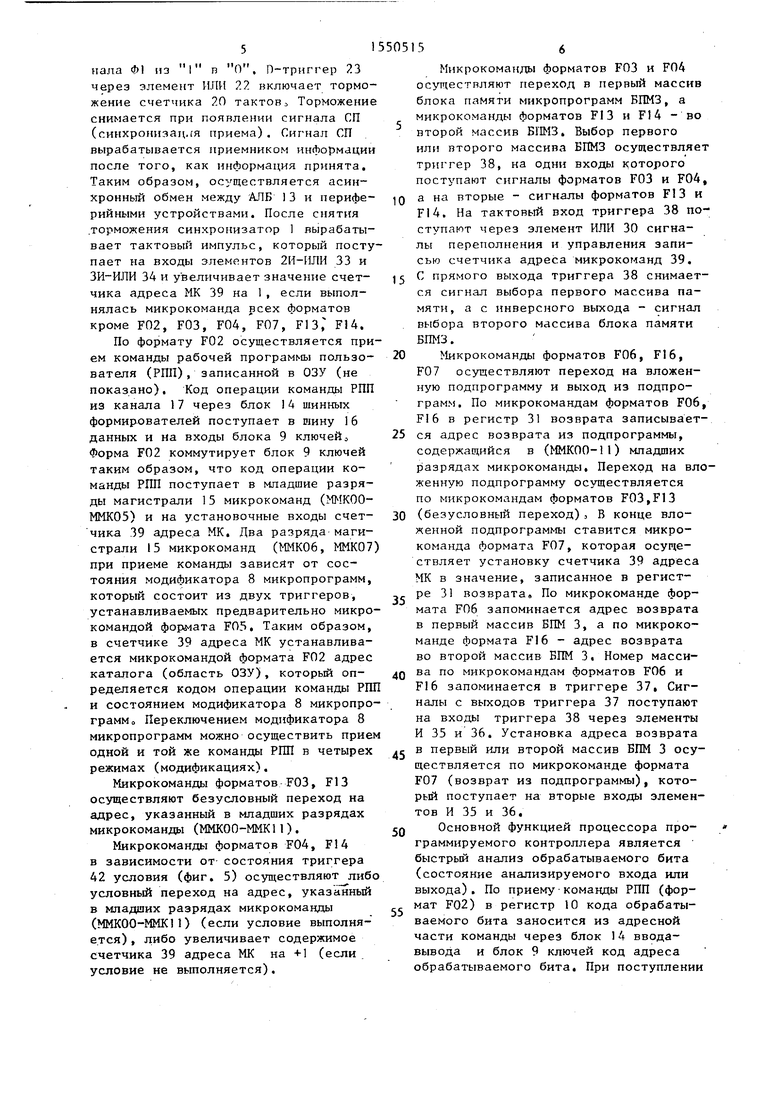

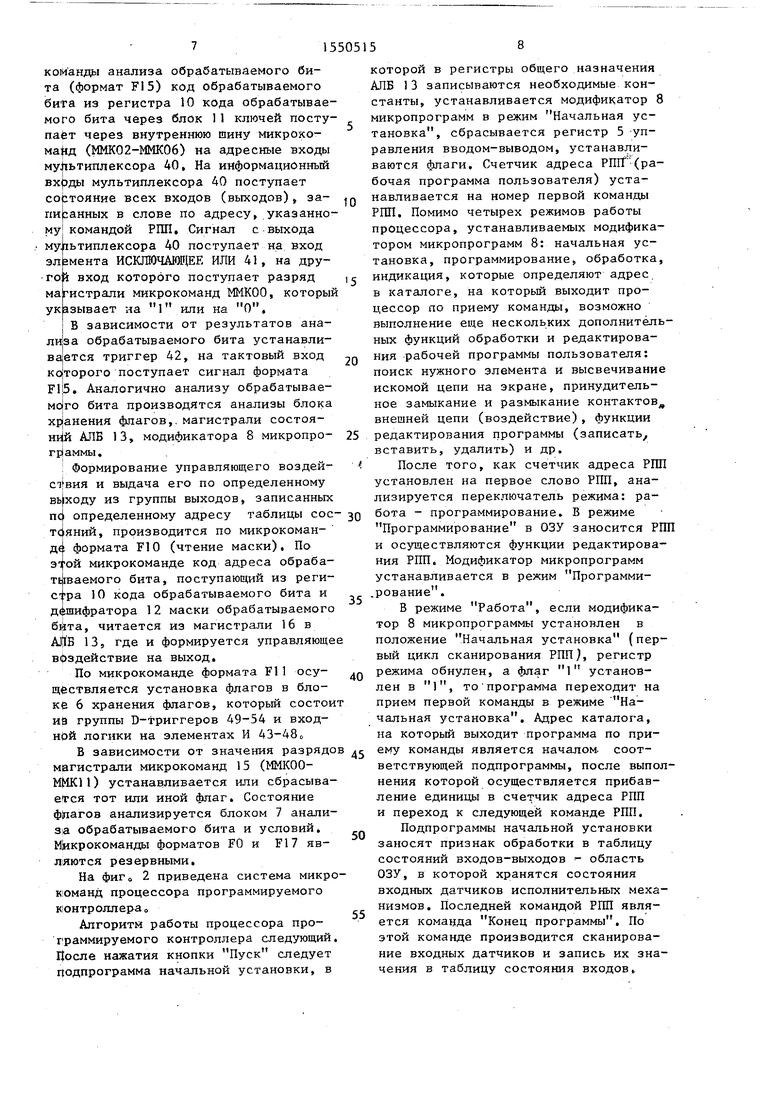

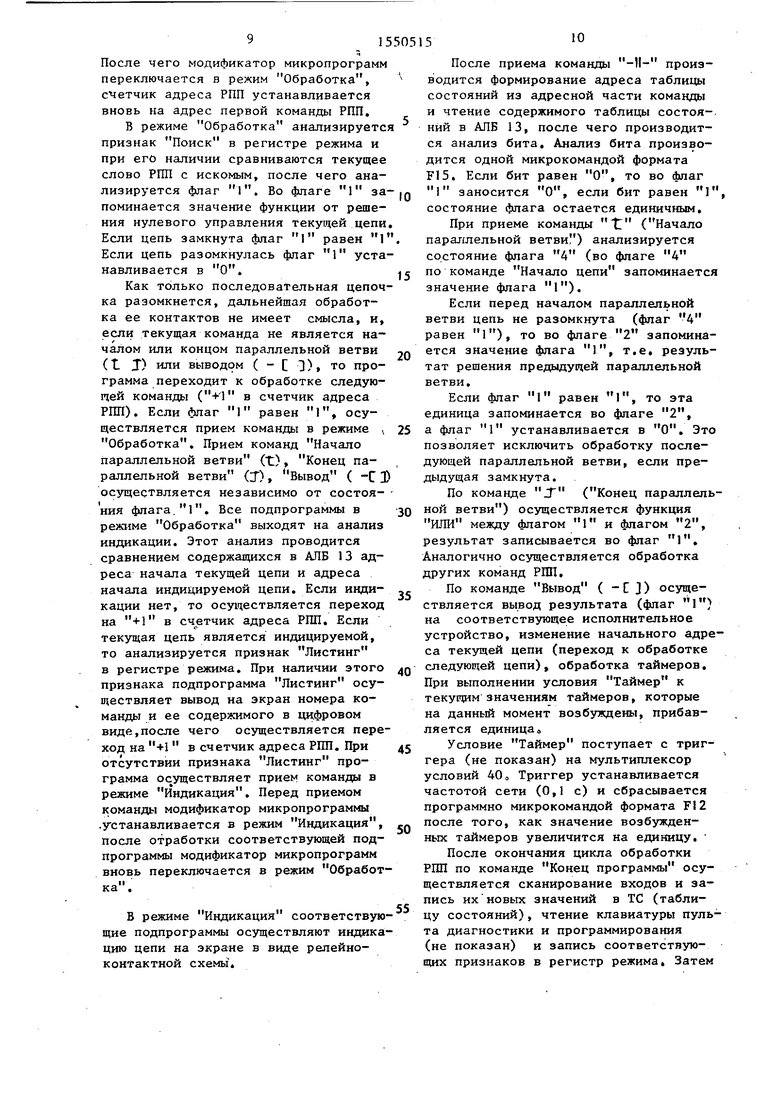

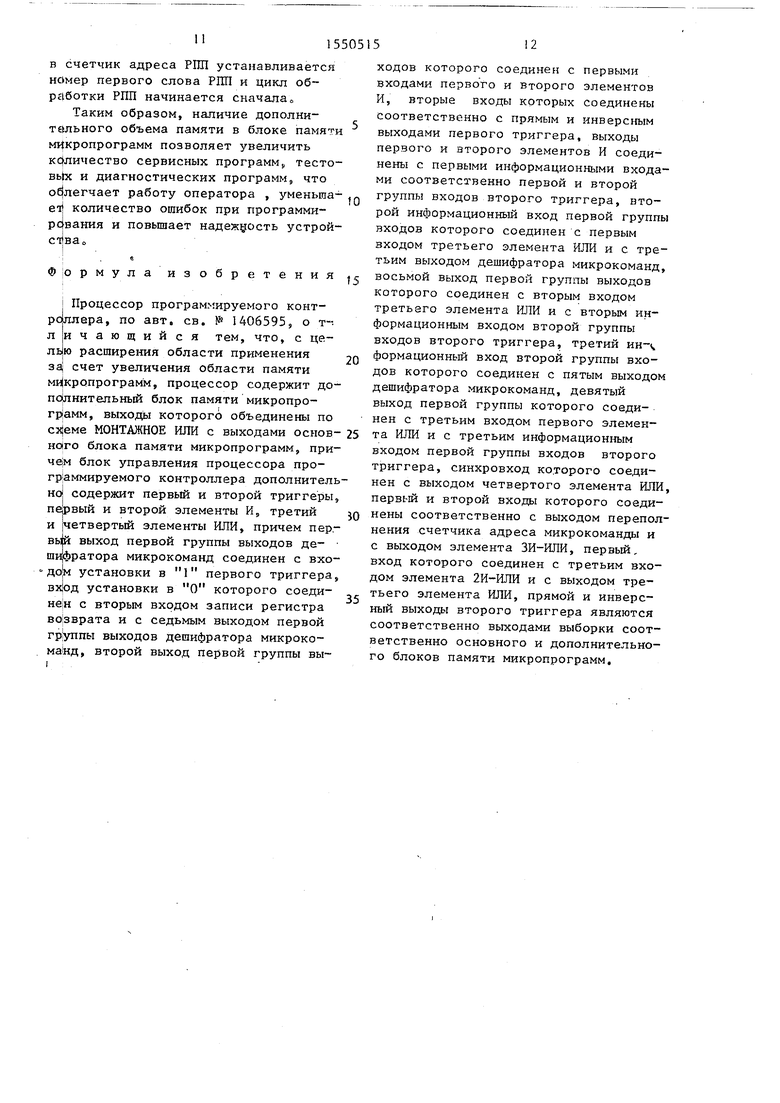

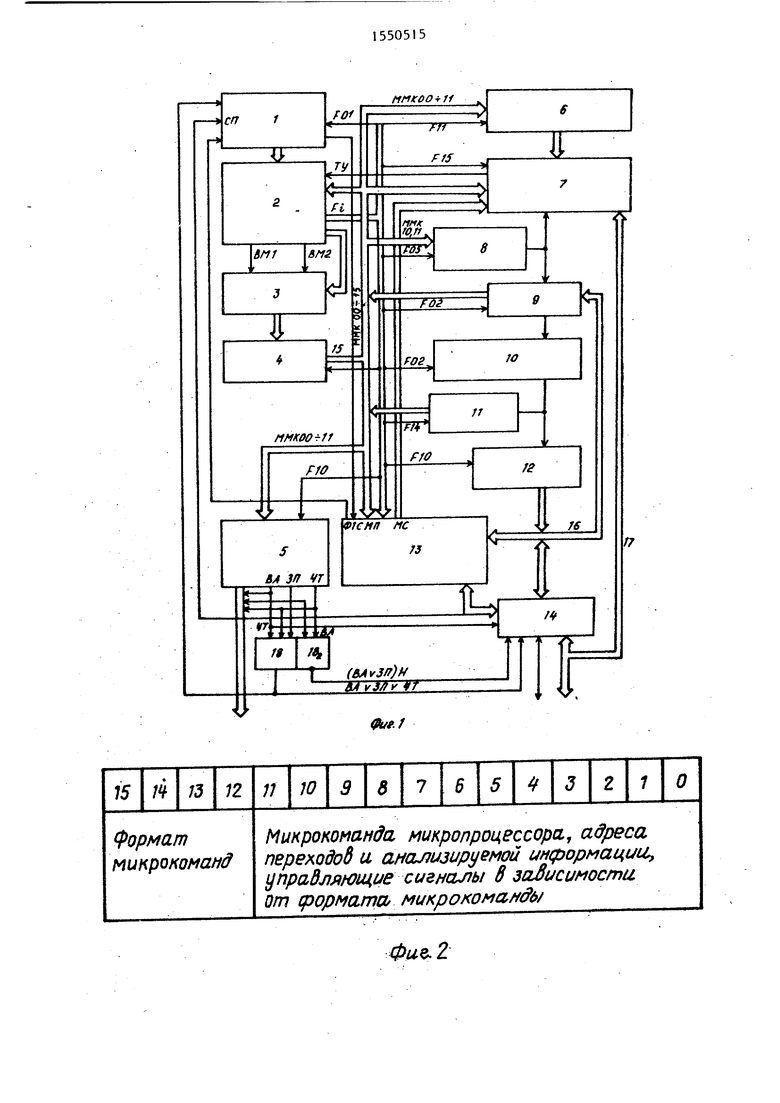

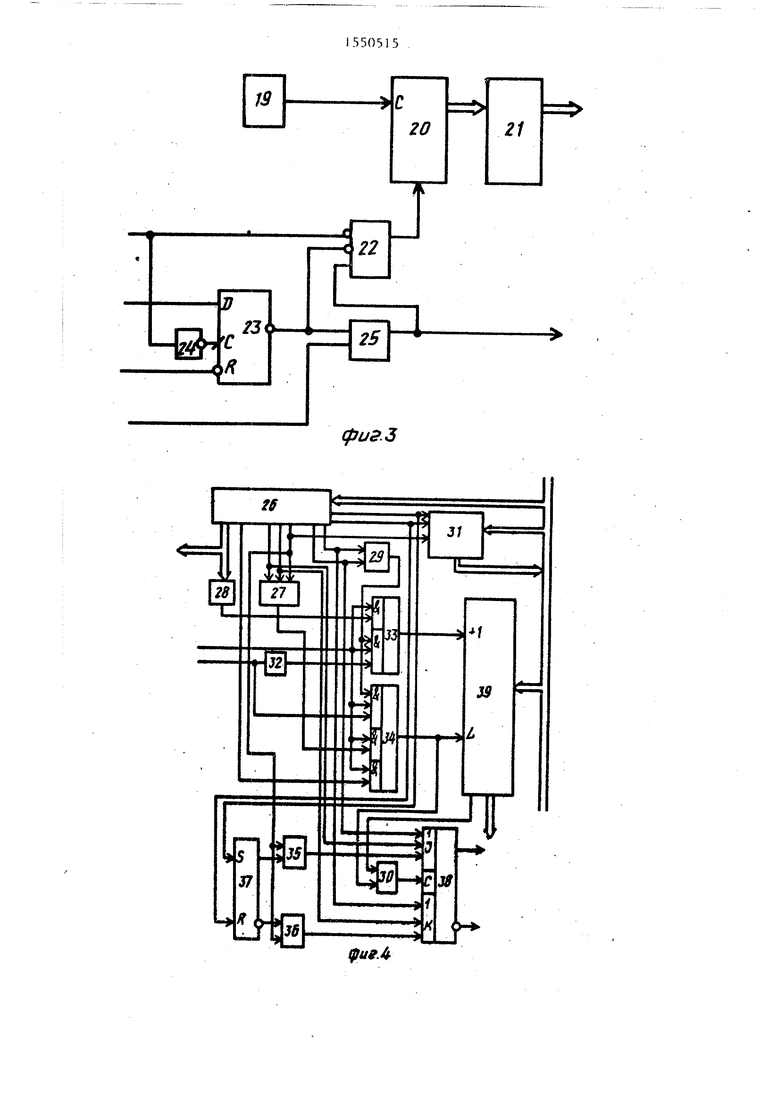

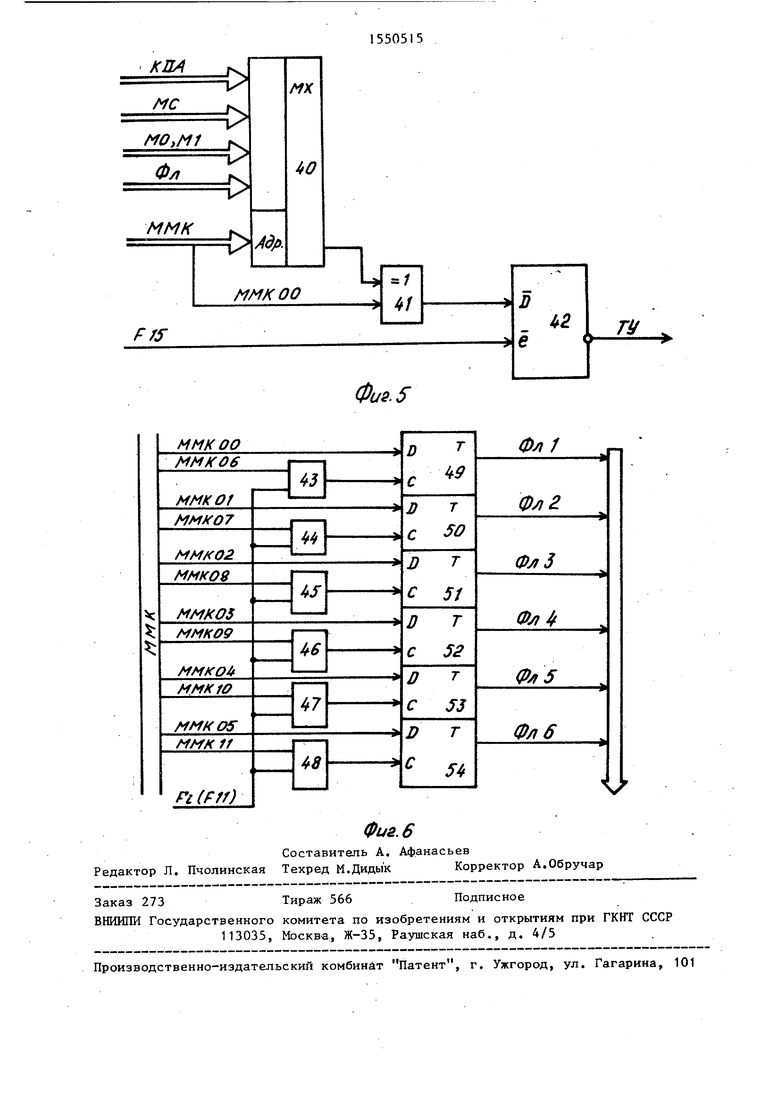

На фиг. 1 приведена структурная схема процессора программируемого контроллера; на фиг. 2 - система микрокоманд процессора; на фиг.З - функциональная схема синхронизатора; на фиг. 4 - функциональная схема блока управления; на фиг. 5 - функциональная схема блока анализа обрабатываемого бита и условий; на фиг. 6 - функциональная схема блока хранения флагов.

Процессор программируемого контроллера содержит синхронизатор 1, . блок 2 управления, блоки 3 памяти микропрограмм (БПМ}, регистр 4 микрокоманд, регистр 5 управления вводом- выводом, блок 6 хранения флагов, блок 7 анализа обрабатываемого бита и условий, модификатор 8 микропрограмм, первый блок 9 ключей с трех- стабильным выходом, регистр 10 кода обрабатываемого бита, второй блок 11 ключей с трехстабильным выходом, дешифратор 12 маски обарабатываемого бита, арифметико-логический блок (АЛБ) 13, блок 14 ввода-вывода, внутренняя шина 15 микрокоманд ,внутренняя шина 16 данных, канал 17 данных, первый 18, и второй 18 элементы ИЛИ.

ел ел

о ел

ел

го

Синхронизатор содержит генератор 19, счетчик 20 тактов, дешифратор 21 тактов, второй элемент ИЛИ 22, триггер 23, первый элемент НЕ 24, пер- йый элемент И 25.

Блок управления процессором и адресом микрокоманд содержит дешифра- ратор 26 формата микрокоманд, элементы ИЛИ 27-30, регистр 31 возврата, Йторой элемент НЕ 32, элемент 2И-ИЛИ $3 и ЗИ-ИЛИ 34, элементы И 35 и 36, Триггеры 37 и 38, счетчик 39 адре- йа МК.

Блок анализа обрабатываемого бита И условий содержит мультиплексор 40, Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 41, триггер 42.

Блок хранения флагов содержит элементы И 43-48 и триггеры 49-54.

Процессор работает следующим образом.

Генератор 19 синхронизатора 1 (|фиг.З} генерирует последовательность импульсов, которая преобразуется Счетчиком 20 и дешифратором 21 тактов и систему тактовых импульсов, синхронизирующих работу процессора. Тактовые импульсы поступают на входы Элементов И-ИЛИ 33 и 34 блока 2 управления,

С выходов счетчика 39 адреса МК Сигналы поступают на адресные входы fylIM 3 и определяют адрес считываемой микрокоманды. С выходов БПМ 3 информация поступает на входы регистра 4 микрокоманд, а с его выходов о внутреннюю шину 15 микрокоманд.

Старшие разряды (ММК12-ММК15) ма- 1Систрали 15 микрокоманд определяют формат микрокоманды (фиг,2) и посту- йают на дешифратор 26 формата микрокоманд.

С выходов дешифратора формата микрокоманд 26 управляющие сигналы (Fi) поступают на входы различных блоков процессора, определяя выполнение микрокоманды данного формата.

В формате 01 выполняются команды АЛБ 13. Код выполняемой микрокоманд Определяют младшие разряды магистра- йи микрокоманд 15 (ММКОО-ММК11). АЛБ 13, сигнализируя о своей готов- Ности к приему микроманды, выставляе На выходе исполнения микрокоманд высокий уровень сигнала Ф1, который по ступает на инверсный вход элемента ИЛИ 22 (фиг.З ), В это же время на вход элемента И 25 поступает сигнал

,

0

5

0

5

0

5

F01 с дешифратора 26 формата, на второй вход элемента И 25 поступает сигнал с инверсного выхода D-тригге- ра 23, который в начальный момент установлен в нулевое состояние сигналом Сброс (не показан). С выхода элемента И 25 сигнал СМП (такт АЛБ) поступает на тактовый вход АЛБ 13, разрешая выполнение микрокоманды, и на второй вход элемента ИЛИ 22, с выхода которого поступает сигнал Тормоз, блокирующий работу счетчика 20 тактов на время приема и исполнения микрокоманды АЛБ 13, который устанавливает низкий уровень сигнала Ф1. С появлением сигнала Тормоз дешифратор 21 тактов формирует сигнал, блокирующий дешифратор 26 формата, который снимает сигнал формата F01 и, соответственно, СМП. По окончании выполнения АЛБ 13 устанавливает высокий уровень сигнала и счетчик тактов # 20 разблокируется. Выполнению АЛБ 13 микрокоманд с обменом - прием информации из канала и выдача информации в канал данных 17, должна предшествовать микрокоманда, устанавливающая соответствующие сигналы с регистра 5 управления вводом-выводом (формат F10)0 Регистр 5 управления вводом- выводом выполнен на микросхеме К589ИР12.

На установочные входы регистра 5 управления вводом-выводом подаются младшие разряды магистрали микрокоманд 15 (ММКОО-ММК07).

На тактовый вход регистра 5 управления вводом-выводом поступает от дешифратора 26 формата сигнал соответствующего формата (F10). С выходов регистра 5 управления вводом-выводом снимаются сигналы, соответствующие адресуемому периферийному устройству: опертивное запоминающее устройство, блоки ввода-вывода, пульт диагностики и др. (не показаны) и сигналы управления выдаваемой или получаемой информацией ЗП (запись), ЧТ (чтение) , ВА (выдача адреса). Регистр 5 управления вводом-выводом сбрасывается микрокомандой формата F10 со всеми нулями в младших разрядах микрокоманды. Сигналы ВА, ЗП, ЧТ через элемент ИЛИ 18, поступают на вход D-триггера 23. Информация о выполнении микрокоманды с обменом (наличие одного из сигналов ВА, ЗП, ЧТ) заносится в D-триггер 23 по перепаду сиг51

нала Ф из I и О. П-триггер 23 через элемент ИЛИ 22 включает торможение счетчика 20 тактов3 Торможение снимается при появлении сигнала СП (синхроннзац,т приема). Сигнал СП вырабатывается приемником информации после того, как информация принята. Таким образом, осуществляется асинхронный обмен между АЛБ 13 и перифе- рийными устройствами. После снятия торможения синхронизатор вырабатывает тактовый импульс, который поступает на входы элементов 2И-ИЛИ 33 и ЗИ-ИЛИ 34 и увеличивает значение счет- чика адреса МК 39 на 1, если выполнялась микрокоманда всех форматов кроме F02, РОЗ, F04, F07, F13, F14.

По формату F02 осуществляется прием команды рабочей программы пользе- вателя (РПП), записанной в ОЗУ (не показано). Код операции команды РПП из канала 17 через блок 14 шинных формирователей поступает в шину 16 данных и на входы блока 9 ключейа Форма F02 коммутирует блок 9 ключей таким образом, что код операции команды РПП поступает в младшие разряды магистрали 15 микрокоманд (ММКОО- ММК05) и на установочные входы счет- чика 39 адреса МК. Два разряда магистрали 15 микрокоманд (ММК06, ММК07) при приеме команды зависит от состояния модификатора 8 микропрограмм, который состоит из двух триггеров, устанавливаемых предварительно микрокомандой формата F05. Таким образом, в счетчике 39 адреса МК устанавливается микрокомандой формата F02 адрес каталога (область ОЗУ), который оп- ределяется кодом операции команды РПП и состоянием модификатора 8 микропрограмм Переключением модификатора 8 микропрограмм можно осуществить прием одной и той же команды РПП в четырех режимах (модификациях).

Микрокоманды форматов F03, F13 осуществляют безусловный переход на адрес, указанный в младших разрядах микрокоманды (ММКОО-ММКП).

Микрокоманды форматов F04, F14 в зависимости от состояния триггера 42 условия (фиг. 5) осуществляют либо условный переход на адрес, указанный в младших разрядах микрокоманды (ММКОО-ММКИ) (если условие выполняется) , либо увеличивает содержимое счетчика 39 адреса МК на +1 (если условие не выполняется).

156

Микрокоманды форматов РОЗ и F04 осуществляют переход в первый массив блока памяти микропрограмм БПМЗ, а микрокоманды форматов F13 и F14 - во второй массив БПМЗ, Выбор первого или второго массива БПМЗ осуществляе триггер 38, на одни входы которого поступают сигналы форматов РОЗ и F04 а на вторые - сигналы форматов FI3 и F14. На тактовый вход триггера 38 поступают через элемент ИЛИ 30 сигналы переполнения и управления записью счетчика адреса микрокоманд 39. С прямого выхода триггера 38 снимается сигнал выбора первого массива памяти, а с инверсного выхода - сигнал выбора второго массива блока памяти БПМЗ.

Микрокоманды форматов F06, F16, F07 осуществляют переход на вложенную подпрограмму и выход из подпрограмм. По микрокомандам форматов F06 FI6 в регистр 31 возврата записывается адрес возврата из подпрограммы, содержащийся в (ММКОО-11) младших разрядах микрокоманды. Переход на вложенную подпрограмму осуществляется по микрокомандам форматов F03,F13 (безусловный переход), В конце вложенной подпрограммы ставится микрокоманда формата F07, которая осуществляет установку счетчика 39 адреса МК в значение, записанное в регистре 31 возврата. По микрокоманде формата F06 запоминается адрес возврата в первый массив БПМ 3, а по микрокоманде формата F16 - адрес возврата во второй массив БПМ 3. Номер массива по микрокомандам форматов F06 и F16 запоминается в триггере 37. Сигналы с выходов триггера 37 поступают на входы триггера 38 через элементы И 35 и 36. Установка адреса возврата в первый или второй массив БПМ 3 осуществляется по микрокоманде формата F07 (возврат из подпрограммы), который поступает на вторые входы элементов И 35 и 36.

Основной функцией процессора программируемого контроллера является быстрый анализ обрабатываемого бита (состояние анализируемого входа или выхода). По приему команды РПП (формат F02) в регистр 10 кода обрабатываемого бита заносится из адресной части команды через блок 14 ввода- вывода и блок 9 ключей код адреса обрабатываемого бита. При поступлении

команды анализа обрабатываемого бита (формат F15) код обрабатываемого би Га из регистра 10 кода обрабатываемого бита через блок 11 ключей поступает через внутреннюю шину микроко- майд (MMKQ2-MMK06) на адресные входы мультиплексора 40, На информационный вх(зды мультиплексора 40 поступает состояние всех входов (выходов), за- писанных в слове по адресу, указанному командой РПП, Сигнал с выхода мультиплексора 40 поступает на вход элгмента ИСКЛЮЧАЮЩЕЕ ИЛИ 41, на другой вход которого поступает разряд магистрали микрокоманд ММКОО, который указывает на 1 или на О,

В зависимости от результатов анализа обрабатываемого бита устанавли- триггер 42, на тактовый вход которого поступает сигнал формата FlB. Аналогично анализу обрабатываемого бита производятся анализы блока хранения флагов, магистрали состояний АЛБ 13, модификатора 8 микропрограммы.

Формирование управляющего воздействия и выдача его по определенному выходу из группы выходов, записанных п0 определенному адресу таблицы сос- тряний, производится по микрокоманде формата F10 (чтение маски). По этой микрокоманде код адреса обраба- ть|шаемого бита, поступающий из реги- сфра 10 кода обрабатываемого бита и дешифратора 12 маски обрабатываемого бита, читается из магистрали 16 в АЙВ 13, где и формируется управляюще воздействие на выход.

По микрокоманде формата F1 1 осуществляется установка флагов в бло- кЈ 6 хранения флагов, который состои ив группы D-триггеров 49-54 и входной логики на элементах И 43-480

В зависимости от значения разрядо магистрали микрокоманд 15 (ММКОО- ММК11) устанавливается или сбрасывается тот или иной флаг. Состояние ф|пагов анализируется блоком 7 анализа обрабатываемого бита и условий. Макрокоманды форматов FO и F17 являются резервными.

На фиг о 2 приведена система микрокоманд процессора программируемого контроллера0

Алгоритм работы процессора программируемого контроллера следующий. После нажатия кнопки Пуск следует Подпрограмма начальной установки, в

0

5

0

5

0

5

0

5

которой в регистры общего назначения АЛБ 13 записываются необходимые константы, устанавливается модификатор 8 микропрограмм в режим Начальная установка, сбрасывается регистр 5 управления вводом-выводом, устанавливаются флаги. Счетчик адреса РПГГ (рабочая программа пользователя) устанавливается на номер первой команды РПП, Помимо четырех режимов работы процессора, устанавливаемых модификатором микропрограмм 8: начальная установка, программирование, обработка, индикация, которые определяют адрес в каталоге, на который выходит процессор по приему команды, возможно выполнение еще нескольких дополнительных функций обработки и редактирования рабочей программы пользователя: поиск нужного элемента и высвечивание искомой цепи на экране, принудительное замыкание и размыкание контактов внешней цепи (воздействие), функции редактирования программы (записать, вставить, удалить) и др.

После того, как счетчик адреса РПП установлен на первое слово РПП, анализируется переключатель режима: работа - программирование. В режиме Программирование в ОЗУ заносится РПП и осуществляются функции редактирования РПП. Модификатор микропрограмм устанавливается в режим Программирование.

В режиме Работа, если модификатор 8 микропрограммы установлен в положение Начальная установка (первый цикл сканирования РПП, регистр режима обнулен, а флаг 1 установлен в 1, то программа переходит на прием первой команды в режиме Начальная установка. Адрес каталога, на который выходит программа по приему команды является началом соответствующей подпрограммы, после выполнения которой осуществляется прибавление единицы в счетчик адреса РПП и переход к следующей команде РПП.

Подпрограммы начальной установки заносят признак обработки в таблицу состояний входов-выходов - область ОЗУ, в которой хранятся состояния входных датчиков исполнительных механизмов . Последней командой РПП является команда Конец программы. По этой команде производится сканирование входных датчиков и запись их значения в таблицу состояния входовt

915

После чего модификатор микропрограмм переключается в режим Обработка, счетчик адреса РПП устанавливается вновь на адрес первой команды РПП.

В режиме Обработка анализируется признак Поиск в регистре режима и при его наличии сравниваются текущее слово РПП с искомым, после чего анализируется флаг 1. Во флаге 1 запоминается значение функции от решения нулевого управления текущей цепи. Если цепь замкнута флаг I равен 1 Если цепь разомкнулась флаг 1 устанавливается в О.

Как только последовательная цепочка разомкнется, дальнейшая обработка ее контактов не имеет смысла, и, если текущая команда не является началом или концом параллельной ветви (t J) или выводом ( - 1), то программа переходит к обработке следующей команды (+ 1 в счетчик адреса РПП). Если флаг 1 равен 1, осуществляется прием команды в режиме v Обработка. Прием команд Начало параллельной ветви (Т), Конец параллельной ветви СГ), Вывод ( С 3) осуществляется независимо от состоя- ния флага 1. Все подпрограммы в режиме Обработка выходят на анализ индикации. Этот анализ проводится сравнением содержащихся в АЛБ 13 адреса начала текущей цепи и адреса начала индицируемой цепи. Если инди- кации нет, то осуществляется переход на +1 в счетчик адреса РПП. Если текущая цепь является индицируемой, то анализируется признак Листинг в регистре режима. При наличии этого признака подпрограмма Листинг осуществляет вывод на экран номера команды и ее содержимого в цифровом виде,после чего осуществляется переход на +1 в счетчик адреса РПП. При отсутствии признака Листинг программа осуществляет прием команды в режиме Индикация. Перед приемом команды модификатор микропрограммы .устанавливается в режим Индикация, после отработки соответствующей подпрограммы модификатор микропрограмм вновь переключается в режим Обработка.

В режиме Индикация соответствующие подпрограммы осуществляют индикацию цепи на экране в виде релейно- контактной схемы .

15

10

5

д

п 5 0 5 0 5 Q

После приема команды -1I- производится формирование адреса таблицы состояний из адресной части команды и чтение содержимого таблицы состояний в АЛБ 13, после чего производится анализ бита. Анализ бита производится одной микрокомандой формата F15. Если бит равен О, то во флаг 1 заносится О, если бит равен 1, состояние флага остается единичным.

При приеме команды Ј (Начало параллельной ветви,) анализируется состояние флага А (во флаге 4 по команде Начало цепи запоминается значение флага 1).

Если перед началом параллельной ветви цепь не разомкнута (флаг 4 равен 1), то во флаге 2 запоминается значение флага 1, т.е. результат решения предыдущей параллельной ветви.

Если флаг 1 равен 1, то эта единица запоминается во флаге 2, а флаг 1 устанавливается в О. Это позволяет исключить обработку последующей параллельной ветви, если предыдущая замкнута.

По команде jj (Конец параллельной ветви) осуществляется функция ИЛИ между флагом 1 и флагом 2, результат записывается во флаг 1. Аналогично осуществляется обработка других команд РПП.

По команде Вывод ( - С J) осуществляется вывод результата (флаг 1) на соответствующее исполнительное устройство, изменение начального адреса текущей цепи (переход к обработке следующей цепи), обработка таймеров. При выполнении условия Таймер к текущим значениям таймеров, которые на данный момент возбуждены, прибавляется единица0

Условие Таймер поступает с триггера (не показан) на мультиплексор условий 40 о Триггер устанавливается частотой сети (0,1 с) и сбрасывается программно микрокомандой формата F12 после того, как значение возбужденных таймеров увеличится на единицу.

После окончания цикла обработки РПП по команде Конец программы осуществляется сканирование входов и запись их новых значений в ТС (таблицу состояний), чтение клавиатуры пульта диагностики и программирования (не показан) и запись соответствующих признаков в регистр режима. Затем

в счетчик адреса РПП устанавливается номер первого слова Р1ГП и цикл обработки РПП начинается сначала

Таким образом, наличие дополнительного объема памяти в блоке памяти микропрограмм позволяет увеличить количество сервисных программ,, тестовых и диагностических программ, что облегчает работу оператора , уменьшает количество ошибок при программирования и повышает надежность уСТрОЙ- СТВа

е

Формула изобретения

Процессор программируемого контроллера, по авт. св. № 1406595, о т- личающийся тем, что, с целью расширения области применения за, счет увеличения области памяти микропрограмм, процессор содержит дополнительный блок памяти микропрограмм, выходы которого объединены по сх)еме МОНТАЖНОЕ ИЛИ с выходами основ- наго блока памяти микропрограмм, причем блок управления процессора программируемого контроллера дополнительно) содержит первый и второй триггеры, первый и второй элементы И„ третий и четвертый элементы ИЛИ, причем первый выход первой группы выходов дешифратора микрокоманд соединен с вхо- -дом установки в 1 первого триггера, установки в О которого соединен с вторым входом записи регистра возврата и с седьмым выходом первой группы выходов дешифратора микрокоманд, второй выход первой группы вы

o

5

25 0

Ю

35

ходов которого соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с прямым и инверсным выходами первого триггера, выходы первого и второго элементов И соединены с первыми информационными входами соответственно первой и второй группы входов второго триггера, второй информационный вход первой группы входов которого соединен с первым входом третьего элемента ИЛИ и с третьим выходом дешифратора микрокоманд, восьмой выход первой группы выходов которого соединен с вторым входом третьего элемента ИЛИ и с вторым информационным входом второй группы входов второго триггера, третий формационный вход второй группы входов которого соединен с пятым выходом дешифратора микрокоманд, девятый выход первой группы которого соединен с третьим входом первого элемента ИЛИ и с третьим информационным входом первой группы входов второго триггера, синхровход которого соединен с выходом четвертого элемента ИЛИ, первый и второй входы которого соединены соответственно с выходом переполнения счетчика адреса микрокоманды и с выходом элемента ЗИ-ИЛИ, первый, вход которого соединен с третьим входом элемента 2И-ИЛИ и с выходом третьего элемента ИЛИ, прямой и инверсный выходы второго триггера являются соответственно выходами выборки соответственно основного и дополнительного блоков памяти микропрограмм.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Процессор для выполнения математических операций | 1986 |

|

SU1381533A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1798781A1 |

| Устройство для управления цифровой вычислительной машиной | 1974 |

|

SU520591A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах управления технологическим оборудованием. Цель изобретения - расширение области применения за счет увеличения области памяти микропрограмм. Процессор содержит синхронизатор, блок управления, блок памяти микропрограмм, регистр микрокоманд, регистр управления вводом-выводом, блок хранения флагов, блок анализа обрабатываемого бита и условий, модификатор микропрограмм, два блока ключей с трехстабильным выходом, регистр кода обрабатываемого бита, дешифратор маски обрабатываемого бита, арифметико-логический блок, блок ввода - вывода, два элемента ИЛИ. Наличие дополнительного объема памяти в блоке памяти микропрограмм позволяет увеличить количество сервисных программ, тестовых и диагностических программ. 6 ил.

Фие.2

Ј$Пф

5Z

ФГ/

У Л

Г

SI50SS

Фи8.5

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-03-15—Публикация

1988-01-06—Подача