(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ДВУХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1211747A1 |

| Устройство для сопряжения двух вычислительных машин | 1979 |

|

SU885988A1 |

| Устройство для обмена информацией | 1986 |

|

SU1336017A1 |

| Устройство для обмена информацией | 1985 |

|

SU1334151A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ДВУХ ЭВМ | 1988 |

|

RU1554636C |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1251093A1 |

| Устройство для сопряжения ЭВМ с датчиками | 1987 |

|

SU1427375A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1987 |

|

SU1411764A1 |

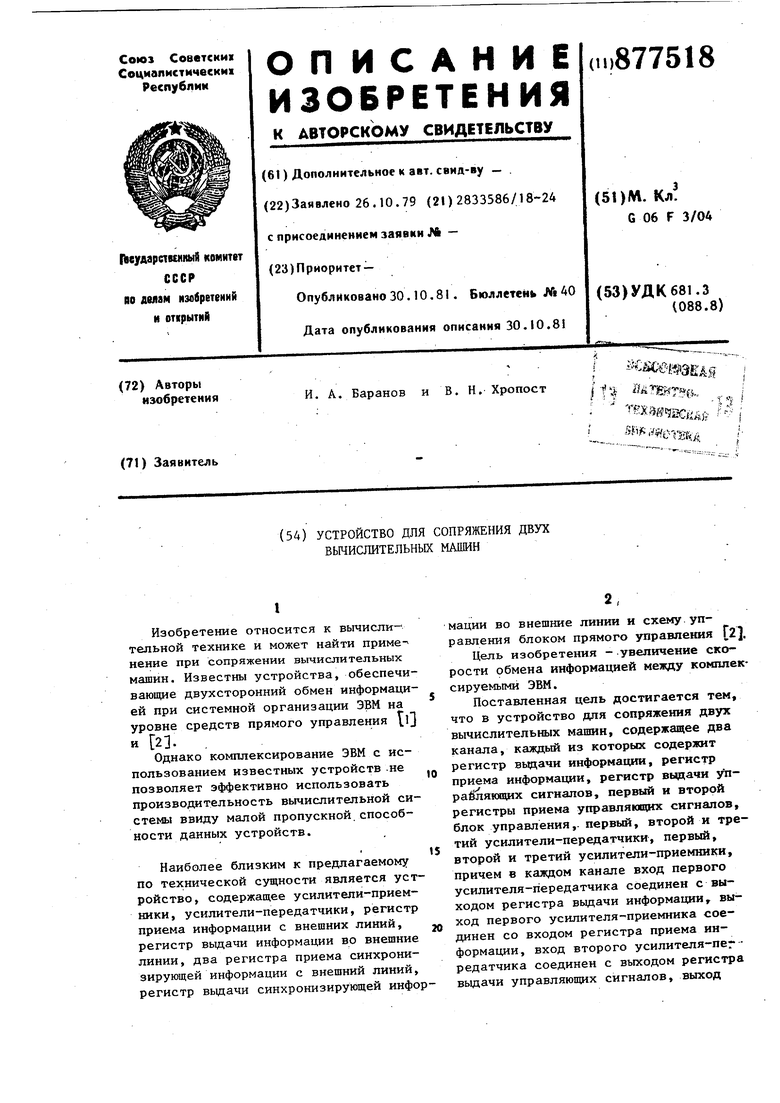

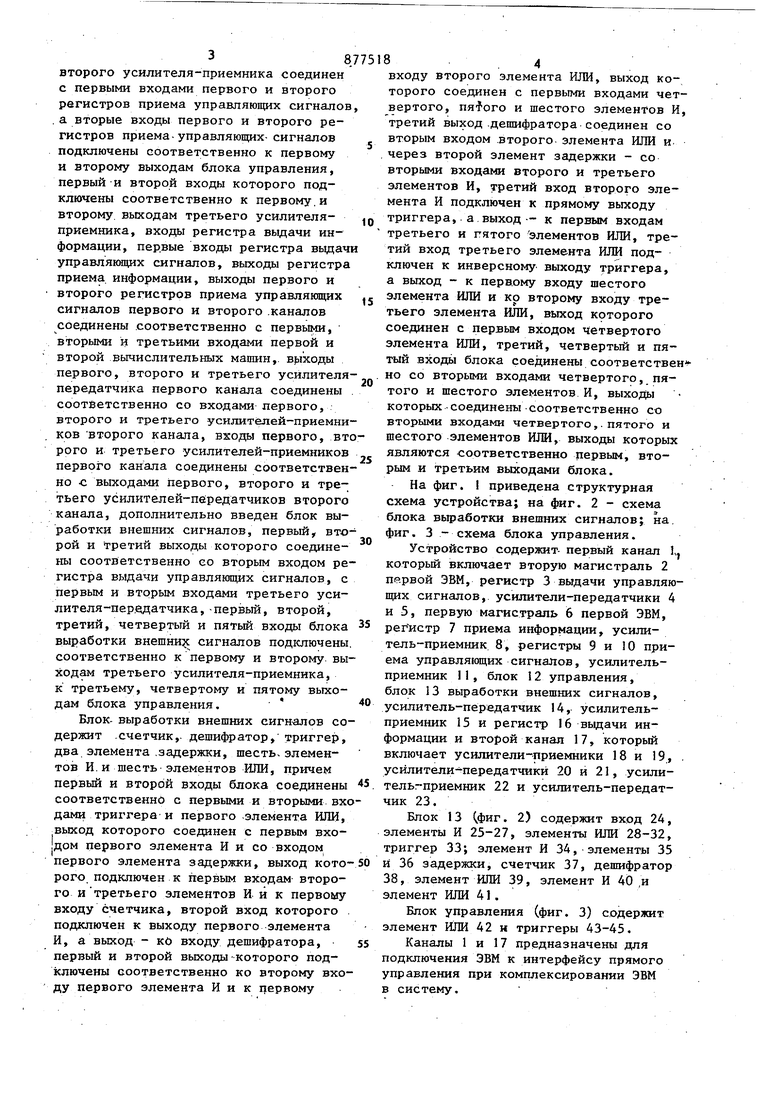

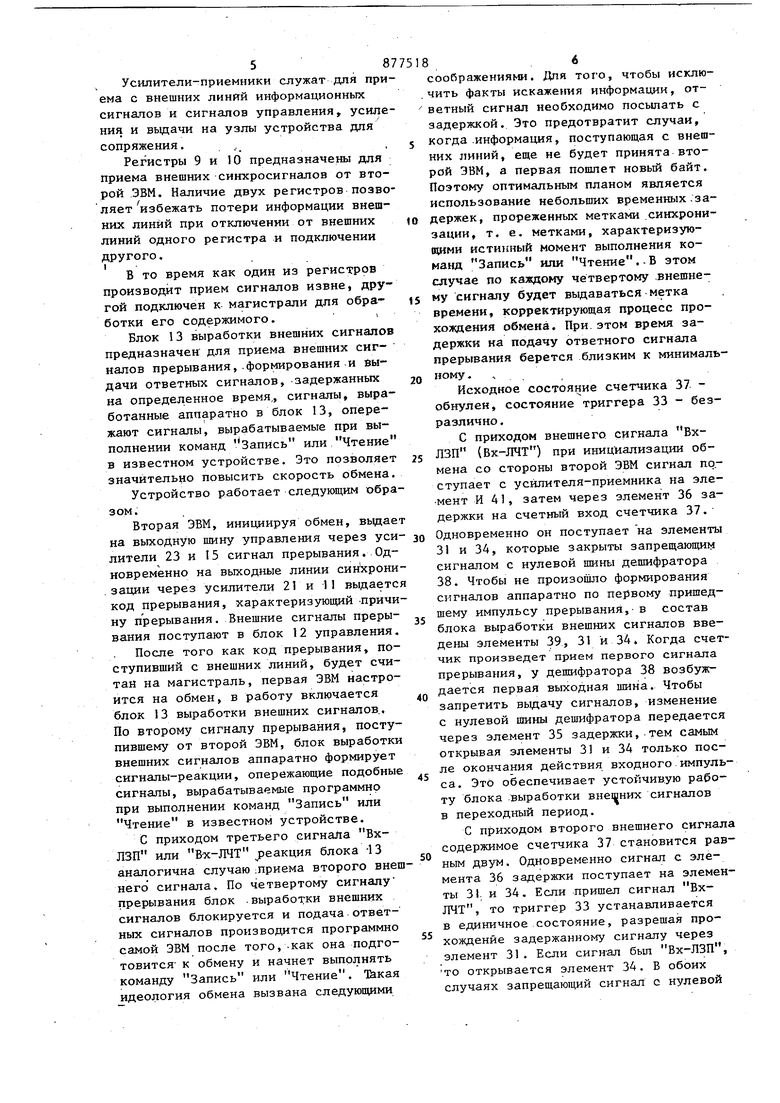

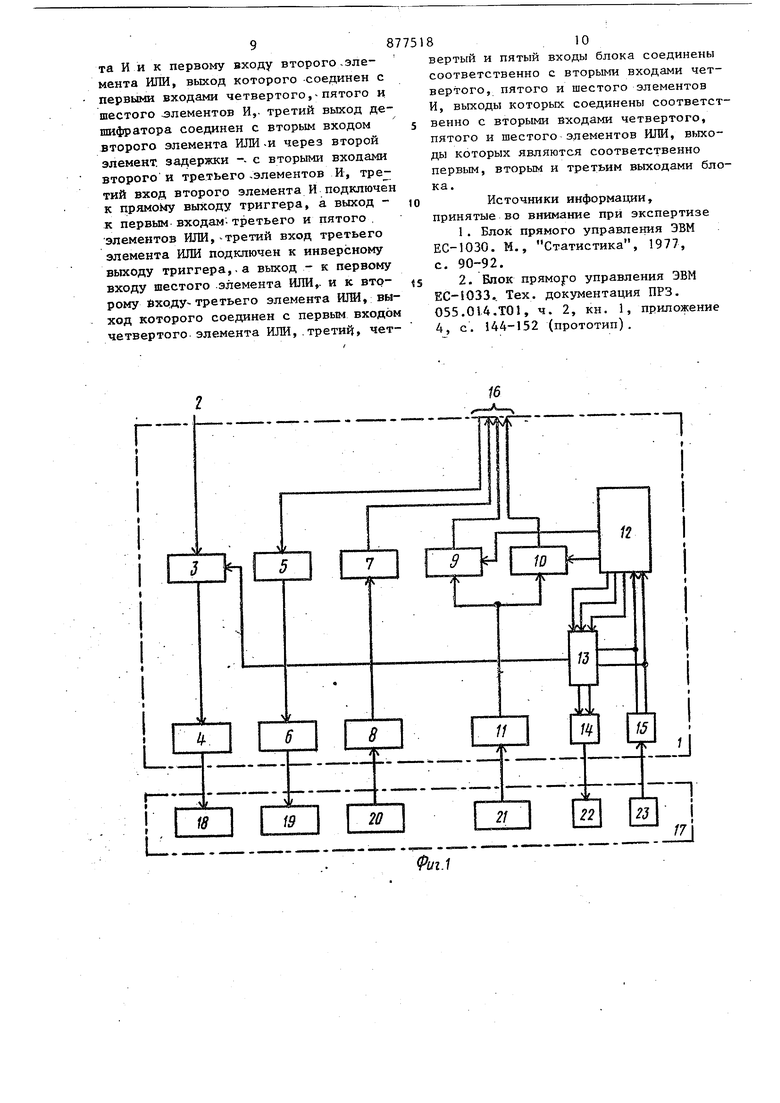

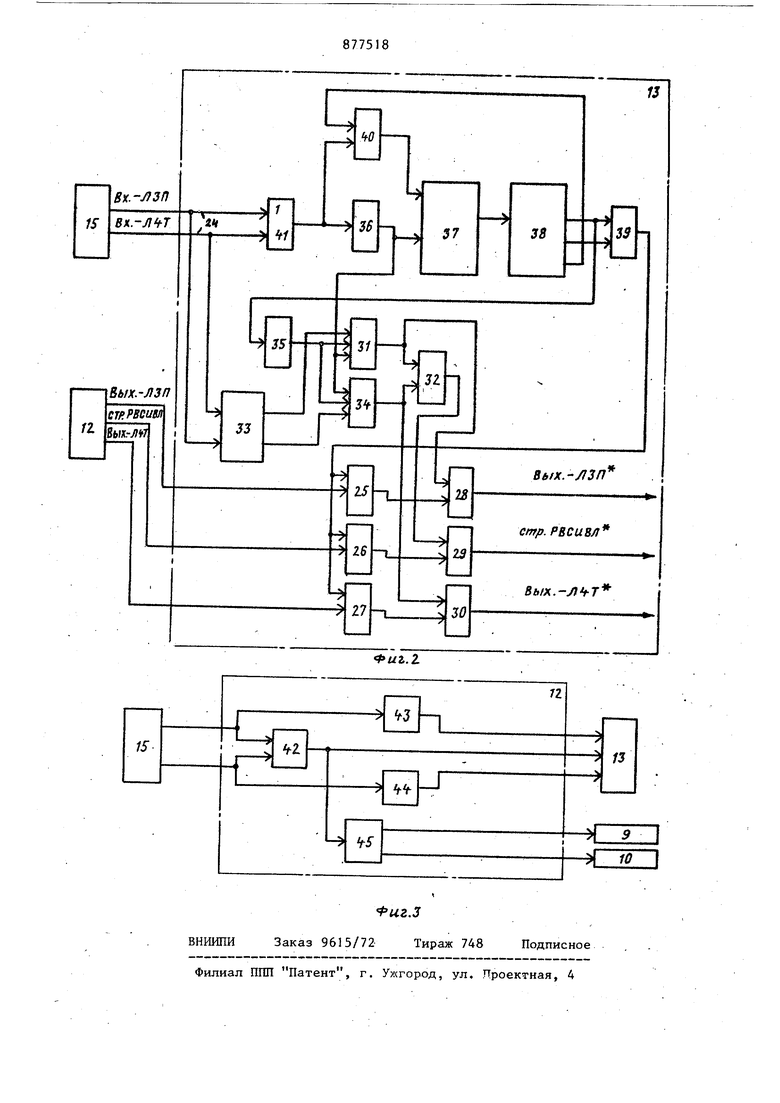

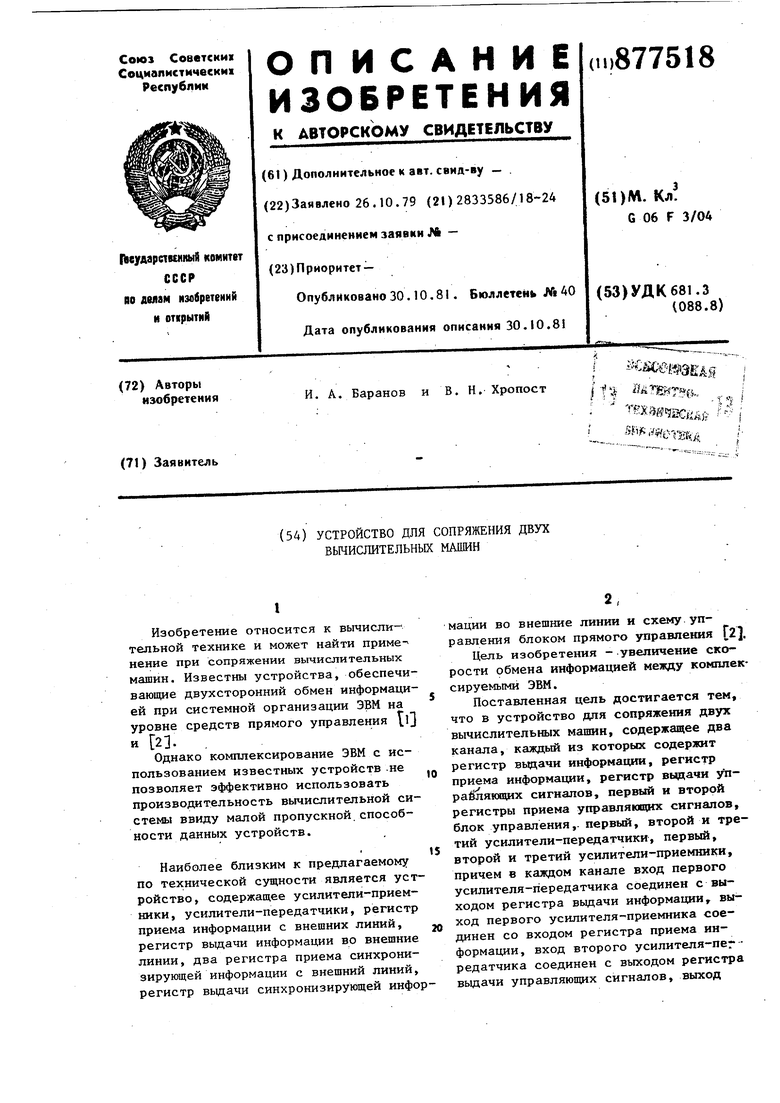

Изобретение относится к вычислительной технике и может найти применение при сопряжении вычислительных машин. Известны устройства, обеспечивающие двухсторонний обмен информацией при системной организации ЭВМ на уровне средств прямого управления 3 и 2. , Однако комштексирование ЭВМ с использованием известных устройств -не позволяет эффективно использовать производительность вычислительной системы ввиду малой пропускной.способности данных устройств. Наиболее близким к предлагаемому по технической сущности является устройство, содержащее усилители-приемники, усилители-передатчики, регистр приема информации с внешних линий, регистр вьщачи информации во внешние линии, два регистра приема синхронизирующей информации с внешний линий, регистр вьщачи синхронизирующей инфор мации во внешние линии и схему управления блоком прямого управления Г2. Цель изобретения - .увеличение скорости обмена информацией между комплексируемыми ЭВМ. Поставленная цель достигается тем, что в устройство для сопряжения двух вычислительных машин, содержащее два канала, каждый из которых содержит регистр выдачи информации, регистр приема информации, регистр выдачи уп- раёлякицих сигналов, первый и второй регистры приема управляющих сигналов, блок управления,, первый, второй и третий усилители-передатчики, первый, второй и третий усилители-приемники, причем в каждом канале вход первого усилителя-передатчика соединен с выходом регистра выдачи информации, выход первого усилителя-приемника соединен со входом регистра приема информации, вход второго усилителя-пег редатчика соединен с выходом регистра выдачи управляющих сигналов, выход второго усилителя-приемника соединен с первыми входами первого и второго регистров приема управляющих сигналов а вторые входы первого и второго регистров приема-управляюпщх-сигналов подключены соответственно к первому и второму выходам блока управления, первый и второй входы которого подключены соответственно к первому.и второму, выходам третьего усилителяприемника, входы регистра вьщачи информации, первые входы регистра вьщачи управляющих сигналов, выходы регистра приема информации, выходы первого и второго регистров приема управляющих сигналов первого и второго .каналов соединены .соответственно с первыми, вторыми и третьими входами первой и второй вычислительных машин,. в 1ходы первого, второго и третьего усилителяпередатчика первого канала соединены соответственно со входами первого, второго и третьего усилителей-приемников второго канала, входы первого, вто рого и третьего усилителей-приемников первого канала соединены соответственно -с выходами первого, второго и тре-; тьего усилителей-передатчиков второго канала, дополнительно введен блок выработки внешних сигналов, первый, второй и третий выходы которого соединены соответственно со вторым входом регистра выдачи управляющих сигналов, с первым и вторым входами третьего усилителя -пер.едатчика, -первый, второй, третий, четвертый и пятый входы блока выработки внешни: сигналов подключены соответственно к первому и второму вы ходам третьего усилителя-приемника, к третьему, четвертому и пятому выходам блока управления. Блок- выработки внешних сигналов со держит -счетчик,- дешифратор, триггер, два элемента .задержки, шесть, элементов И. и шесть элементов ИЛИ, причем первый и второй входы блока соединены соответственно с первыми и вторыми.вх дами триггера и первого -элемента ИЛИ, выход которого соединен с первым первого элемента И и со входом первого элемента задержки, выход кото рого подключен к первым входам второго и третьего элементов Инк первому входу счетчика, второй вход которого подключен к выходу первого элемента И, а выход - ко входу дешифратора, первый и второй выходы которого подключены соответственно ко второму вхо ду первого элемента И и к первому входу второго элемента ИЖ, выход которого соединен с первьп ш входами четвертого, пятого и шестого элементов И, третий выход .дешифратора соединен со вторым входом .второго элемента ИЛИ и через второй элемент задержки - со вторыми входами второго и третьего элементов И, третий вход второго элемента И подключен к прямому выходу триггера, а.выход-- к первым входам третьего и гятого элементов ИЛИ, третий вход третьего элемента ИЛИ подключен к инверсному выходу триггера, а выход - к перв.ому входу шестого элемента ИЛИ и ко второму входу третьего элемента ИДИ, выход которого соединен с первым входом четвертого элемента ИЛИ, третий, четвертый и пятый входь блока соединены соответствен но со вторыми входами четвертого, пятого и шестого элементов И, выходы которых-соединены -соответственно со вторыми входами четвертого,.пятого и шестого элементов ИЛИ, выходы которых являются соответственно первым, вторым и третьим выходами блока. На фиг. I приведена структурная схема устройства; на фиг. 2 - схема блока выработки внешних сигналов; на. фиг. 3 - схема блока управления. Устройство содержит- первый канал l.j который включает вторую магистраль 2 первой ЭВМ, регистр 3 выдачи управляющих сигналов,, усилители-передатчики 4 и 5, первую магистраль 6 первой ЭВМ, регистр 7 приема информации, усилитель-приемник 8, регистры 9 и 10 приема управляющих сигналов, усилительприемник 11, блок 12 управления, блок 13 вьфаботки внешних сигналов, усилитель-передатчик 14, усилительприемник 15 и регистр 16 выдачи информации и второй канал 17, который включает усилители-приемники 18 и 19, . усилители-передатчики 20 и 21, усилитель-приемник 22 и усилитель-передатчик 23. Блок 13 фиг. 2) содержит вход 24, элементы И 25-27, элементы ИЛИ 28-32, триггер 33; элемент И 34, элементы 35 и 36 задержки, счетчик 37, дешифратор 38, элемент ИЛИ 39, элемент И 40 ,и элемент ИЛИ 41. Блок управления (фиг. 3) содержит элемент ИЛИ 42 и триггеры 43-45. Каналы 1 и 17 предназначены для подключения ЭВМ к интерфейсу прямого управления при комплексированяи ЭВМ в систему. 58 Усилители-приемники служат для при ема с внешних линяй информационных сигнапов и сигналов управления, усиле ния и выдачи на узлы устройства для сопряжения. . Регистры 9 и 10 предназначены для приема внешних синхросигналов от второй .ЭВМ. Наличие двух регистров позво ляет избежать потери информации внеш них линий при отключении от внешних линий одного регистра и подключении другого. I В то время как один из регистров производит прием сигналов извне, другой подключен к магистрали для обработки его содержимого. Блок 13 выработки внешних сигналов предназначен для приема внешних сигналов прерывания,.формирования-И йыдачи ответных сигналов, -задержанных на определенное время,, сигналы, выработанные аппаратно в блок 13, опережают сигналы, вырабатывае 1ые при выполнении команд ЗапИсь или,Чтение в известном устройстве. Это позволяет знaчйтeль o повысить скорость обмена. Устройство работает следующим обра зом. Вторая ЭВМ, инициируя обмен, выдае на выходную шину управления через уси лители 23 и 15 сигнал прерывания..Одновременно на выходные линии синЬсрони .зации через усилители 2Г и 11 выдаетс код прерывания, характеризующий лричи ну прерывания. Внешние сигналы прерывания поступают в блок 12 управления. После того как код прерывания, поступивший с внешних линий, будет считан на магистраль, первая ЭВМ настроится на обмен, в работу включается блок 13 выработки внешних сигналов.. По второму сигналу прерывания, поступившему от второй ЭВМ, блок выработки внешних сигналов аппаратно формирует сигналы-реакции, опережающие подобные сигналы, вырабатываемые программно при выполнении команд Запись или Чтение в известном устройстве. С приходом третьего сигнала ВхЛЗП или В-х-ЛЧТ реакция блока -13 аналогична случаю ;приема второго внеш него сигнала. По четвертому сигналу прерывания блок .выработки внешних сигналов блокируется и подача ответных сигналов производится программно самой ЭВМ после того,-как она подготовится к обмену и начнет выполнять команду Запись или Чтение. Тикая идеология обмена вызвана следующими 86 соображениями. Для того, чтобы исключить факты искажения информации, ответный сигнал необходимо посылать с задержкой. Это предотвратит случаи, когда .информация, поступающая с внешних линий, еще не будет принята второй ЭВМ, а первая пошлет новый байт. Поэтому оптимальным планом является использование небольших временных -задержек, прореженных метками .синхронизации, т. е. метками, характеризующими исти}шый момент выполнения команд Запись или Чтение.-В этом случае по каждому четвертому .внешнему сигналу будет вьщаваться метка времени, корректирующая процесс прохозкдения обмена. При. этом время задержки на подачу ответного сигнала прерывания берется близким к минимальному. , Исходное состояние счетчика 37 обнулен, состояние триггера 33 - безразлично . С приходом внешнего сигнала ВхЛЗП () при инициализации обмена со стороны второй ЭВМ сигнал по.ступает с усилителя-приемника на элемент ИД, затем через элемент 36 задержки на счетный вход счетчика 37. Одновременно он поступает на элементы 31 и 34, которые закрыты запрещающие сигналом с нулевой шины дешифратора 38. Чтобы не произошло формирования сигналов аппаратно по первому пришедшему импульсу прерывания,-в состав блока выработки внешних сигналов введены элементы 39, 31 и 34. Когда счетчик произведет прием первого сигнала прерывания, у дешифратора 38 возбуждается первая выходная шина. Чтобы запретить вьщачу сигналов, изменение с нулевой шины дешифратора передается через элемент 35 задержки,.тем самым открывая элементы 31 и 34 только после окончания действия входного импульса. Это обеспечивает устойчив.ую работу блока выработки внешних сигналов в переходный период. С приходом второго внешнего сигнала содержимое счетчика 37 становится равным двум. Одновременно сигнал с элемента 36 задержки поступает на элементы 31. и 34. Если пришел сигнал ВхЛЧТ, то триггер 33 устанавливается в единичное состояние, разрешая прохождение задержанному сигналу через элемент 31. Если сигнал бьт Вх-ЛЗП, ТО открывается элемент 34. В обоих случаях запрещающий сигнал с нулевой шины дешифратора 38 снят. Это произведено в предьщущем такте,-когда счетчик 37 принял сигнал прерывания. Аналогичным образом работает блок 13 выработки внешних сигналов.при поотуплении третьего внешнего сигнала. С приходом четвертого сигнала прерывания . счетчик 37 до поступления ла его вход задержанного импульса сбрасывается в ноль элементом И 40,.который пропускает-незадержанный сигнал, с элемента ИЛИ 41 при значении счетчика 37, равном трем. К приходу задержанного сигнала, счет чик 37 будет обнулен и с поступлением импульса на его счетный вход значение его станет равным единице.- Блок начинает работать аналогично поступлению первого сигнала прерывания. Далее цикл повторяется. Чтобы вьщавать сигналы прерывания, сформированные программно,- в случае, когда первая ЭВМ выступает в роли ини циатора, обмена, или в ответ на первый сигнал прерывания, поступивший от второй ЭВМ, в состав блока введен эле мент ИЛИ 39, который разрешает вьщачу сигналов Вых-ЛЗП, Вых-ЛЧТ и стр. РВСИВЛ через элементы-25-27. Таким образом, введенный в устройUTBO блок .выработки внешних сигналов поз.щрляет увеличить скорость обмена, 1Что повышает эффективность -использования вычислительной системы в целом. Формула изобретения 1. Устройство для сопряжения.двух вычислительных машин,-содер: ащее два канала каждый из которых содержит .pe гистр выдачи информации, регистр приема информации, -регистр выдачи управляюш;их сигналов, первый и второй регистры приема управляющих сигналов, блок управления, -первый, второй и третий у сил ители-пере датчики, - первый второй и третий усилители-приемники, причем в каждом канале- вход первого усилителя-передатчика соединен с выходом «егистра вьщачи информации, выход.первого усилителя-приемника соединен, с входом регистра приема информации, вход второго усшштеля-передат чика соединен с выходом -регистра вьзда чи управляющих сигналов, - выход второго усилителя-приемника соединен с пер выми входами первого и второго регист ров приема управляющих сигналов, а вт рые входы первого и второго регистров приема управляющих сигналов подключены соответственно к первому и второму выходам блока управления, первый и второй входа которого подключены ;соответственно к первому и второму выходам третьего усилителягприемника, входы регистра выдачи информации,, первые входы регистра выдачи управляюцих сигналов , выходы регистра приема информации, выходы первого и второго регистров приема управляющих сигналов первого и второго каналов соединены.соответственно с первыми., вторыми и тре- : тьими входами первой и второй вычислительных машин,, выходы первого, второго и третьего усилителя-передатчика первого канала соединены соответственно с входами первого, второго и третьего усилителей-приемников второго канала, входы первого, второго и третьего усилителей-приемников первого канала соединены соответственно с выходами первого, второго и третьего усилителей-передатчиков второго канала, отличающееся тем, что, с целью увеличения скорости обмена, в него вреден блок выработки внешних сигналов, первый, второй и третий выходы которого соединены соответственно с вторым входом регистра выдачи управляющих сигналов, с первым и вторым входами третьего усилителя-передатчика, первый, второй, третий, четвертый и пятый входы блока выработки внешних сигналов подключены соответственно к первому и второму выходам третьего усилителя-приемника, к третьему, четвертому и пятому вькодам блока управления. 2. Устройство по п. 1, о т л и ч а. ю щ е е с я тем, что блок вьфаботки.внешних сигналов содержит счетчик, дешифратор, триггер, два элемента задержки, шесть элементов И и шесть элементов ИЛИ, причем первый и второй входы блока соединены соответственно с первыми и вторыми входами триггера и первого элемента ИЛИ, выход которого, соединен -с первым входом первого элемента И и с входом первого элемента задержки , выход которого-подключен к первым -входам второго и третьего элементов И и к первому входу счетчика, второй вход которого подключен к выходу-первого элемента И, а выход.к входу дешифратора,- первый и второй выходел которого подключены соответственно, к второму входу первого элемен98

та И и к первому входу второго.элемента ИЛИ, выход которого соединен с первыми входами четвертого,-пятого и шестого -элементов И,, третий выход дешифратора соединен с вторым входом второго элемента ИЛИ -и через второй элемент, задержки -- с вторыми входами второго и третьего-элементов И, третий вход второго элемента И подключен к прямому выходу триггера, а выход к первым-входам-третьего и пятого , элементов ИЛИ,-третий вход третьего элемента ИЛИ подключен к инверсному выходу триггера,-а выход - к первому входу шестого .элемента ИЛИ,, и к втррому входу-третьего элемента ИШ, выход которого соединен с первым входом четвертого элемента ИЛИ,.третий, чет810

вертый и пятый входы блока соединены соответственно с вторыми входами четвертого, пятого и шестого элементов И, выходы которых соединены соответственно с вторыми Входами четвертого, пятого и шестого элементов ИЛИ, выходы которых являются соответственно первым, вторым и третьим вьгходами блока.

Источники информации, принятые во внимание при экспертизе

(Риг.1

BK.-JJ3n

1 t1

ли Bn.-JIt-T

0

35

Вых.-лзп

CTKfBCUSJI

33

BvKrMJ

39

38

37

-

Lj

3i

r

Вых.-лзп

2

cm/j. РВСиВЛ

Z3

Sft/x.

30

Фиг.2.

Авторы

Даты

1981-10-30—Публикация

1979-10-26—Подача