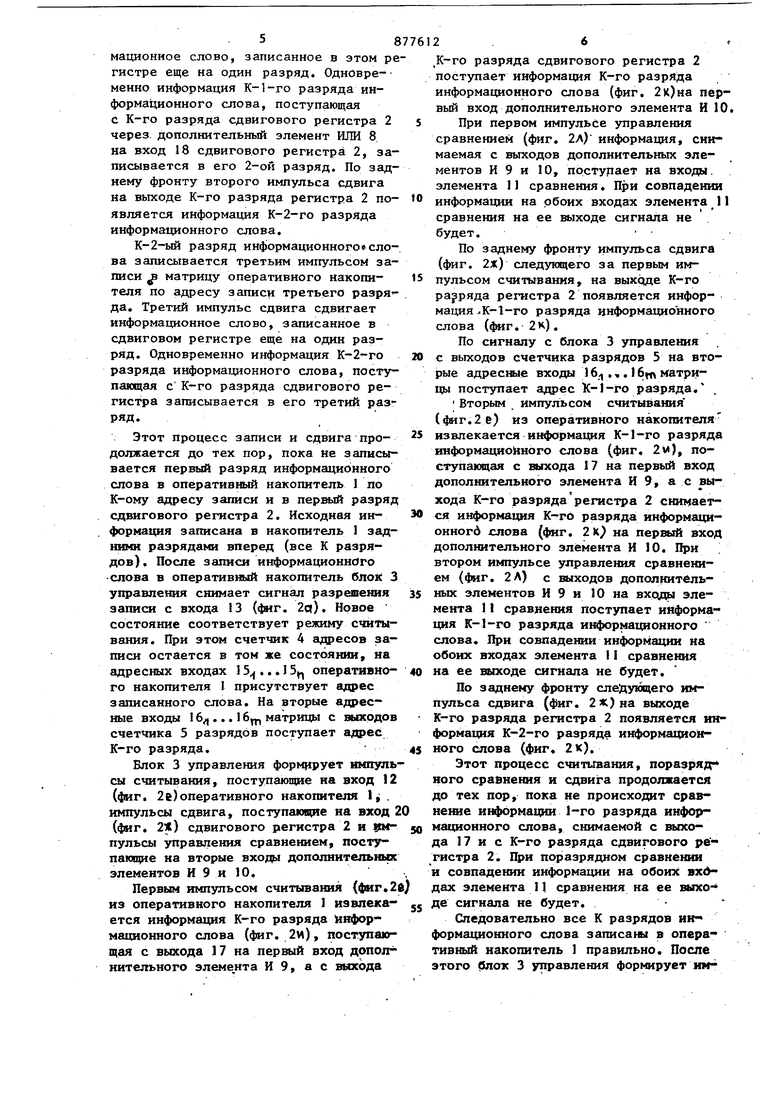

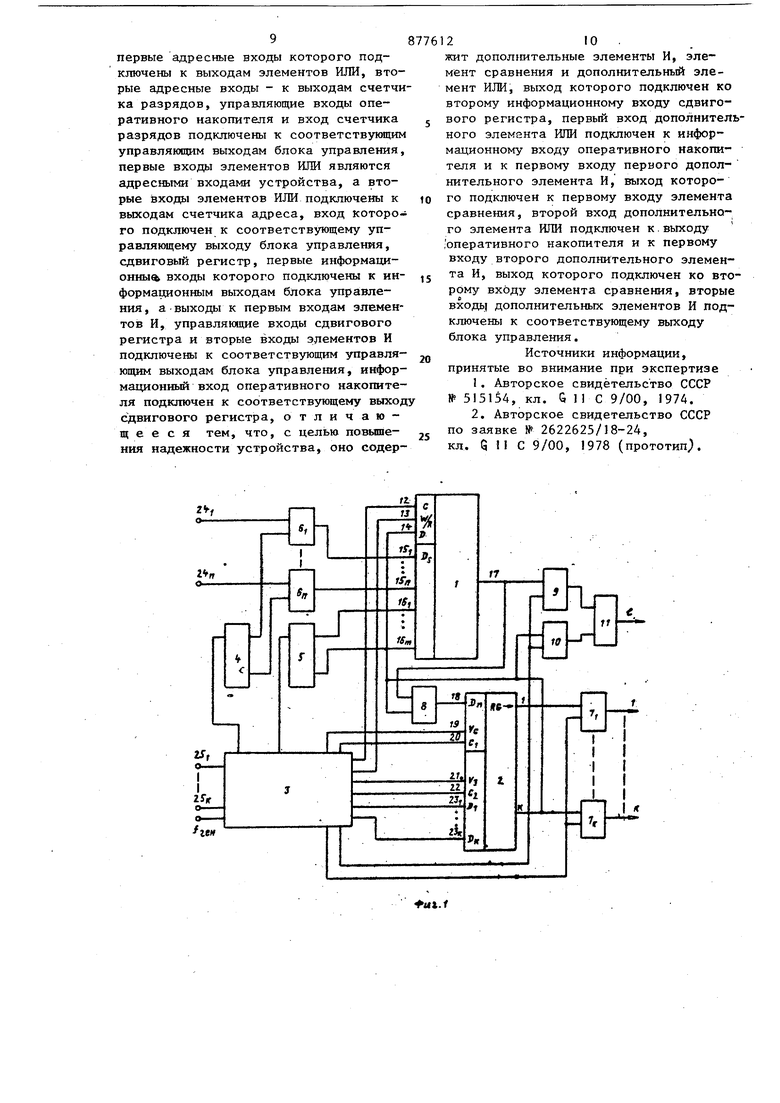

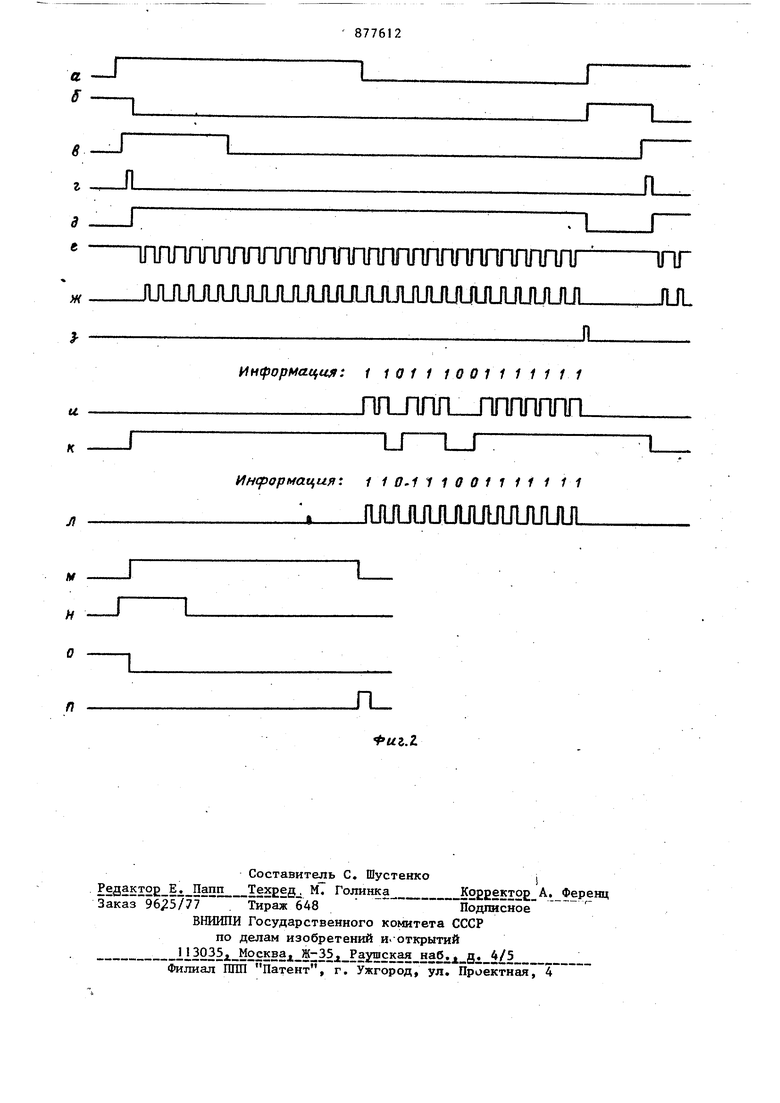

Изобретение относится к вычислительной технике и может быть использо вано для согласования работы высокоскоростных ЦВМ с низкоскоростными уст ройствами ввода-вывода. Известно буферное запоминающее уст ройство, содержащее накопитель, счетчик адресов, блок управления и элемен ты И и ИЛИ D. Недостатком известного устройства является сложность схемной реализации Наиболее близким по технической сущности к предлагаемому является буферное запоминающее устройство, содержащее оперативный накопитель, регистр сдвига, блок управления, счетчик адресов, счетчик разрядов, элементы ИЛИ и элементы И 2. Недостатком известного устройства является то, что в нем возможны случайные искажения информации при записи ее в матрицу оперативной памяти вызванные индустриальными помехами что снижает дос оверность записи. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в буферное запоминающее устройство, содержащее оперативный накопитель, первые адресные входыкоторого подключены к выходам элементов ИЛИ, вторые адресные входы - к выходам счетчика разрядов, управляклцие входы оперативного накопителя и вход счетчика разрядов подключены к соответствукицим управпякщим входам блока управления, первые входы элементов ИЛИ являются адресными входами устройства, а вторые входы элементов ИЛИ подключены к выходам счетчика адреса, вход которого подключен к соответствующему управляющему выходу блока управле- иия, сдвиговый регистр первый информационные входы которого подключены к информационным выходам блока управления, а выходы к первым входам элементов И, управляющие входы сдвигового регистра и вторые входы элементов И 38 подключены к соответствующим управляющим выходам блока управления, информационный вход оперативного накопителя подключен к соответствующему выходу сдвигового регистра, дополнитель но введены дополнительные элементы И, элемент сравнения и дополнительный элемент ИЛИ, выход которого подключен ко второму информационному входу сдви гового регистра, первый вход дополнительного элемента ИЛИ подключен к информационному входу оперативного накопителя и к первому входу первого до полнительного элемента И, выход которого подключен к первому входу эле мента сравнения, вторые входи дополни тельных элементов И подключены к соот ветствующему выходу блока управления. На фиг. 1 приведена структзфная схема устройства; на фиг. 2 показана временная диаграмма работы устройства. Буферное запоминакяцбе устройство содержит матрицу оперативного накопителя 1, сдвиговый регистр 2, блок 3 управления, счетчик 4 адресов, счетчик 5 раэрядов, элементы ИЛИ 6,| ...6, элементы И 7f ...7)i,, дополнительный элемент ИЛИ 8, первый дополнительный элемент И 9, второй дополнительный элемент И 10, элемент 11 сравнения, управляющие входы 12 и- 13 оператив-. кого накопителя, информационный вход первые адресные входы 15 ... 15 , вто- рые адресные входы 16. ... 1 б,, выход t оперативного накопителя, информационйый вход 18 последовательной.-аалиси сдвигового регистра 2, упрарпякяцие входы 19-22, и информационные входы 23.) ...23.J/ параллельной записи сдви гового регистра, входы устройства 24fl...24tc и 25....25ц. Перед началом работы устройства схема приводится в исходное состояние, т.е. на управлякщий вход 13 оперативного накопителя I и управляющий вход 21 сдвигового регистра 2 поступают сигналы разрешения записи (фиг.2 и фиг. 2 6 с блока 3 управления, а на вторые входы элементов И 7...7)с поступает сигнал запрета. На первые адресные входы 15 . ..I5„ матрицы оперативного накопителя через злеме ты ИЛИ 6...6п со счетчика 4 адресов поступает адрес записи первого информационного слова, а на вторые адресшле входы 16...16 со счетчика 5 раз .рядов поступает адрес записи первого 24 . разряда. Схема готова к работе в режиме записи. Устройство работает следующим образом. При поступлении информационного слова на входы 25...25« (фиг, 28)блока 3 управления, блок 3 пропускает это слово на информационные входы 23,..23ц параллельной записи сдвигового регистра 2 и формирует импульс записи на входе 22 (фиг. 2t) этого регистра.« По заднему фронту импульсазаписи (фиг. 2 г.) блок 3 управления выдает сигнал Разрешение сдвига на вход 19 (фиг. 2Э) сдвигового регистра 2 и снимает сигнал разрешения записи со входа 21 (фиг. 25). После этого с блока 3 управления поступают импульсы записи на вход 12 (фиг 2е) оператив4 ного накопителя, и импульсы сдвига ° на вход 20 (4мг. 2) сдвигового регистра 2 и вход счетчиков разрядов 5. импульсы сдвига формируются так, что их передний фронт совпадает с задним фронтом импульсов записи. Информация К-го разряда информационного слова, поступающая с К-го разряда сдвигового регистра 2, записывается первым импульсом записи по входу 12 (ф«г. 9е) по адресу первого разряда в матрицу оперативного накопителя 1. Первым импульсом сдвига по входу 20 (фиг. 2 ) сдвигового регистра 2 информационное слово, записанное в. нем, сдвигается на один разряд, и одновременно информация К-го разряда информационного слова, поступающая с К-го разряда сдвигового регистра 2 через дополнительный элемент ИЛИ 8 на вход 18 сдвигового регистра 2, записывается в его 1-ый разряд. По заднему фронту первого импульса сдвига на выходе К-го разряда регистра 2 появляется информация К-1-го разряда информационного слова. Сигналом, поступающим с блока 3 управления на вход счетчика 5 разрядов, этот счетчик переключается и с его входа на вторые адресные входы 16/1 ... 16|fl матрицы оперативного накопителя поступает адрес записи второго разряда. Информация К-1-го разряда информационнога слова записывается в матрицу оперативного накопителя по адресу записи второго разряда вторым импульсом записи по входу 12 (фиг. 2е) оперативного накопителя 1. Второй импульс сдвига по входу 20 сдвигового регистра 2 сдвигает инфор58мациониое слово, записанное в этом ре гистре еще на один разряд. Одновременно информация К-1-го разряда информационного слова, поступающая с разряда сдвигового регистра 2 через дополнительный элемент ИЛИ 8 на вход 18 сдвигового регистра 2, записывается в его 2-ои разряд. По заднему фронту второго импульса сдвига на выходе К-го разряда регистра 2 появляется информация К-2-го разряда информационного слова. К-2-ый разряд информационного«слова записывается третьим импульсом записи f матрицу оперативного накопителя по адресу записи третьего разря да. Третий импульс сдвига сдвигает информационное слово, записанное в сдвиговом регистре еще на один разряд. Одновременно информация К-2-го разряда информационного слова, поступающая с К-го разряда сдвигового регистра записывается в его третий разряд. Этот процесс записи и сдвига продолжается до тех пор, пока не записывается первый разряд информационного слова в оперативный накопитель 1 по К-ому адресу записи и в первый разряд сдвигового регистра 2. Исходная информация записана в накопитель 1 задними разрядам вперед (все К разрядов) . После записи информационного слова в оперативный накопитель блок 3 управления снимает сигнал разрипения записи с входа 13 (фиг, 2q). Новое состояние соответствует режиму считывания. При этом счетчик 4 адресов записи остается в том же состоянии, на адресных входах 13... 15 оперативного накопителя 1 присутствует адрес записанного слова. На вторые адресные входы 16д... 16 матрицы с выходов счетчика 5 разрядов поступает адрес К-го разряда. Блок 3 управления формирует импуль сы считывания, поступающие на вход 12 (фиг. 2е)оперативного накопителя 1 . импульсы сдвига, поступающие на вход (фиг. 2) сдвигового регистра 2 и уаг пульсы управления сравнением, поступакяцие на вторые входы дополнительньрс элементов И 9 и 10. Первым импульсом считывания (фиг.2 из оперативного накопителя 1 иэвлекается информация К-го разряда Информационного слова (фиг. 2и), поступаю щая с выхода 7 на первый вход дрпол нительного элеме,нта И 9, а с вюсода 2 .6. К-го разряда сдвигового регистра 2 поступает информация К-го разряда информационного слова (фиг. 2к)на первый вход дополнительного элемента И 10. При первом импульсе управления сравнением (фиг. 2Л) информация, снимаемая с выходов дополнительных элементов И 9 и 10, поступает на входы, элемента П сравнения. При совпадении информации на обоих входах элемента 11 сравнения на ее выходе сигнала не будет. По заднему фронту импульса сдвига (фиг. 2ж) следующего за первым импульсом считывания, на выходе К-го разряда регистра 2 появляется информация ..К-1-го разряда информационного слова (4иг. 2к). По сигналу с блока 3 управления с выходов счетчика разрядов 5 на вторые адресное входы 16. .,. 16 матрицы поступает адрес Х-1-го разряда, Вторым импульсом считывания (4иг.2е) из оперативного накопителя извлекается информация К-1-го разряда информационного слова (фиг. 2w), поступамщая с выхода 17 на первый вход дополнительного элемента И 9, ас выхода К-го разряда регистра 2 снимается информация К-гО разряда информахц онногб слова (фиг. 2К на первый вход дополнительного элемента И 10. При втором импульсе управления сравнением (фиг. 2 Л) с выходов дополнительных элементов И 9 и 10 на вхрды элемента 1I сравнения поступает информация К-1-ГО разряда И1 рмационного слова. При совпадении информации на обоих входах элемента i1 сравнения на ее выходе сигнала не будет. По заднему фронту сле;цу1бщего импульса сдвига (фиг, 2 Ж) на выходе К-го разряда регистра 2 появляется информация К-2-ГО разряда информационного слова (фиг, 2 к). Этот процесс считывания, поразряд ного сравнения и сдвига продолжается до тех пор, пока не происходит сравнение информации 1-го разряда информационного слова, снимаемой с выхода 17 и с К-го разряда сдвигового регистра 2, При поразрядном сравнении и совпадении информации на обоих вхддах элемента 11 сравнения на ее вьпсо- де сигнала не будет. Следовательно все К разрядов ин- формационного слова записан 1 в оперативный накопитель 1 правильно. После этого блок 3 управления формирует им7 8

пульс (фиг. 23), которьй поступает на вход счетчика 4 адресов и переключает его, выбирая адрес следующего информационного слова. Кроме того, блок 3 управления сштает сигнал разрешения сдвига со входа19 (фиг. 2д), подает сигнал разрешения параллельной записи на вход 20 (фиг. 2 S) сдвигового регистра 2 и подает сигнал разрешения записи на вход 13 (фиг. 2ci) операти ного накопителя 1. Таким образом, буферное запоминающее устройство готово к записи следующего информационного слова.

В случае несовпадения информации по какому-либо разряду информационного слова, снимаемой с выхода 7 и с К-го разряда сдвигового регистра 2, при соответствующем импульсе управле,ния сравнением на выходе элемента 11 сравнения появляется импульс сигнала.

Этот сигнал используется для повторения параллельной записи информационного слова из блока 3 управления в сдвиговый регистр 2 и поразрядной переписи его в оперативный накопитель 1

с последующим процессом поразрядного сравнения информации с помощью элемента 11 сравнения, описанного вьппе. Повторение записи и последующее поразрядное сравнение информации осуществляется в паузе между импульсами следования информационных слов (фиг,2

После записи определенного числа информационных слов, которое определяется емкостью счетчика Д адресов Записи, блок 3 управления снимает сигнал разрешения записи со входа 13. Это состояние соответствует режиму считывания. Кроме того, блок 3 управления устанавливает счетчик 5 разрядов в состояние, соответствующее адресу первого разряда считывания.

Рассмотрим работу устройства в режиме считывания . Адрес считываемого информационного слова поступает на входы 24...24п элементов ИЛИ 6...6 (фиг. 2) и через эти элементы - на первые адресные входы 15;...15f оперативного накопителя 1. На вторые адресные входы 16... 16 с выходов счетчика 5 разрядов поступает адрес первого разряда считывания.

Блок 3 управления формирует сигналы разрешения сдрига (фиг. 2м) и запрет записи (фиг. 25) , поступающие соответственно на.входы 19 и 21 сдвигового регистра 2, а также им28

пульсы считывания (фиг. 2е) , поступающие на вход 12, и сдвига (фиг. 2 ж , поступаюп(ие на вход 20 сдвигового регистра 2. Так как информация в буферное запоминающее устройство была записана задними разрядами вперед, то первым импульсом считывания (фиг. 2е) извлекается из матриць оперативной памяти информация К-го разряда информационного слова, которая с выхода 17 поступает через дополнительный элемент ИЛИ 8 на информационный вход 18 последовательной записи сдвигового регистра 2 и записывается в первый разряд этого регистра первым импульсом сдвига. Счетчик 5 разрядов по сигналу с блока 3 управления подготавливает адрес второго разряда считывания. Вторым импульсом считывания извлекается информация К-1-го разряда информациднного слова. Эта информация поступает на вход 18 сдвигового регистра 2. Вторым импульсом сдвига информация К-го разряда, записанная в первом разряде сдвигового регистра 2 сдвигается на один разряд, а в первый раз- ряд регистра 2 записывается информация К-1-ГО разряда. Процесс считывания информации из оперативного Hagoпителя 1 и запись ее в сдвиговый регистр 2 продолжается, пока не будет считано все информационное слово. После считывания первого разряда информационного слова и записи его в сдвиговый регистр 2, блок 3 управления подает сигнал (фиг. 2 Л) на вторые вход элементов И 7 ... 7к и информация выбранного слова с выходов элементов И 7 t..7(j поступает на приемно устройство. Следующее информационное слово считывается из матрицы оперативного накопителя J аналогичным образом Использование предлагаемого изобретения позволяет повысить достоверность записи информации в оперативный накопитель. Ошибки, возникающие при сбое во время записи какого-либо информационного слова в накопитель 1, устраняются повторением записи этого слова с последующим поразрядным сравнением информации, осуществляемыми в паузе между импульсами следования информационных слов. Таким образом, повышается надежность устройства.

Формула изобретений

Буферное запоминающее устройство, содержащее оперативный накопитель. 9 первые адресные входы которого подключены к выходам элементов ИЛИ, вторые адресные входы - к выходам счетчи ка разрядов, управляющие входы оперативного накопителя и вход счетчика разрядов подключены к соответствующим управляющим выходам блока управления, первые входы элементов ИЛИ являются адресными входами устройства, а вторые входы элементов ИЛИ подключены к выходам счетчика адреса, вход которого подключен к соответствующему управляющему выходу блока управления, сдвиговый регистр, первые информационны% входы которого подключены к информационным выходам блока управления, а выходы к первым входам элементов И, управляющие входы сдвигового регистра и вторые входы элементов И подключены к соответствующим управляющим выходам блока управления, информационный вход оперативного накопителя подключен к соответствующему выход сдвигового регистра, отличающееся тем, что, с целью повышения надежности устройства, оно содер210 . жит дополнительные элементы И, элемент сравнения и дополнительньй элемент ИЛИ, выход которого подключен ко второму информационному входу сдвигового регистра, первый вход дополнительного элемента ИЛИ подключен к информационному входу оперативного накопителя и к первому входу первого дополнительного элемента И, выход которого подключен к первому входу элемента сравнения, второй вход дополнительного элемента ИЛИ подключен к.выходу оперативного накопителя и к первому входу второго дополнительного элемента И, выход которого подключен ко второму входу элемента сравнения, вторые входь дополнительных элементов И подключены к соответствующему выходу блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 515154, кл. Q 11 С 9/00, 1974. 2.Авторское свидетельство СССР по заявке № 2622625/18-24, кл. Q П С 9/00, 1978 (прототип. Инсрормаци : i i о f 1 1001111111 пп ппп ппппппп

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1084890A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Буферное запоминающее устройство | 1982 |

|

SU1048516A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для поиска информации | 1989 |

|

SU1686464A1 |

| Устройство для сопряжения абонентов с цифровой вычислительной машиной | 1985 |

|

SU1277123A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели переменного тока | 1989 |

|

SU1793458A1 |

| Устройство для выбора заданного числа повторений двоичных чисел | 1984 |

|

SU1267402A1 |

Инсрормация:

M

н о

п

Г1

Puz.i i 1 0-1 11001111111 ппппппппппппппп

Авторы

Даты

1981-10-30—Публикация

1980-02-27—Подача