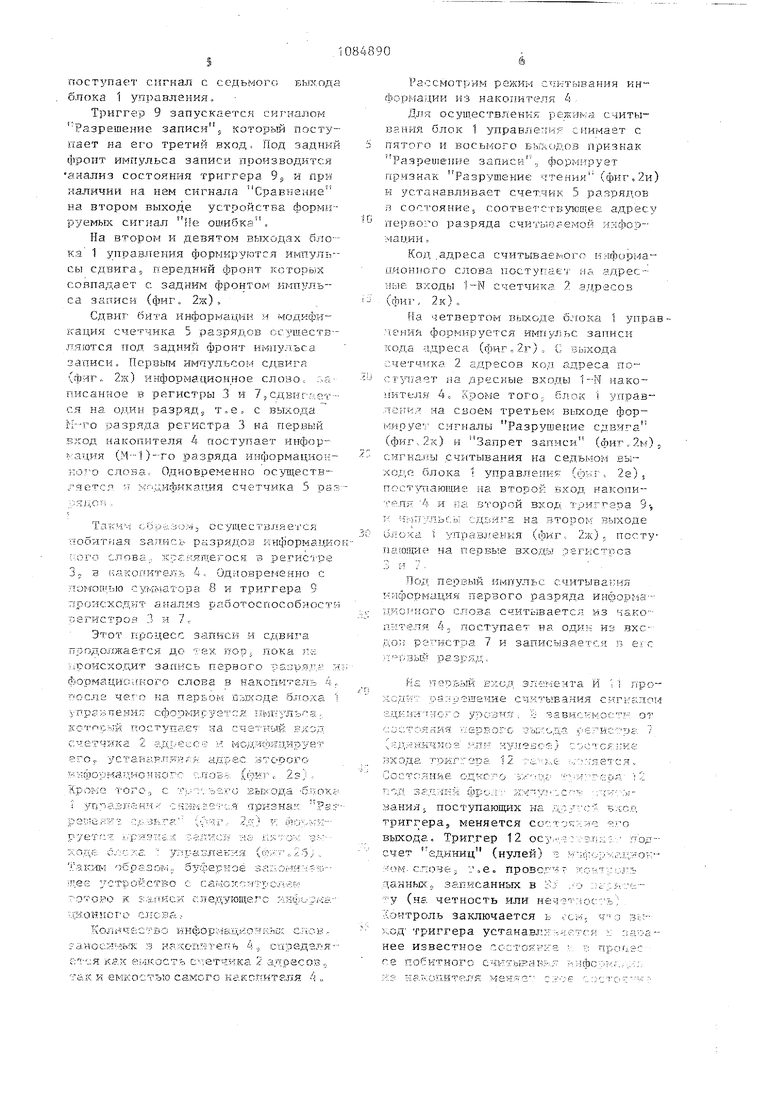

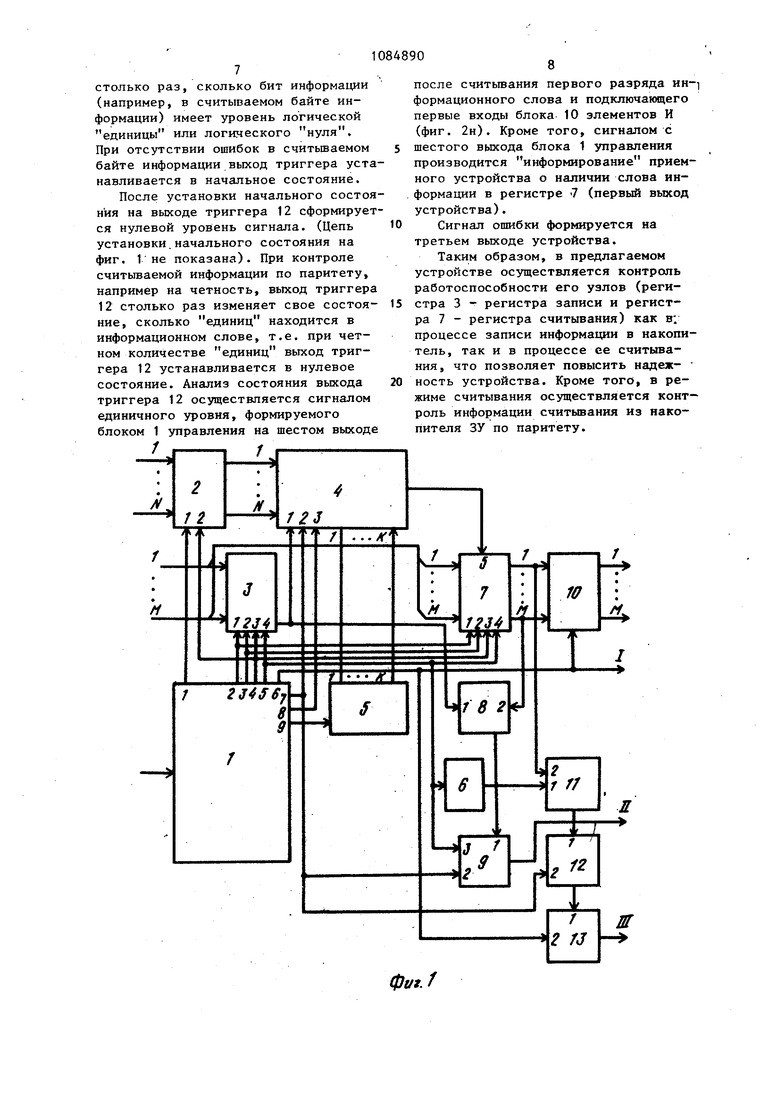

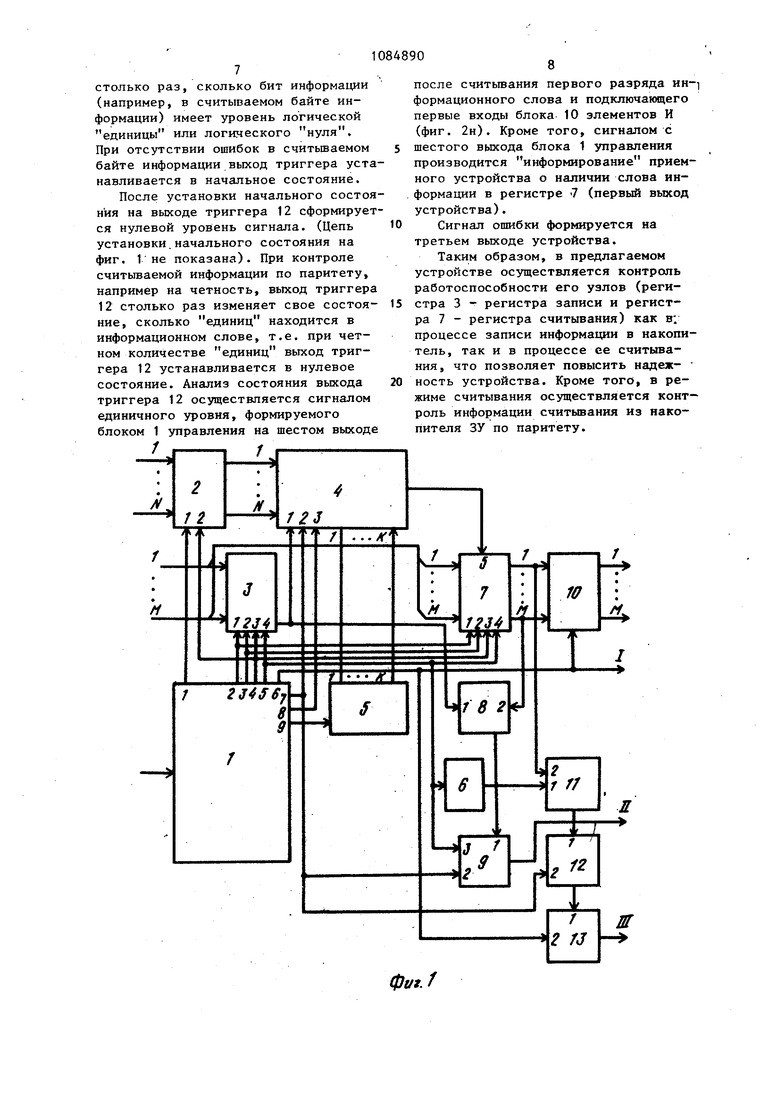

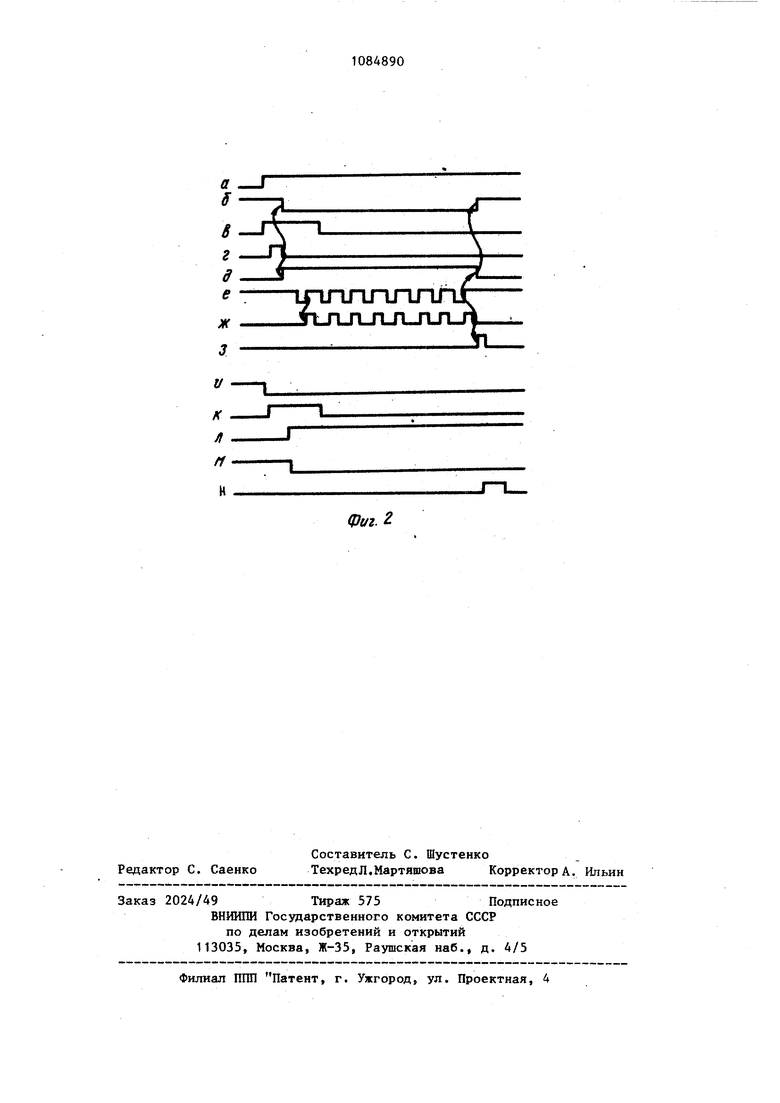

Изобретение относится к вычислительной технике, в частности к буферным запоминающим устройствам (ЗУ Известно буферное запоминающее устройство, содержащее оперативный накопитель, счетчики адресов записи ji считьюания, входной и выходной ре гистры, дешифратор адреса, блок управления, элементы И и ИЛИ, приче одни из выходов блока управления подключены соответственно к входу счетчика адресов, управляющему вход оперативного накопителя и первым входам элементов И, .вькоды счетчика адреса соединены с первыми входа ми элементов ИЛИ, вторые входы которых подключены к одним из входов устройства Однако данное устройство имеет низкую достоверность передаваемой 6т передатчика к приемнику информаци из-за отсутствия контроля работоспособности оборудования ЗУ. Известно также буферное запоминающее устройство, содержащее блок памяти, входные и выходные элементы MS, блок, реагирующий на запись-счит вание данных из памяти, блок запоминания признака переполнения памят регистры адреса записи и считывания . Вследствие отсутствия контроля работоспособности оборудования устройство имеет низкую достоверность передаваемой от передатчика к прием нику информации, Наиболее близким по технической сущности к предлагаемому является буферное устройство, содержащее оперативный накопитель, одни адресные входы которого подключены к выходам счетчика адресов, информационный вход накопителя подключен к выходу первого сдвигового регистра, информационные входы которого являются соответствующими входами устройства , другие адресные входы устройства подключены к выходам счетчика рз-ЗрядоЕц вход которого подклю чен к соо зетствующему выходу блока управления,, управляюпдай вход которо го является входом устройства, блок элементов И, вьгходы которого являют ся информационными выходами устройства, заправляющие входы счетчика адресов, накопителя,первого сдвигового регистра и блока элементов И подключены к соответствующим выхода блока управления ГЗ. Недостатком известного устройства является отсутствие контроля работы регистра сдвига, вследствие чего в накопитель возможна запись недостоверной информации либо передача недостоверной информации приемнику информации, что снижает надежность устройства. Кроме того, отсутствие контроля информации, занесенной в накопитель, например, по паритету, затрудняет в процессе эксплуатации обнаружение неисправного узла ЗУ (в данном случае либо регистра сдвига, либо накопителя), что приводит к увеличению времени восстановления устройства. Цель изобретения - повьппение надежности устройства. Поставленная цель достигается тем, что в буферное запоминающее устройство с самоконтролем, содержащее накопитель, одни адресные входы которого подключены к выходам счетчика адресов, информационный вход накопителя подключен к выходу первого сдвигового регистра, информационные входы которого являются соответствующими входами устройства, другие адресные входы устройства подключены к выходам счетчика разрядов вход которого подключен к соответствующему выходу блока управления, управляющий вход которого является входом устройства, блок элементов И, выходы которого являются информационными выходами устройства, управляющие входы счетчика адресов, накопителя, первого сдвигового регистра и блока элементов И подключены к соответствующим выходам блока управления, дополнительно введены сдвиговый регистр, сумматор по модулю два, триггеры, элементы И и элемент НЕ, выход которого подключен к первому 1ВХОДУ первого элемента И, второй вход первого элемента И подключен к соответствующему выходу второго сдвигового регистра, установочные входы которого подключены к входам первого сдвигового регистра, шрапяяющие входы второго сдвигового регистра подключены к соответствующим входам первого,информационный вход второго сдвигового регистра подключен к выходу накопителя, выход первого сдвигового регистра подклю ен к одному входу сумматора по модулю два, другой вход которого подключен к срответствующему выходу второго сдвигового регистра, выход сум матора по модулю два подключен к первому входу первого триггера, выход которого является одним из упра ляющих выходов устройства, выход которого является одним из управлякицих выходов устройства, выход первого элемента И подключен к первому входу второго триггера, второй вход крторого подключен к второму входу первого триггера и к соответствующему выходу блока управления, выход второго триггера подключен к первому входу второго элемента И, выход которого является другим упра ляющим выходом устройства, второй вход второго элемента И подключен к соответствующему выходу блока управ ления, выход второго триггера подключен к первому входу второго элемента И, выход которого является другим управляющим выходом устройст ва, второй вход второго элемента И подключен к соответствующему ных ду блока управления, вход элемента НЕ подключен к третьему входу первого триггера и к соответствующему выходу блока управления. Второй сдвиговый регистр предна значен для считьгеания побитно инфо мации, хранимой в ЗУ, и вьщачи сло или байта информации приемнику информации, что позволяет проводить контроль данных, записанньк в ЗУ п периметру. Кроме того, в режиме за писи информации в накопитель ЗУ с помощью данного регистра осуществляется контроль первого сдвигового регистра, с помощью, которого осуще ствляется побитная запись информации в накопитель ЗУ. Сумматор по модулю два, входы которого соединены с выходами первого и второго регистров сдвига, сравнивает между собой однотипные биты записываемой информации. Второй триггер, первый и второй элементы И, элемент НЕ предназначены для контроля информаии, считываемой из накопителя ЗУ по паритету (на четность и нечетность) ГЗ На фиг. 1 представлена структурная схема буферного запоминающего. устройства с самоконтролем; на фиг. 2 - временные диаграммы его работы. Буферное ЗУ содержит блок 1 управления, счетчик 2 адресов, сдвиговый регистр 3, накопитель 4, счетчик 5 разрядов, элемент НЕ 6,сдвиговый регистр 7, сумматор 8 по модулю два, триггер 9, блок 10 элементов И, элемент И 11, триггер 12 и элемент И 13. Рассмотрим работу предлагаемого ЗУ с самоконтролем в режимах записи и считывания информации. В режиме записи устройство приводится в следующее исходное состояние: на пятом и восьмом выходах блока 1 управления формируется признак Разрешение записи (фиг.2а,б), Уровень данного сигнала единичный . На выходах 1 - К счетчика 5 разрядов устанавливается код адреса записи первого разряда, а на входы блока 10 элементов И поступает сигнал Запрет с.шестого выхода блока управления. Таким образом, регистры 3 и 7 подготовлены для приема первого информационного слова данных, поступающего по информационным входам устройства, а накопитель 4 подготовлен к побитному режиму записи. При наличии запроса на обработку, поступающего на вход блока 1 управления, наличии кода адреса на адресных входах устройства блок 1 управления на своем четвертом выходе формирует импульсы записи кода адреса и информационного слова данных, поступающих на соогветствуюдие входы счетчика 2 адресов и входы регистров 3 и 7 (фиг. 2г). Под задний фронт импульса записи (фиг. 2д) на третьем вькоде блока 1 управления формируется сигнал Разрешение сдвига, на пятом выходе - сигнал Разрешение записи (фиг. 26), на седьмом выходе - сигнал Запись (фиг. 2е), по которым происходит запись бита информационного слова данных в накопитель 4 по цепи, сое,диняющей последний выход регистра 3 с входом накопителя 4 и входом сумматора 8 по модулю два. А так как второй вход сумматора 8 соединен с одноименным вьпкодом регистра 7, при исправной работе регистров 3 и 7 сформируется сигнал Сравнение нулевого уровня. Данный сигнал поступает на один вход триггера 9, на другой вход которого

поступает сигнал с седьмого выхода блока 1 управления.

Триггер 9 запускается сит-налом Разрешение записи,, который постзпает на его третий вход. Под задний фронт импульса записи производится анализ состояния триггера 9э и при наличии на нем сигнала Сравнение на втором выходе устройства формггруемьвс сигнал Пе ошибка.

На втором и девятом выходах бло-ка 1 управления формируются импульсы сдвига, передний фронт которых совпадает с задним фронтом импульса записи (фиг. 2ж),

Сдвиг информации и модификация счетчика 5 разрядов ссуществ-лягатся под задний фронт импульса записи. Первым импульсом сдвига (фиг. 2ж) информационное слово, аписанное в регистры 3 и 7, сдвг гтлется на один разряд,3 т,,е, с вь.тхода К-то разряда регистра 3 на первьш вкод накопителя 4 поступает инфорацня (М-1)--го разряда информационКО7-О Одновременно осутцеств;яется т кг цификация счетчика 5 раз , .

Таки.1 образом, осуществляе1ся побитная запись разрядов информацио ::ого слова,, хргкяпвгося в perHcipe 3j 3 накопитель 4, Одновременно с помопыо сумлштора 8 и триггера 9 происходит анализ работоспособности оегистров 3 и 7

Этот процесс записи и сдвига продолжается до чвх пор, пока як :,лроисходит запись первого разряди н формацио;.шого слова в накопитель 4,. Госле чего на парь ом оыкоде б, 1 упррвпения сфоркируечсл Г1ьш;льгз. кстпрчтй постзпает на Влзд счетчика 2 -адресе V- мсдитяггиоувч его. уставар.г;ярг и адрес аторого l:- v;фopмa ,нoнкoгc с.позь. (фи)с, 2з/.: Кроме того,-, с Ti,-;. ъ-гго выхода -бпоке уп; азленн-- признак Рв:

KOtfjf- с,:,:.:7: У;5разлцкня (, 5/Таким образ DIM,, буферное SciiiOrKiv i;-ii;ee устройство с сатогс гтролй к ;:.1,1Иси следующегс йнй;с-::йаЦИОКНОГО СЛС;В«,

Кол чйСтво инфорлаци.о:чкь :; с,;Чов. ганосимьж ;я накепнгеп-ь 4,, спредзлкeiCH как si/iKocTb сметчика 2 адресов,, так и емкостью самого какспителя „

Рассмотрим режим считывания информации из накопителя ;

Для осуществления режима считывания блок 1 управлегтил снимает с nsiToro и восьмого Бъглс до5 признак

признак Разрушение чтения (фиг.2и) и устанавливает счетчик 5 разрядов в состояние; соответствующее адресу первого разряда считываемой информардии,

Код, .адреса считываемого информаиконного слова поступает иа адрес-7

1-1ые Бходы I-М счетчика /. адресов (фиг, 2к).

Иа четвертом выходе 6:1ока 1 упрачтения формируется HMnyjibc записи хода адреса (фиг,2г), : выхода ;:четчт{ка 2 адресов код адреса пос, тзп/ает на входы 1--N накоiniTejii 4t Кроме того, клок i управланил на своем третьем выходе формирует сигналы Разрушение сдвига (фиг,, 2к) и Запрет записи (фиг ., 2t-f) сигналы считывания на седьмом выходе блока 1 управления (фиг,, 2е) , постугшюшие на второй вход накопи-:е,пя и па второй вход триггера 9; т- Лг,1гтульсь; ,а на втором выходе 6jTo; a управления (фиг,, 2ж) , поступаюпще на первь;е входы регистров

ЛСД первый икг/ульс считыва1;ия иифорг адия первого разряда информацкогкого с,поза считывается из чакоп::-:те,ля „ поступает на один из вхсдои регистра / и записывается в ev с )1--авы& разряд.

На первый ЕХОД злепента И .. i проход vvr разрешение считывания сигнало

ЕДКНИПНОГО урСЗНЯ , и зависимое: р от

сзсто,яния г: ер БОГо гъг/год, ре:- и;;;Сра 7

входа триггера 12 ::а--;,,.е ,г:,тяетс л „ Состо; н,йе одксго зх-лз,; ,я:Г;иа 12

нанял; поступающих на дру триггера; меняется состо : выхода. Триг.гер 12 осу.-,-;счет единиц (нулей) ; /-У :-(, слоче5 т.во провслчг данньк,, записанн&Ех в У,; . -у (нс, четность или ,лонтроль заключается ь ос; ход- триггера устанавл ; ;,ч,с нее известное состокгхе

с 8 ПОС КТНОГО C V biPt I-Vv ;,-; ,

, Но,т оп ителк столько раз, сколько бит информации (например, в считываемом байте информации) имеет уровень логической единицы или логического нуля. При отсутствии ошибок в считьшаемом байте информации выход триггера уста навливается в начальное состояние. После установки начального состоя ния на выходе триггера 12 сформирует ся нулевой уровень сигнала. (Цепь установки.начального состояния на фиг. 1 не показана). При контроле считываемой информации по паритету, например на четность, выход триггера 12 столько раз изменяет свое состояние, сколько единиц находится в информационном слове, при четном количестве единиц выход триггера 12 устанавливается в нулевое состояние. Анализ состояния выхода триггера 12 осуществляется сигналом единичного уровня, формируемого блоком 1 управления на шестом выходе после считьгоания первого разряда ин-формационного слова и подключающего первые входы блока 10 элементов И (фиг. 2н). Кроме того, сигналом с шестого выхода блока 1 управления производится информирование приемного устройства о наличии слова информации в регистре 7 (первый выход устройства). Сигнал ошибки формируется на третьем выходе устройства. Таким образом, в предлагаемом устройстве осуществляется контроль работоспособности его узлов (регистра 3 - регистра записи и регистра 7 - регистра считывания) как в: процессе записи информации в накопитель, так и в процессе ее считывания, что позволяет повысить надеж- ность устройства. Кроме того, в режиме считывания осуществляется конт роль информации считывания из накопителя ЗУ по паритету.

Фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1980 |

|

SU877612A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для коррекции ошибок в блоках памяти с последовательным доступом | 1987 |

|

SU1510014A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Устройство для коррекции ошибок | 1987 |

|

SU1541677A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU942163A2 |

БУФЕРНОБ: ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО с САМОКОНТРОЛЕМ., содержащее накопитель, одни адресные входы которого подключены к выходам счетчика адресов, информационный вход накопителя подключен к вькоду первого сдвигового регистра, инфор-мационные входы которого являются соответствующими входами устройстваj другие адресные входы устройства подключены к выходам счетчика разрядов, вход которого подключен к соответствующему вькоду блоку управления 5 управляющий вход которого является входом устройства, блок элементов И, выходы которого являются информационными выходами устройства, управляющие входы счетчика адресов, накопителя, первого сдвигового регистра и блока элементов И подключены к соответствующим выходам блока ттравления- отличающееся тем, что, с целью повышения его надежности, оно содержит второй сдвиговый регистр, cyivflnaTOp по модулю два, чриггерь, И и зламект НЕ 5 выход которого подклю хен к первому входу первсго элемента Ид второй вход первого элемента И под клюнен к соответствующему выходу второго сдзигового регистра, установочные входы которого подключены к входам первого сдвигового реги-стра, ;,т1равлягошие входы второго сдвигового регистра подключены к соответствующим входам первого, информационный ;з;;:од сдвигового регистра лодключе:- к вькоду накогЕИ еля,. выход ттер-эгэ сдвигового регистра подкл : че к одному входу а 3 cyMj iaTopa по fiony.T;. . j другой вход .которого л-од,кл;-0: к к состзетств то щему выходу .сдвигового резъ-з гистра, выход сумматора по модуд;ю два подключен к первому входу первого триггера, Еьпгод которого является одним КЗ управляющих выходов Laffi устройства, выход первого элемента И подключен к первому входу второго триггера„ второй вход которого подключеч к втором у входу первого триггера и к соответств аошену выходу блока, управления;, выход второго триггера подключен к nepaoNry рходу второгс элемента И, зьход которого является другим управляющим выходом уСТрОЙСТза,. ЗТОрЭЙ ЗХО/; ;JTOpOrO элемектгг И подключ-З к состветст--вутогаему выходу блока управлект.я ,, элементг. КБ подключен к третъег-: входу, первого триггера и к соотне:;ствуюо ему выходу блока травления,

Фиг. 2.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1984-04-07—Публикация

1982-12-16—Подача