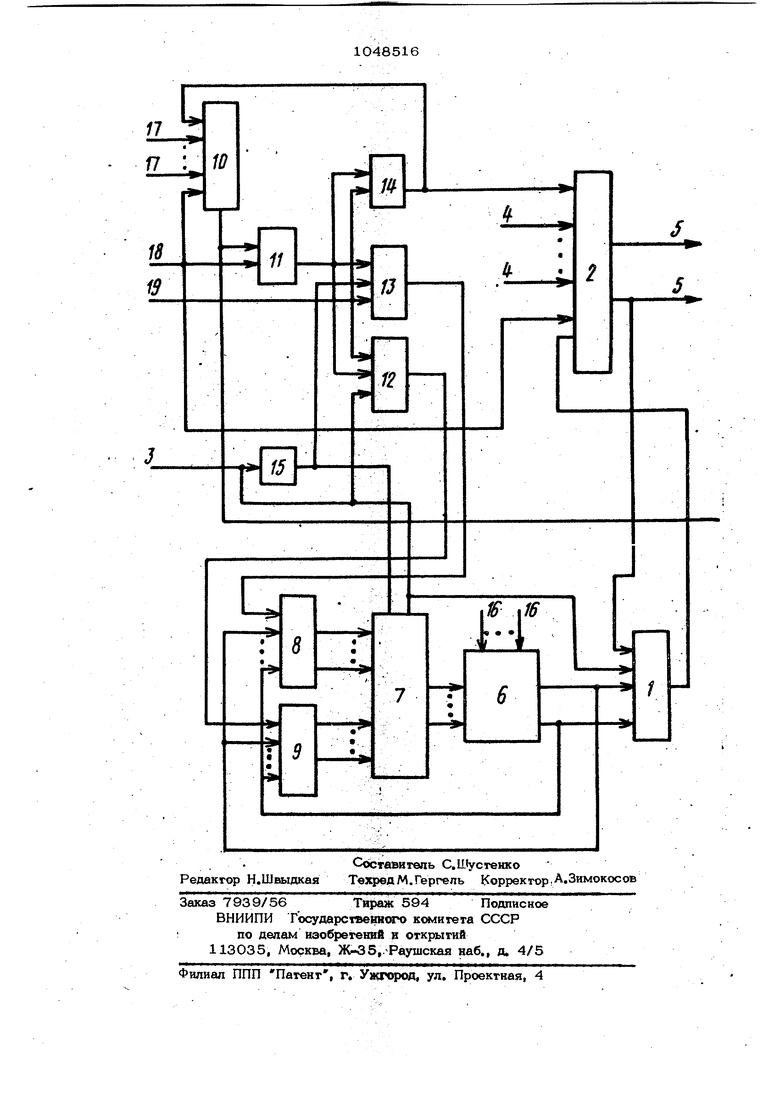

Изобретение огносится к запоминающи устройствам. Известны буферные запоминающие устройства, в которых используется мето перекрестно-последовательного обращения позволяющий осуществлять двусторонний обмен информацией .и совмещать процерсы ввода информации в буферное запоминающее устройство и вывода из него ij Наиболее близким по техническому решению к изобретению является буферное запоминающее устройство, содержащее на ксятитель, информационный выход которого соединен с последовательным входом регистра сдвига,, вход управления накопителя соединен с шиной КОД операции, информационный вход накопителя подключе к выходу последнего разряда регистра сдвига, параллельные информационные входы регистра сдвига являются информа ционными входами устройства, выходы регистра сдвига являются информационными выходами устройства 2 . Недостатком известного устройства является малоэффективное использование памяти цри работе со словами, разрядность которых не кратна степени 2, Кроме того, известное устройство работа ет со словами фиксированной разрядности не позволяет производить операции преобразования форматов слов, а также мат;ричные операции с массивами слов. Цель изобретения - повышение эффек тивносги и расширение области применени устройства за счет преобразования формата данных. Поставленная цель достигается тем, .что в буферное запоминающее устройство, содержащее накопитель, информационный вход которого подключен к одному из выходов сдвигового регистра, информационные выходы сдвигового регистра явлшотся информационными выходами устройства счетчик, элементы И, дополнительно введены в блок И-ИЛИ, регист., триггер, элемент НЕ и сумматор, одни входы которого являются первой группой управляющих входов устройства, другие входы сумматора подключены к выходам блока элементов И-ИЛИ, информационные входы которого подключены к выходам первого и второго регистров, выходы сумматора подключены к информационным входам накопителя и к инфор ационным входам первого и второго регистров, входы записи которых подключены к выходам соответственно первого и второго алементов И, первые входы первого, второго и третьего элементов И подключены к выходу триггера, первый вход которого подключен к входам записи счетчика -и сдвигового регистра и является вторым управляющим входом устройства, второй вход первого элемента И подключен к вторым входам второго и третьего элементов И и является третьим управляющим входом устройств у третий вход первого элемента И подключен к управляющему входу накопителя, к входу элемента НЕ, к. первому управляющему входу блока элементов И-ИЛИ и является чег вертым управляющим входом устройства, третий вход второго элемента И подключен к выходу- элемента НЕ и к второму управляющему входу .блока элементов И-ИЛИ, выход счетчика подключен к второму входу триггера и является управляющим входом устройства, выход третьего элемента И подключен к тактовому входу сдвигового регистра и к тактовому входу счетчика, информационные входы которого являются второй группой управляющих входов устройства. На чертеже приведена струк.турная схема буферного запоминаклцего устройства. Устройство соде ржит накопитель Г, сдвиговый регистр 2, управляющий вход 3 КОД операции, информационные входы 4, выходы 5, сумматор 6, блок 7 элементов И-ИЛИ, регистр 8 адреса записи, регистр 9 адреса чтения, счетчик 1О, триггер 11, элементы И 12-14, элемент НЕ 15, группу управляющих входов 16 для кода модификации адреса, группу управляющих входов 17 для кода длины формата, управляющий вход 18 пуска и управляющий вход 19 синхронизации. Перед началом работы устройство приводится в исходное состояние, т.е. производится обнуление регистра 8 адреса записи и регистра 9 адреса чтения, установка триггера 11 в нулевое состояние, которое запрещает прохождение импульсов синхронизации в устройстве.(Цепи установки в исходное состояние не показаны). В режиме записи устройство работает следующим образом. На вторые входы сумматора 6 постуает код модификации адреса с входов 16. По сигналу на входе 18 производится апись информационного слова через араллельные информационные входы 4 в егистр 2, запись кода с входа 17 кода лины формата в счетчик 10, а акже роисходит установка триггера 11 в еди3104ничное состояние, которое разрешает прохождение импульсов синхронизации с входа 19 через элемент 14 на счетчик 1О и регистр 2. Одновременно сигнал с вход 3 кода операции, пройдя через элемент . НЕ 15, разрешает прохождение импульсов с входа 19 через элемент И 13 на регистр 8 адреса записи, одновременно этот же сигнал прои;зводит коммутацию на сумматор 6 через блок 7 элементов И-И Л И регистра 8 адреса.записи, а также переводит накопитель 1 в состояние готовности к записи, По адресу, сформированному на выхо- . де сумматора 6, производится запись15.

посл днего разряда кнфо лационного слова в накопитель 1. По импульсу, пришедшему в устройство с входа 9, происходит уменьшение содержимого счетчика 1О на единицу, сдвиг содержимого регистра 2, запись в регистр 8 адреса записи последнего h -го-разряда информационного слова.

Адрес записи ( Ц -1) -го разряда информационного слова задается кодом, сфорл1ированным на выходе сумматора 6, который определяется суммой кода, поступакидегр с регистра 8, и кода, поступающего с входов 16, Этот процесс записи и сдвига продолжается-до тех пор, пока не запишутся все разрядьт информационного слова. После того, как записан последний разряд информационного слова, по импульсу с входа 19 происходит сдвиг содержимого регистра 2,запись в регистр 8 ацреса записи поспецнего разряда информационного слова, появляется сигнал лаема со счетчика 1О, который устанавливает триггер 11 в нулевое состояние, бяр кируюшее прохождение импульсов синхронизации в устройстве. Кроме того, сигнал заема является сигналом о записи информационного слова и готовности принять новое слово. Аналогично производится запись в накопитель 1 последуклпих информационных слов, В режиме счи1ъгоания устройство ра ботает следующим образом. На вторые входы сумматора 6 поступает код с входов 16 для модификации адреса. По сигналу на входе 18 пуск . производится запись с входов 17 кода длиныформата в счетчике Ю, а также происходит установка триггера 11 в еди-. ничное состояние, которое разрешает прохождение импульсов синхронизации входов 19 через элемент И 14 на счетчик Ю и регистр 2, Одновременно сигнал с вхоMCffo регистра 2 с одновременной записью М -го разряда информационного слова в 1-й разрящ регистра 2, запись в регистр 9 адреса чтения И -го разр5Ша

информационного слова. Адрес чтения

(п -1) го разряда информационного слова задается кодом, сформированным на выходе сумматора 6, который сятределяется суммой кода, поступающего с регист

ра 9 адреса чтения и кода поступа1ющего с входов 16, Этот процесс считывания и сдвига продолжается до тех пор, пока не Считаются все разряды информационного слова,

После того, как определен адрес счи;тьгеания 1-го разряда информационного слова, по импульсу с входа 19 происходит запись этого разряда в регистр 2 с одновременным сдвигом предыдущих 64 да ; 3 кода операции разрешает прохождекие импульсов с входа 19 через элемент И 12 на регистр 9 адреса чтения, одновременно этот же сигнал производит коммутацию на сумматор 6 через бпмс 7 элементов И-ИЛИ регистра 9 адреса чтения, а также переводит накопитель 1 в соетояние готовности к считыванию, По адресу, сформированному на выходе сумматора 6, производится считывание И -го разряда информационного слова ИЗ накопителя 1; По импульсу синхронизации, пришедшему в устройство с входа 19, происходит уменьшение содержимого счетчика на единицу, сдвиг содержиразрядов в этом регистре, запись в ре-. гистр 9 адреса чтения первого разряда информационного слова, появляется сигнал заема со счетчика 1О, который устанавливает триггер 11 в нулевое состояние,, блокирующее прохождение импульсов синхронизации в устройстве, Кремле того, сигнал заема является сигналом о записи информационного слова в регистр 2 и ГОТОВНОСТИ передачи этого слова с выходов 5, Следующее инфор- Медионное слово считывается из накопителя 1 аналогичным образом, В предлагаемом устройстве устранены недостатки известного, кр. того, оно позволяет производить операции преобразования форматов слов (максимальная длина слова определяется разрядностью регистра 2 сдвига) и матричные «эте.рации с массивами слов, . В режиме транспортирования матрицы устройство работает следующим образом. Допустим, что информационные слова, записанные в накопителе 1, представляют co6tMll столбцы матрицы.;При данной маг. ричной операции необходимо чтобы считан кое слово было образовано одноименными апеме,нтами различных столбцов ма1рицыГ О счетчик 10 с входов кода длины форма та записывается код длины 6троки транспортированной матрицы. Адрес первого выбираемого элемента в первом столбце матрицы определяется с входов 16 кодом модификации адреса. После того, как считан первый элемент на входах 16,выставляется код, соотве тс твукяций длине столбца преобразуемой матрицы, и следующие элементы строки транспортированной матриШ) получаются без изменения кода на входах 16. Подобным образом считываются и другие строки матрицы. Для преобразования форматов слов, например, по байтной записи, а считывания - по тетрадам или наоборот дос1таточно задавать код длины формата соответственно 6 и 4. Дпя выделения из каждого информациь онного слова заданной части на входах 17 устанавливается код длины выделяемой части. При последовательном считывании элементов выделяемой части на входах16 установлен код единицы, а по сигналу с выхода счетчика 10 устанавливается код, соответствующий объему невыделяемой части. Таким образом, предлагаемое устройство может работать со словами различной разрядности, осуществлять преобразоваиие формата слов, предварительную обработку массивов слов, что значительно расширяет область его использования в автоматизированных системах обработки данных. Эффективное использование объема накопителя уменьшает затраты на его изготовление и увеличивает надежность.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1249583A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1439681A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1084890A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1571679A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопитель, информационный вход которого подключен , к одному из выходов сдвйговето регистра, информационные выходы сдвигового регистра ябляются информационными выхода ми устройства, счетчик, элементы И, отличающееся тем, :что, с целью расширения области применения устройства за счет преобразования форма та данных, содержит блок элементов ИИЛИ, регистры, триггер, элемент. НЕ и сумматор, одни входы которого являются первой группой управляющих входов устройства, другие входы сумматора подключены к выходам блока элементов И-ИЛИ, информационные входы которого подклк чены к выходам первого и второго регистров, выходы сумматора подключены к } . информационным входам нак

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Буферное запоминающее устройство | 1979 |

|

SU822287A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авгорское свидетельство СССР № 758251, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-10-15—Публикация

1982-06-11—Подача