Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при построении оперативных запоминающих устройств (ОЗУ) с большой частотой выборки и записи информации, например ОЗУ, работающих в телевизионном режиме формирования изображения.

Известно запоминающее устройство, содержащее накопитель, счетчик адресов, элементы ИЛИ, через которые осуществляется коммутация адресов записи и считывания, счетчик разрядов, регистр, выходные элементы И, блок управления 1.

Недостатком этого устройства является снижение быстродействия с увеличением разрядности входной информации.

Наиболее близким к данному изобретению является запоминающее устройство, содержащее синхронизатор, соединенный с первым входом блока управления и счетным . входом счетчика адреса считывания, счетчик адреса записи, счетный вход которого, а также второй вход блока управления подключены к щине управления поэлементной записи, а выходы соединены с соответствующими входами блока управления и п коммутатора.ми адресации, подключенными также к выходам счетчика адреса считывания и к первому выходу блока управления, входные и выходные информационные , группы накопителей, каждая из которых содержит п накопителей, два п-разрядных сдвиговых регистра и коммутатор, причем входы записи накопителей соединены с соответствующими п выходами блока управления, адресные входы соединены с выходами соответствующих коммутаторов адресации, разрядные входы обоих регистров подключены к информационным выходам соответствующих накопителей, а первый и второй входы синхронизации подключены ко второму и третьему выходам блока управления,- информационные входы коммутатора подключены к выходам п-го разряда обоих регистров, два управляющих входа коммутатора, а также Входы выбора режима первого и второго регистров подключены к одному из выходов и инверсному выходу счетчика адреса считывания соответственно, а выхой коммутатора соединен с соответствующей выходной информационной щиной 2.

Недостатком данного устройства является низкое быстродействие в режи.аде записи, поскольку устройство не обеспечивает . запись информации с такой же скоростью, как осуществляется считывание, т. е. в телевизионном режиме формирования изображения. В данном устройстве для записи кадра изображения требуется значительно больще времени, чем время кадровой развертки.

Целью изобретения является повыщение быстродействия устройства в режиме записи.

Поставленная цель достигается тем, что

в запоминающее устройство, содержащее генератор тактовых импульсов, первый выход которого соединен со счетным входом счетчика адресов считывания, адресные выходы которого подключены к одним из вхо0 дов адресного блока, другие входы которого соединены свыходами счетчика адресов записи, блок управления, коммутаторы, группы сдвиговых регистров и группы нако пителей, адресные входы которых подклю5 чены к выходам адресного бока, причем управляющие входы первых сдвиговых регистров групп соединены с первыми унравляющи.ми входами коммутаторов и прямым управляющим выходом счетчика адресов считывания, инверсный управляющий выход

0 которого подключен к управляющим входам вторых сдвиговых регистров групп и вторым управляющим входам коммутаторов, информационные входы которых соединены с одними из выходов первого и вто5 рого сдвиговых регистров соответствующей группы, разрядные входы которых подключены к выходам накопителей однои.менной группы, одни из входов блока управления соединены соответственно со вторым выходом генератора тактовых импульсов, со вхо0 дом и с выходами счетчика адресов записи, одни из выходов блока управления подключены соответственно к управляющим входам адресного блока, к управляю. щим входам накопителей групп, к одним из входов синхронизации сдвиговых регист5 ров групп, информационные входы первого и второго сдвиговых регистров каждой группы объединены и являются инфор.мационными входами устройства, первым управляющим входом и информационными

0 выхода.ми которого являются соответственно вход счетчика адресов записи и выходы коммута10ров, введены элемент И, первый и второй триггеры, первые входы которых соединены с третьим выходом генератора тактовых импульсов, и группы ко.мму5 таоров, первые и вторые управляющие входы которые подключены соответственно к прямому и к инверсному управляющим выходам счетчика адресов считывапия, причем третьи управляющие входы всех коммуQ таторов соединены с управляющим входом адресного блока и первым входом элемента И, второй вход которого подключен к выходу второго триггера, другому входу блока управления и четвертым управляющим входам всех коммутаторов, выход первого

5 триггера соединен со вторым входом второго триггера, третий вход и выход элемента И подключены соответстве1пк) к другому выходу блока управления и к другим входам

синхронизации сдвиговых регистров групп, другие выходы сдвиговых регистров каждой группы соединены с информационными входами коммутаторов одноименной группы, .выходы которых подключены к информационным входам накопителей одноименной группы, кроме первого, информационный вход которого соединен с выходом соответствующего коммутатора, второй вход первого триггера является вторым управляющим входом устройства.

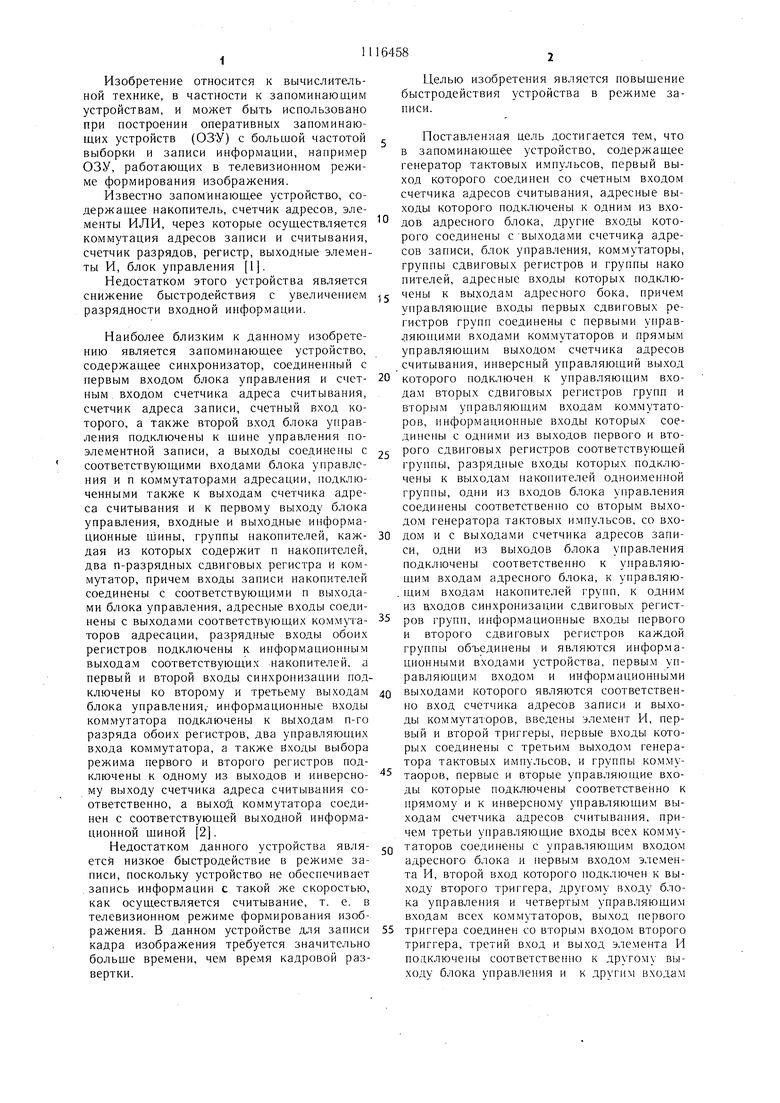

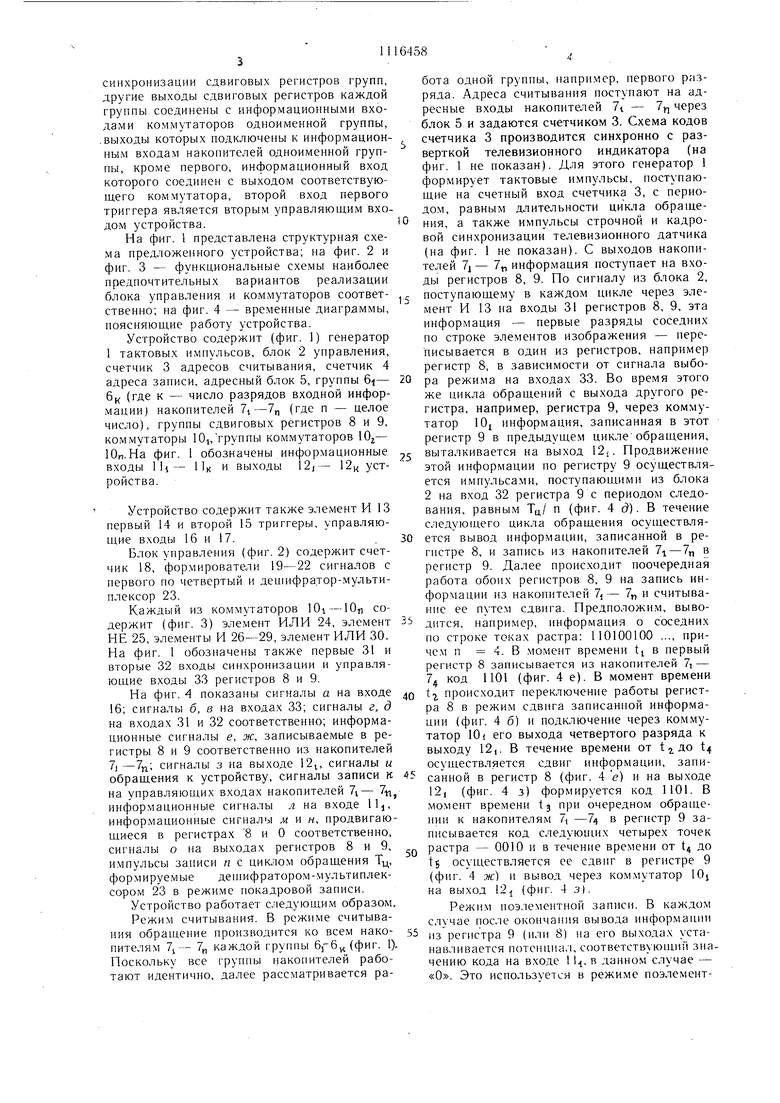

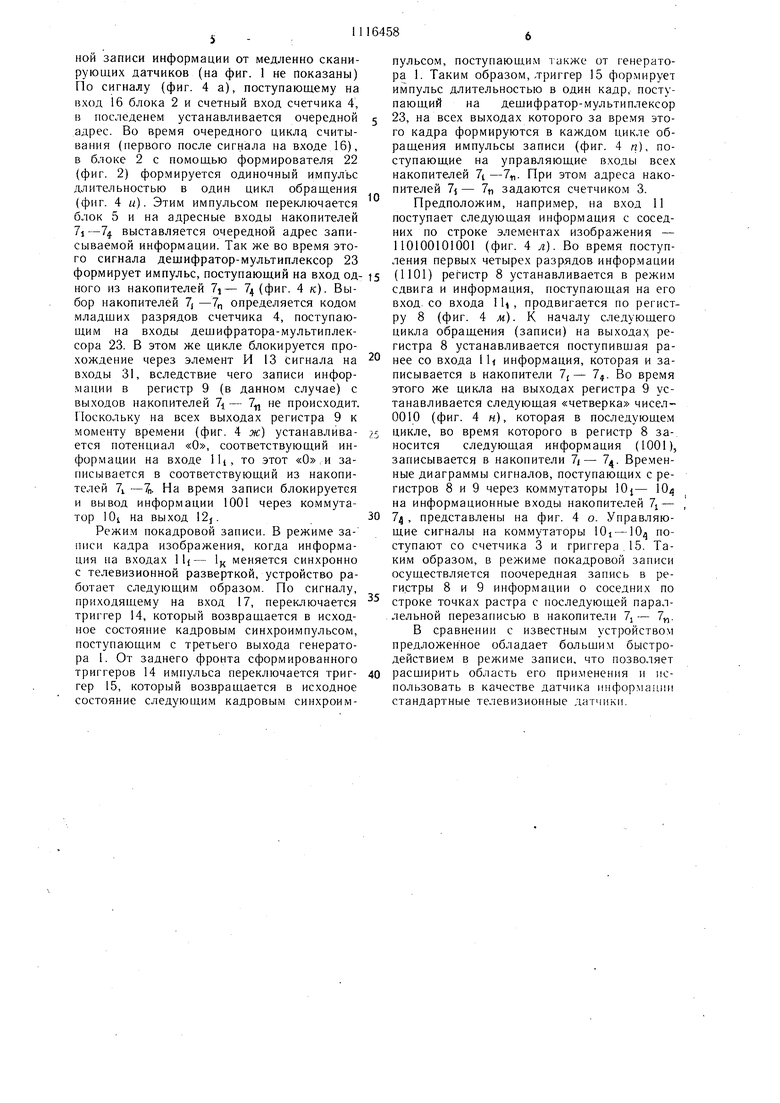

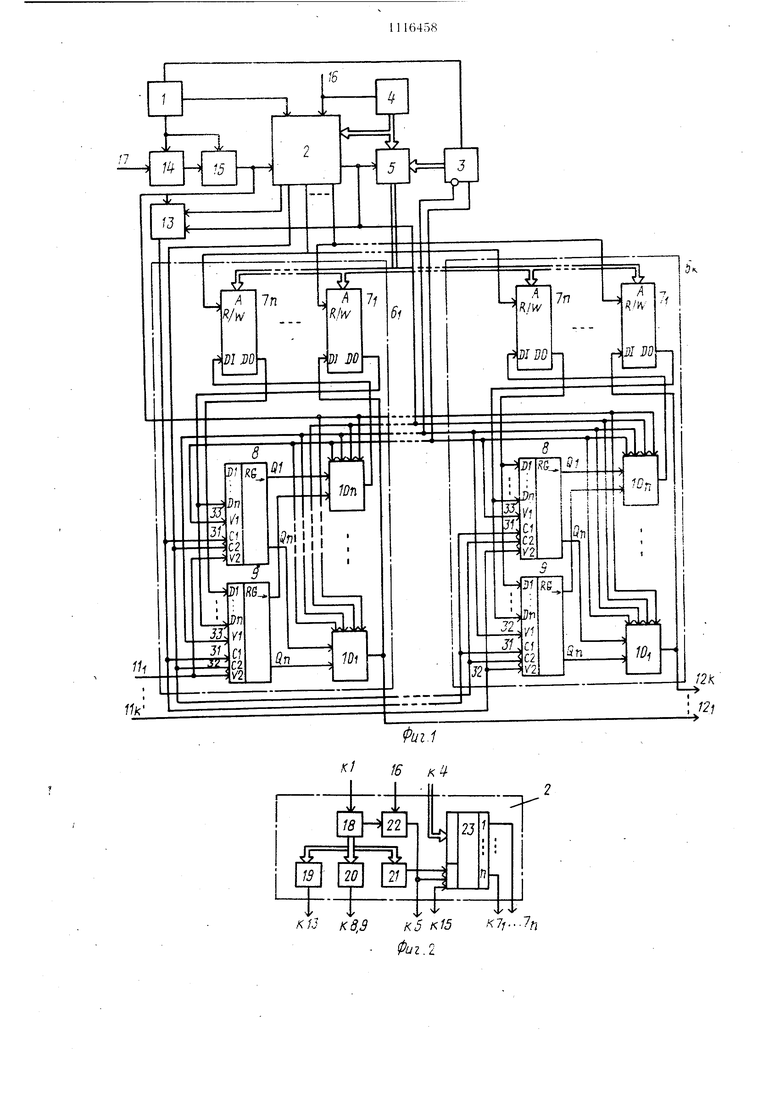

На фиг. 1 представлена структурная схема предложенного устройства; на фиг. 2 и фиг. 3 - функциональные схемы наиболее предпочтительных вариантов реализации блока управления и коммутаторов соответственно; па фиг. 4 - временные диаграммы, поясняющие работу устройства.

Устройство содержит (фиг. ) генератор 1 тактовых импульсов, блок 2 управления, счетчик 3 адресов считывания, счетчик 4 адреса записи, адресный блок 5, группы 6i- 6 (где к - число разрядов входной информации) накопителей 7t-7„ (где п - целое число), группы сдвиговых регистров 8 и 9, коммутаторы 10,группы коммутаторов Юп.На фиг. 1 обозначены информационные входы i- 11 и выходы 12j- 12 устройства.

Устройство содержит также элемент И 13 первый 14 и второй 15 триггеры, управляющие в.чоды 16 и 17..

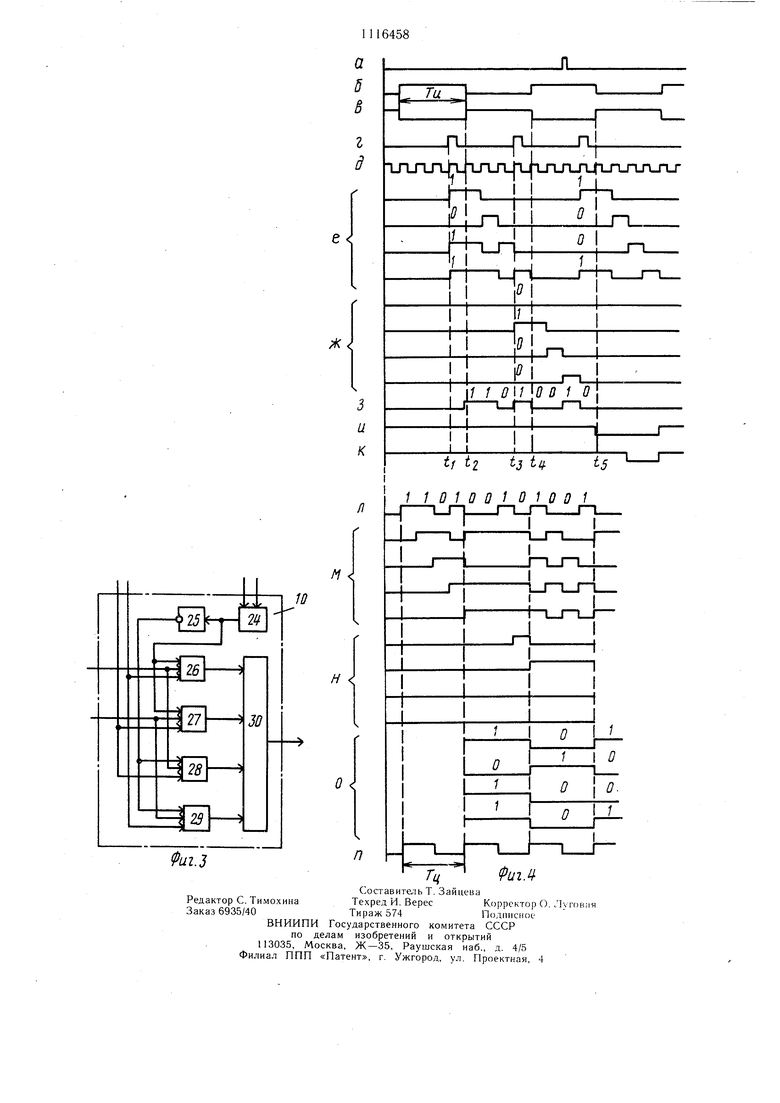

Блок управления (фиг. 2) содержит счетчик 18, формирователи 19-22 сигналов с первого по четвертый и дешифратор-мультиплексор 23.

Каждый из коммутаторов lOi -10 содержит (фиг. 3) элемент ИЛИ 24, элемент НЕ 25, элементы И 26-29, элемент ИЛИ 30. На фиг. 1 обозначены также первые 31 и вторые 32 входы синхронизации и управляющие входы 33 регистров 8 и 9.

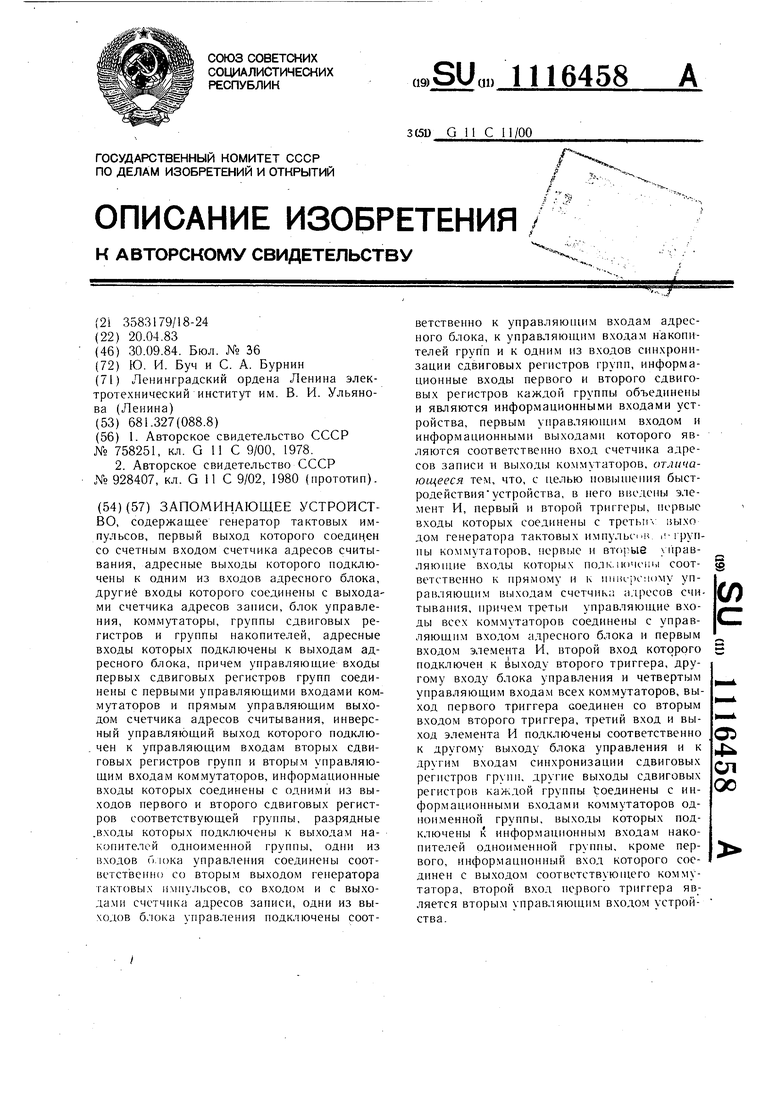

На фиг. 4 показаны сигналы а на входе 16; сигналы б, в на входах 33; сигналы г, д на входах 31 и 32 соответственно; информационные сигналы е, ж, записываемые в регистры 8 и 9 соответственно из накопителей сигналы з на выходе 12, сигналы и обращения к устройству, сигналы записи к на управляющих входах накопителей 7i- информационные сигналы л на входе 11, информационные сигналы м и к, продвигающиеся в регистрах 8 и О соответственно, сигналы о па выходах регистров 8 и 9,

Т

импульсы записи п с циклом ооращения 1ц, формируемые дешифратором-мультиплексором 23 в режиме покадровой записи.

Устройство работает следующим образом. Режим считывания. В режиме считывания обращение производится ко всем накопителям 7„ каждой группы 6)-6,(фиг. 1). Носкольку все группы накопителей работают идентично, далее рассматривается работа одной группы, папример, первого разряда. Адреса считывания поступают на адресные входы накопителей 7t - 7, через блок 5 и задаются счетчиком 3. Схема кодов счетчика 3 производится синхронно с разверткой телевизионного индикатора (на фиг. 1 не показан). Для этого генератор i формирует тактовые импульсы, поступающие на счетный вход счетчика 3, с периодом, равным длительности цикла обращения, а также импульсы строчной и кадровой синхронизации телевизионного датчика (на фиг. 1 не показан). С выходов накопителей 7j - 7„ информация поступает на в.ходы регистров 8, 9. По сигналу из блока 2, поступающему в каждом цикле через элемент И 13 на входы 31 регистров 8, 9, эта информация - первые разряды соседних по строке элементов изображения - переписывается в один из регистров, папример регистр 8, в зависимости от сигнала выбора режима на входах 33. Во время этого же цикла обращений с выхода другого регистра, например, регистра 9, через коммутатор lOj информация, записанная в этот регистр 9 в предыдущем циклеобращения, выталкивается на выход 12i. Продвижение этой информации по регистру 9 осуществляется импульсами, поступающими из блока 2 на вход 32 регистра 9с периодом следования, равным Тц/ п (фиг. 4 с). В течение следующего цикла обращения осуществляется вывод информации, записанной в регистре 8, и запись из накопителей в регистр 9. Далее проис.ходит поочередная работа обоих регистров 8, 9 на запись информации из накопителей 7i- 7„ и считывание ее путем сдвига. Предположим, выводится, папример, информация о соседних по строке токах растра: 110100100 ..., причем п 4. В момент времени ti в первый регистр 8 записывается из накопителей 7, - 7 код 1101 (фиг. 4 е). В момент времени t происходит переключение работы регистра 8 в режим сдвига записанной информации (фиг. 4 б) и подключение через коммутатор 10 ( его выхода четвертого разряда к выходу 12(. В течение времени от 12. до t4 осуществляется сдвиг информации, записанной в регистр 8 (фиг. 4 ) и на выходе 12, (фиг. 4 з) формируется код 1101. В момент времени i при очередном обращении к накопителям 7 -7 в регистр 9 записывается код следующих четырех точек растра - 0010 и в течение времени от t до ts осуществляется ее сдвиг в регистре 9 (фиг. 4 ж) и вывод через коммутатор lOj на выход 12 (фиг. 4 з).

Режим поэлементной записи. В каждом случае после окончания вывода информации из регистра 9 (или 8) на eiO выходах устанавливается потенциал, соответствуюп1ий значению кода на входе 1 . в данном случае - «О. Это используется в режиме поэ,аементной записи информации от медленно сканирующих датчиков (на фиг. 1 не показаны) По сигналу (фиг. 4 а), поступающему на вход 16 блока 2 и счетный вход счетчика 4, в последенем устанавливается очередной адрес. Во время очередного циклд считывания (первого после сигнала на входе 16), в блоке 2 с помощью формирователя 22 (фиг. 2) формируется одиночный импульс длительностью в один цикл обращения (фиг. 4 и). Этим импульсом переключается блок 5 и на адресные входы накопителей 7i-/4 выставляется очередной адрес записываемой информации. Так же во время этого сигнала дешифратор-мультиплексор 23 формирует импульс, поступающий на вход одкого из накопителей 7i- 7 (фиг. 4 к). Выбор накопителей 7, определяется кодом младших разрядов счетчика 4, поступающим на входы дещифратора-мультиплексора 23. В этом же цикле блокируется прохождение через элемент И 13 Сигнала на входы 31, вследствие чего записи информации в регистр 9 (в данном случае) с выходов накопителей 7 - 7 не происходит. Поскольку на всех выходах регистра 9 к моменту времени (фиг. 4 ж) устанавливается потенциал «О, соответствующий информации на входе lU, то этот «О, и записывается в соответствующий из накопителей 7х -7п. На время записи блокируется и вывод информации 1001 через коммутатор lOt на выход 12j. Режим покадровой записи. В режиме записи кадра изображения, когда информация на входах 1Ij- 1 меняется синхронно с телевизионной разверткой, устройство работает следующим образом. По сигналу, приходящему на вход 17, переключается триггер 14, который возвращается в исходное состояние кадровым синхроимпульсом, поступающим с третьего выхода генератора 1. От заднего фронта сформированного триггеров 14 импульса переключается триггер 15, который возвращается в исходное состояние следующи.м кадровым синхроимпульсом, поступающим также от генератора 1. Таким образом,-триггер 15 формирует импульс длительностью в один кадр, поступающий на дещифратор-мультиплексор 23, на всех выходах которого за время этого кадра формируются в каждом цикле обращения импульсы записи (фиг. 4 п), поступающие на управляющие входы всех накопителей 7i -7. При этом адреса накопителей 7i - 7t) задаются счетчиком 3. Предположим, например, на вход 11 поступает следующая информация с соседних по строке элементах изображения - 110100101001 (фиг. 4л). Во время поступления первых четырех разрядов информации (1101) регистр 8 устанавливается в режим сдвига и информация, поступающая на его вход, со входа 1 , продвигается по регистру 8 (фиг. 4 ж). К началу следующего цикла обращения (записи) на выходах регистра 8 устанавливается поступившая ранее со входа 111 информация, которая и записывается в накопители 7j- 74. Во время этого же цикла на выходах регистра 9 устанавливается следующая «четверка чисел0010 (фиг. 4 н), которая в последующем цикле, во время которого в регистр 8 заносится следующая информация (1001), записывается в накопители 7/- 7. Временные диаграммы сигналов, поступающих с регистров 8 и 9 через коммутаторы lOj- 10 на информационные входы накопителей , 7 , представлены на фиг. 4 о. Управляющие сигналы на коммутаторы lOj -10 поступают со счетчика 3 и григгера . 15. Таким образом, в режиме покадровой записи осуществляется поочередная запись в регистры 8 и 9 информации о соседних по строке точках растра с последующей параллельной перезаписью в накопители 7„. В сравнении с известным устройством предложенное обладает больщим быстродействием в режиме записи, что позволяет расщирить область его применения и использовать в качестве датчика информации стандартные телевизионные датчики.

К13 к8,3 к5 к15 Kii...ln фиг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции ошибок | 1987 |

|

SU1541677A1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1242968A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1084890A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Устройство для вывода графической информации | 1985 |

|

SU1339625A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее генератор тактовых импульсов, первый выход которого соединен со счетным входом счетчика адресов считывания, адресные выходы которого подключены к одним из входов адресного блока, другие входы которого соединены с выходами счетчика адресов записи, блок управления, коммутаторы, группы сдвиговых регистров и группы накопителей, адресные входы которых подключены к выходам адресного блока, причем управляющие входы первых сдвиговых регистров групп соединены с первыми управляющими входами коммутаторов и прямым управляющим выходом счетчика адресов считывания, инверсный управляющий выход которого подклю. чен к управляющим входам вторых сдвиговых регистров групп и вторым управляющим входам коммутаторов, информационные входы которых соединены с одни.ми из выходов первого и второго сдвиговых регистров соответствующей группы, разрядные .входы которых подключены к выходам накопителей одноиме.иной группы, одни из входов олсжа управления соединены соответственно со вторым выходом генератора тактовы.х и п1ульсов, со входом и с выходами счетчика адресов записи, одни из выходов блока управления подключены соответственно к управляющим входам адресного блока, к управляюогим входам накопителей групп и к одним из входов синхронизации сдвиговых регистров групп, информационные входы первого и второго сдвиговых регистров каждой группы объединены и являются информационными входами устройства, первым управляюпи1м входом и информационными выходами которого являются соответствешю вход счетчика адресов записи Т выходы коммутаторов, отличающееся тем, что, с целью 11овыц1е1тя быстродействияустройства, в пего введены элемент И, первый и второй триггеры, первые входы которых соединены с третыгч ныхо дом генератора тактовых импульсИ, г -группы коммутаторов, первые и вторые хиравI ляющие входы которых полк.мочсчи, соответственно к прямому и к 1И11К-|(.-:1()Му уПся равляющим выходам счетчика адресов считывания, причем третьи управляющие входы всех коммутаторов соединены с управляющим входом адресного блока и первым входом элемента И, второй вход которого подключен к выходу второго триггера, другому входу блока управления и четвертым управляющим входам всех коммутаторов, выход первого триггера соединен со вторым входом второго триггера, третий вход и вы05 ход элемента И подключены соответственно к другому выходу блока управления и к другим входам синхронизации сдвиговых 01 регистров групн, другие выходы сдвиговых 00 регистров каждой группы toeдинeны с информационными входами коммутаторов одноименной группы, выходы которых подключены к информационным входам накопителей одноименной группы, кроме первого, информационный вход которого соединен с выходом соответствующего коммутатора, второй вход первого триггера является вторым управляющим входом устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 758251, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство | 1980 |

|

SU928407A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-09-30—Публикация

1983-04-20—Подача