(54) ЗАПОМИ АЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2037892C1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| Ассоциативное запоминающее устройство | 1991 |

|

SU1833917A1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Запоминающее устройство | 1981 |

|

SU1010654A1 |

Изобретение относится к запоминакмцим устройствам и может быть исполь зовано для создания больших интеграл ных схем запоминающих устройств с произвольной.выборкой, имеющих большую площадь кристалла. Известны запоминаннщие устройства О и 2. Одно из известных устройств содержит матрицу элементов памяти и схемы логики обрамления, позволяющие производить обращение при записи и считывании информации- ТОЛБКО к одному любому элементу памяти матрицы tl. Недостатком этого устройства является низкая надежность. Наиболее б.гшзким техническим решением к предлагаемому является запоминающее устройство, содержащее Д . шифратор адреса слова, соединенный с адресными шинами матрицы элементо памяти, разрядные шины которой соед нены с выходами первых вентилей и информационными входами первого блока считывания, управляющие входы которого подключены к выходам дешифратора адреса разряда и к первым вxoдa первых вентилей, вторые входы которых соединены с шиной записи, вторыми входами вторых венти:тей, входами J, К и R JК-триггера и первым входом сумматора по модулю два, третьи входы с шиной управления, третьими входами вторых вентилей, входами дешифратора адреса слова и разряда, первым входом выходного блока, четвертые входы с выходом первого элемента И, первым входом соединенного с шиной разрешения записи и управляющим (счетным) входом JK-триггера, первые входы вторых вентилей соединены с выходами вторых элементов И дешифратора обращения к- дополнительным элементам памяти и с управляющими входами второго блока считывания, информационные входы второ.го блока считывания соединены с разрядными шипами дополнительных элемен3тов памяти и выходами вторых вентилей выход первого блока считывания соединен с вторым входом сумматора по модулю два Г21. Недостатком этого устройства явля- атся низкое быстродействие при коррекции двух и более дефектных элементов памяти из-за большой задержки сигнала в элементах коррекции и необходимости отключать дефектнь1е элементы памяти от разрядных шин, Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем что в запоминающее устройство, содер жащее первый накопитель матричного ти па, вьтолненный на триггерных запомин ющих элементах, дешифраторы, блоки считывания, сумматор по модулю два, первый триггер, группы элементов И, элементы И и выходной блок, причем вхо ды запоминающих элементов строк первого накопителя соединены соответственно с выходами первого дешифратора, прямые выходы запомиианяцих элементов столбцов первого накопителя подключены соответственно к информационным входам блоков считывания и выходам элементов И первой и второй групп, а инверсные выходы к инверсным входам элементов И8перво и второй групп, счетный вход первого триггера является первым управляющим входом устройства и соединен с прямым входом первого и инверсным входом второго элементов И, выход первого элемента И подключен к первым входам элементов И первойтруппы, вызгоды элементов И третьей группы соединены соответственно с первыми входами элементов И второй группы и управляющими входами второго блока считывания, выход первого блока считывания подключен к первому входу сум матора по модулю два , вторЪй вход которого является :информационным вхо дом устройства и соединен с J, К и R входами первого триггера и вторыми входами элементов И первой и вгорой групп, третьи входы которьтх подключены к первому входу выходного блока входам дешифраторов и являются вторы управляющим входом устройства, а выход выходного блока является выходом устройс- аа, введены второй и тре тий накопитеЛи матричного типа, выпо

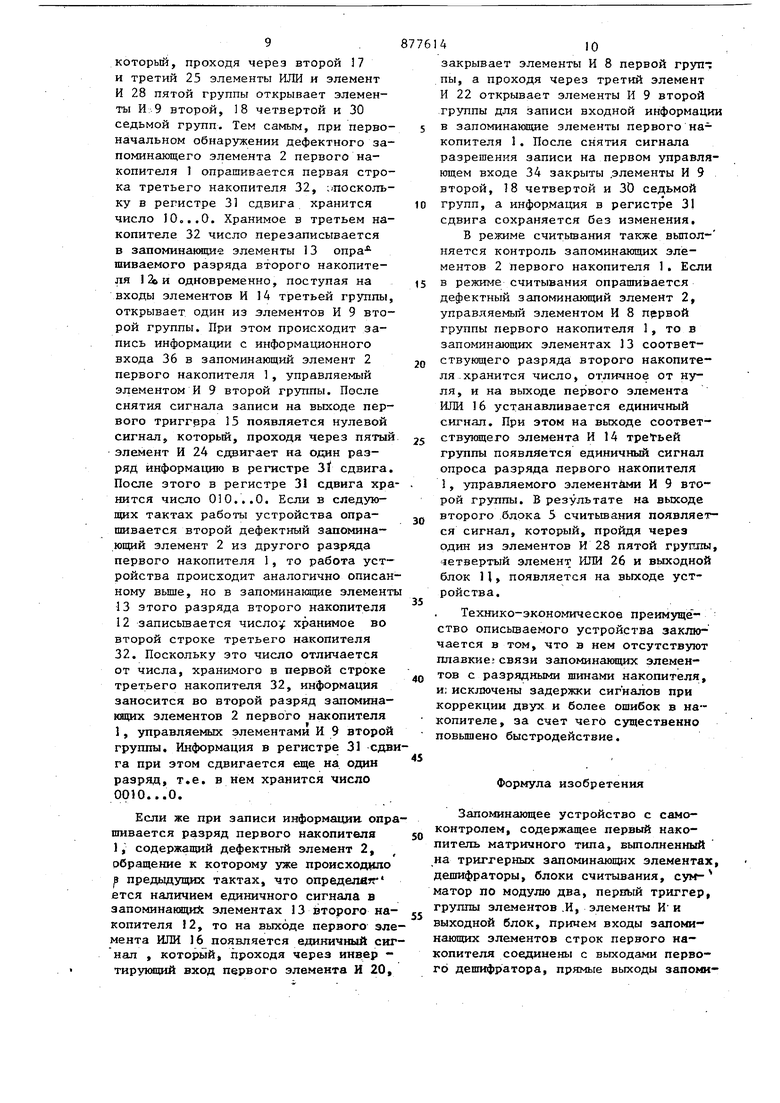

ненные на.триггерных запоминающих элементах, второй триггер, регистр сдвига, элементы ИЛИ, третий, четвермые входы элементов И пятой группы соединены соответственно с выходами первого и второго блоков считывания. 4 тый и пятьш элементы И, четвертую, пятую, шестую и седьмую группы элементов И, причем входы запоминающих элементов столбцов второго накопителя подключены соответственно к выходам второго дешифратора, прямые входысоответственно ко входам первого элемента ИЛИ, входам элементов И третьей и выходам элементов И четвертой группы, а инверсные выходы запоминающих элементов столбцов второго накопителя - соответственно к инверсным входам элементов И четвертой группы, выход второго триггера соединен с прямым входом второго элемента И, в установочный вход - с выходом первого элемента ИЛИ, первым входом третьего элемента И и инверсными входами элементов И пятой группы, счетный вход второго триггера подключен к прямому входу первого элемента И и второму входу третьего элемента И выход которого соединен с первым входом второго элемента ИЛИ, выход которого подключен к четвертым входам элементов И второй группы, а второй вход - к выходу четвертого и первому входу пятого элементов И и первому входу третьего элемента ИЛИ, первый и второй прямые входы четвертого Элемента И соединены соответственно с выходами первого триггера и сумматора по модулю два, а инверсный входс выходом второго элемента И, установочный вход регистра сдвига подклют; чей к первым входам элементов И щестой группы, инверсному входу третьего элемента ИЛИ, второму входу пятого элемента И и является установочным входом устройства, выход третьего элемента ИЛИ подключен к первым входам элементов И четвертой группы, вторые входы которых соединены соответственно с выходами элементов И шестой труппы, выход пятого элемента И подключен к счетному входу регистра сдвига и первым входам элементов И седьмой группы, вторые вхо;ц 1 .которых соединены с выходами регистра сдвига соответственно, а входы - соответственно со счетными входами запоминакшщх элементов строк третьего накопителя, выходы запоминайзщиж элементов столбцов которого подключены соответственно ко вторым входам элементов И шестой группы, пряа выходы - со входами четвертого эле мента ИЛИ, выход которого подключен ко второму входу выходного блока. На чертеже изображена структурная схема предлагаемого устройства. Устройство содержит первый накопитель 1 матричного типа, выполненны на триггерньк запоминающих элементах 2, первый дешифратор 3, являющийся дешифратором адреса слова, первый 4 и второй 5 блоки считывания с информ ционными 6 и управляющими 7 входами, первую 8 и вторую 9 группы элементов И, второй дешифратор 10, выходной блок « 1 , второй накопитель 12, вьшол ненный на триггерных запоминакяцих элементах 13, третью группу элементо И 14, выполняющих функции дешифратора обращения, первый триггер 15, первый 16 и второй 17 элементы ИЛИ, четвертую группу элементов И 18, вто рой триггер 19. первый 20, второй 21, третий 22, четвертый 23 и пятый 24 элементы И, третий 25 и четвертый 26 элементы ИЛИ, сумматор 27 по модулю два, пятую 28, шестую 29 и сед мую 30 группы элементов И, регистр 31 сдвига, третий накопитель 32, выполненный на триггерных запоминающих элементах 33, первый 34 и второй 35 Заправляющие, информационный 36 и ус,тановочный 37 входы. Первый триггер 15 является JK-триг гером, а второй триггер 19 RS-триггером. Входы запоминающих элементов 2 строк первого накопителя 1 соединены соответственно с выходами первого дешифратора 3, Прямые выходы заломинанщих элементов 2 столбцов первого накопителя 1 подключены соответственно к информационным входам 6 первого 4 и второго 5 блоков считьшания и выходам элементов И пер вой 8 и второй 9 Групп, а инверсные выходы - к инверсным входам элементов И 8 первой и 9 второй групп. Сче ньш вход первого триггера 15 является первым управляющим входом 34 устройства и соединен с прямым входом первого 20 и инверсным входом второго 21 элементов И. Выход первого элемента И 20 подключен к первым входам элементов И первой группы в. Выходы элементов И третьей группы 14 соединены соответственно с первьгми входами элементов И второй группы 9 и управлянядимн входами второго блока 5 считывания. Выход первого блока 4 считывания подключен к первому входу сумматора 27 по модулю два, второй вход которого является информационным входом 36 устройства и соединен с J, К и R входами первого триггера 15 и вторыми входами элементов И первой В и второй 9 групп, третьи входы которых подключены к первому входу выходного блока I1, входам первого 3 и второго 10 дешифраторов и являются вторым управляющим входом 35 устройства. Входы запоминающих элементов 13 столбцов второго накопителя 12 подключены соответственно к выходам второго дешифратора 10, прямые выходы - соответственно ко вхрдам первого элемента ИЛИ 16, входам элементов И 14 третьей группы и выходам элементов И 18 четвертой группы. Инверсные выходы запоминающих элементов 13 столбцов второго накопителя 12 подключены соответственно к инверсным входам элементов И 18 четвертой группы, -Выход второго триг гера J 9 соединен с прямым входом второго элемента И 21, а установочный вход - с выходом первого элемента ИЛИ 16, первым входом третьего элемента И 22 и инверсными входами элементов И 28 пятой/группы. Счетный вход второго триггера 19 подключен к прямому входу первого элемента И 20 и второму входу третьего элемента И 22, выход которого соединен с первым входом второго элемента ИЛИ 17. Выход второго элемента ИЛИ 17 подключен к четвертым входам элементов И 9 второй группы, а второй входк выходу четвертого 23 и первому входу пятого 24 элементов И и первому входу третьего элемента ИЛИ 25.- Первый и второй прямые входы четвертого элемента И 23 соединены соответственно с выходами первого триггера 15 и сумматора 27 по модулю два, инверсный вход - с выходом второго элемента И 21. Установочный вход регистра 31 сдвига подключен к первым входам элементов И 29 шестой группы, инверсному входу третьего элемейта ИЛИ 25, второму входу пятого элемента И 24 и является установоч- ным входом 37 устройства. Выход третьего элемента ИЛИ 25 подключен к первым входам элементов И 18 четвертой группы, вторые входы которых соединены соответственно с выходами элементов И 29 шеетой.группы. Выход пятого элемента И 24 подключен к счетиому входу регистра 31 сдвиге 7 и первым входам элементов И 30 седьмой группы, вторые входы которых соединеггы с выходами регистра 3 сдвига, соответственно, а входы соответственно со счетными входами запоминающих элементов 33 строк третьего накопителя 32, выходы запомина ющих элементов 33 столбцов которого подключены соответственно к вторым входам элементов И 29 шестой группы. Вторые входы элементов И 28 пятой группы соединены соответственно с выходами первого 4 и второго 5 блоков считьшания, а выходы - со входам четвертого элемента ИЛИ 26,- вьгход которого подключен ко второму входу выходного блока Г, Количество строк (слов 0 третьем накопителе 32 и разрядность регистра 31 сдвига равны количеству исправ ляемых разрядов накопителя 1, предус мотренному при создании устройства. Количество слов во втором накопителе 12 и разрядов (столбцов в третьем н копителе 32 равны (r+l), Устройство работает следующим образом, В исходном состоянии все запоминающие элементы 13 второго накопителя 12устанавливаются в нулевое состояние нулевым сигналом, с установочного входа 37 через элементы И 29 шестой группы. При этом единичный си нал на выходе третьего элемента, ИЛИ держит открытым элементы И. J8 четвер той группы, а регистр 31 сдвига по установочному входу заносится информ ция 10...0. При изготовлении в запоминающие элементы 33 третьего накопителя заносится постоянная информация в зависимости от числа исправляемых разрядов первого накопителя 1, При записи информации на информационные входы 36 устройства подаются сигналы записи, а на первый 34 и вто рой 35 управляющие входы - сигналы разрешения и управления. При этом происходит возбуждение выходов первого 3 и второго Ю дешифраторов в соответствии с кодом адреса, ВозЗужденный выход первого дешифратора 3 подключает запоминающие элементы 2 первого накопителя 1 выбранного слова к информационным входам б блоков 4 и. 5 считывания, а возбужденный выход второго дешифратора 10 подключает запоминающие элЕменты 13выбранного разряда второго накопителя 32 к первому элементу ИЛИ 16 4 и входам элементов И I4 третьей группы. При этом, если опрашивается разряд первого накопителя I, где S предыдущих тактах работы не было дефектных запоминающих элементов 2, то в запоминающих элементах 13 второго накопителя )2 хранится число 0...0. Тогда на выходе первого элемента ИЛИ 16 находится нулевой сигнал, который записывается для хранения во второй триггер 19, устанавливает на выходе третьего элемента И 22 нулевой сигнал и открывает первый элемент И 20. При этом сигнал разрешения записи на первом управляющем входе 34 открывает элементы И 8 первой группы для записи входной информации в запоминающий элемент 2 первого накопителя J, находящийся на пересечении выбранного слова (строки) и разряда (столбца). В то же время нулевой сигнал с выхода первого триггера 15 поступает через четвертый элемент И 23 на-второй вход второго элемента ИЛИ 17, на выходе которого будет йулевой сигнал, удерживанядий элемент И второй группы 9 в закрытом состоянии. При.снятии сигнала разрешения записи, запись информации в перый накопитель J прекращается и лроисходит контрольное считывание записанной информации с зыбраннаго запоминающего элемента 2 первого накопителя 1 и сравнение ее на сумматоре 27 по модулю два с входной информацией, пост шающей с информационного входа 36, Наряду с этим, при снятии сигнала |)азрешения записи на выходе первого триггера 15 появляется единичный сигнал, который открьшает четвертый элемент И 23, Тогда, если опрашивается исправный запоминающий элемент 2 первого накопителя 1, на выходе сумматора по модулю два 27 и. выхода четвертого элемента И 23 будет нулевой сигнал, который закрывает элементы И 18 четвертой группы и 30 седьмой К сдвигу ингруппы, но не приводит сдвига. На выформации в регистре 31 ходе второго элемента ИЛИ 17 устанавливается нулевой сигнал, удерживающий элементы И 9 второй группы в закрытом состоянии, В случав, если опрашивается дефектный запоминающий элемент 2, на выходе сумматора 27 по модулю два и выходе четвертого элЕнента И 23 появляется единичный сигнал. 9. который, проходя через второй 37 и третий 25 элементы ИЛИ и элемент И 28 пятой группы открывает элементы И 9 второй, 18 четвертой и 30 седьмой групп. Тем самьм, при первоначальном обнаружении дефектного запоминающего элемента 2 первого накопителя 1 опрашивается первая строка третьего накопителя 32, ; посколъку а регистре 31 сдвига хранится число 10...0. Хранимое в третьем накопителе 32 число перезаписывается в запоминакнцие элементы 13 опрашиваемого разряда второго накопителя 2би одновременно, поступая на входы элементов И 14 третьей группы открывает один из элементов И 9 второй группы. При этом происходит запись информации с информационного входа 36 в запоминающий элемент 2 первого накопителя , управляемый элементом И 9 второй группы. После снятия сигнала записи на выходе первого триггера 15 появляется нулевой сигнал, который, проходя через пятый элемент И 24 сдвигает на один разряд информацию в регистре 3t сдвига После этого в регистре 31 сдвига хра нится число 010...0. Если в следующих тактах работы устройства опрашивается второй дефектный запоминающий элемент 2 из другого разряда первого накопителя 1, то работа уст- ройства происходит аналогично описан ному выше, но в запоминающие элемент 13 этого разряда второго накопителя 12 записьшается число : хранимое во второй строке третьего накопителя 32. Поскольку это число отличается от числа, хранимого в первой строке третьего накопителя 32, информация заносится во второй разряд запоминающих элементов 2 первого накопителя 1, управляемых элементами И 9 второй группы. Информация в регистре 31 сдв га при этом сдвигается еще иа один разряд, . в нем хранится число 0010...0. Если же при записи информации опр шивается разряд первого накопителя 1, содержащий дефектный элемент 2, обращение к которому уже происходило р предыдущих тактах, что определв г ется наличием единичного сигнала в запоминающий элементах 13 второго на копителя 12, то на выходе первого эл мента ИЛИ 16 появляется единичный си нал , который, проходя через вивер тирукшщй вход первого элемеита И 20, 10 закрывает элементы И В первой груп пы, а проходя через третий элемент И 22 открывает элементы И 9 второй группы для записи входной информации в запоминакядие элементы первого накопителя 1. После снятия сигнала разрешения записи на первом управляющем входе 34 закрыты .элементы И 9 второй, 18 четвертой и 3D седьмой групп, а информация в регистре 31 сдвига сохраняется без изменения. В режиме считьшания также выполняется контроль запоминающих элементов 2 первого накопителя 1. Если в режиме считывания опрашивается дефектный запоминающий элемент 2, управляемый элементом И 8 первой группы первого накопителя 1, то в запоминающих элементах 13 соответствующего разряда второго накопителя, хранится число, отличное от нуля, и на выходе первого элемента ИЛИ 16 устанавливается единичный сигнал. При этом на выходе соответствукнцего элемента И 14 трегьей группы появляется единичный сигнал опроса разряда первого накопителя 1, управляемого элементами И 9 второй грулпы. В результате на вьпсоде второго блока 5 считьтания появляетгся сигнал, который, пройдя через один из элементов И 28 пятой группы, четвертый элемент ИЛИ 26 и выходной блок 1I, появляется на выходе устройства. Технико-экономическое преимущество описьшаемого устройства заключается в том, что в нем отсутствуют плавкие- связи запоминающих элементов с разрядными шинами накопителя, и; исключены задержки сигналов при коррекции двух и более ошибок в наопителе, за счет чего существенно повьшено быстродействие. Формула изобретения Запоминающее устройство с самоонтролем, содержащее первый накоитель матричного типа, выполненный а триггерных запоминающих элементах, ешифраторы, блоки считывания, сум- атор по модулю два, первый триггер, руппы элементов ,И, элементы И и ыходной блок, причем входы запомиающих элементов строк первого иаопителя соединены с выходами первоо дешифратора, прямые выходы запоминающих элементов столбцов первого накопителя подключены соответственно к информационным входам блоков считывания и выходам элементов И первой и второй групп, а инверсные выходы - к инверсным входам элементов И первой и второй групп, счетный вход первого триггера является первым управляющим входом устройства и соединен с входом первого и инверсным входом второго элементов И, выход первого элемента И подключен к первым входам элементов И первой группы, выходы элементов И третьей rpjmпы соединены соответственно с первыми входами элементов И второй группы и управляющими входами второго блока считывания, выход первого блока считывания подключен к первому входу сумматора по модулю два, второй вход которого является информационным входом устройства и соединен с J, К и R входами первого триггера и вторыми входами элементов И первой и второй групп, третьи входы которых подключены к первому входу выходного блока, входам дешифраторов и являются вторым управлякнцим входом устройства, выход выходного блока является выходом устройства, отличающееся тем, то, с целью повышения быстродействия устройства, оно содержит второй и. третий накопители матричного типа, выполненные на триггерных запоминающих элементах, второй триггер, регистр сдвига, элементы ИЛИ, третий, четвертый и пятый элементы И, четвертую, пятую, шестую и седьмую груп пы элементов И, причем входы запоминающих элементов столбцов второго накопителя подключены соответственно к выходам второго дешифратора, прямые входы - соответственно ко входам первого элемента ШШ, входам Элементов И третьей группы и; выходам элементов И четвертой группы, а инверсные выходы запоминающих элементов столбцов второго накопителя соответственно к инверсным входам элементов И четвертой группы, выход второго триггера соединен с прямым входом второго элемента И, а установочный вход - с выходом первого элемента ШШ, первым входом третьего элемента И и инверсными входами элементов И пятой группы, счетный вход второго триггера подключен к прямому входу первого элемента И и второму входу третьего элемента И, вход которого соединен с первым входом второго элемента ИЛИ, выход которого подключен к четвертым входам элементов И второй группы, а второй вход к выходу четвертого и первому входу пятого элементов И и первому входу третьего эле1М.ента ИЛИ, первый и прямые входы четвертого элемента И

соединены соответственно с выходами первого триггера и сумматора по модулю два, а инверсный вход - с выходом второго элемента И, установочный вход регистра сдвига подключен к

первым входам элементов И шестой группы, инверсному входу третьего эле- о мента ИЛИ, второму входу пятого элемента И и является устаиовочньм входом устройства, выход третьего элемента ИЛИ подключен к первым входам элементов И четвертой группы, вторые входы которых соединены соответствен но с выходами элементов И шестой группи, выход пятого элемента И подключен

к счетному входу регистра сдвига Q первым входам элементов И седьмой группы, вторые входы которых соединены с выходами регистра сдвига, соответственно, а входы - соответственно со счетными входами запоминающих элементов строк третьего накопителя, выходы запоминающих элементов столбцов которого подключены соответственно ко вторым входам элементов И шестой группы, прямые входы элементов И пятой группы сойдинены соответственно с выходами первого и второго,блоков считывания, а выходы - со входами четвертого элемента ИЖ, выход которого подключен ко второму входу выходного блока.

Источники информации, принятые во внимание лри экспертизе :1. Микроэлектроника. Сб. статей под ред. Ф.А,Лукина. Сов. радио,

вьш„ 5, 1972, с. 123-150.

2, Авторское свидетельство СССР 649044, кл. G 1 С 29/00, 1975 (прототип).

Авторы

Даты

1981-10-30—Публикация

1980-02-15—Подача