Изобретение относится к запоминающим устройствам.

Известно устройство для контроля оперативной памяти, содержащее блок пуска-останова, связанный с блоком формирования адресов, соединенным с блоком формирования чисел и с имитатором ввода конечного адреса, блок контроля информации, связанный с блоком формирования чисел, и блок управления l .

Недостатком устройства является низкая надежность.

Наиболее близким по технической сущности к- предлагаемому является устройство для контроля оперативной памяти, содержащее формирователь адресных сигналов, соединенный с схемой сравнения адресов, подключенный к имитатору ввода конечного адреса и формирователю числовых сигналов, соединенному с схемой сравнения числа, счетчик, подсоединенный к дешифратору, триггер, блок управления, соединенный с счетчиком, дешифратором, триггером, с формирователем числовых сигналов,.с схемой сравнения числа и адреса, с формирователем адресных сигналов, подсоединенным к имитатору ввода начального адреса.

две схемы И, подключенные к схеме сравнения числа и схеме ИЛИ, соединенной с блоком пуска-останова 2.

Недостатком этого устройства является низкая надежность, поскольку оно не позволяет выявить взаимное влияние ячеек памяти в накопителях, построенных на .чнамических элементах памяти.

10

Цель изобретения - повыиение надежности устройства.

Поставленная цель достигается тем, что в устройство для контроля оперативной пс1мяти, содержащее фор15мирователь адресных сигналов, схемы сравнения,-формирователь числовых сигналов, блок управления, первый счетчик, первый триггер, первый дешифратор, элементы И, первый элемент

20 ИЛИ, первый блок местного управления, блок ввода начального адреса, которого подключен к nepBOMi входу формирователя адресных сигналов, и блок ввода конечного адреса,

25 выход которого соединен с первым входом первой схемы сравнения, первый выход и второй и третий входы которой подключены соответственно к первому входу блока управления и

30 к первому и второму выходам формирователя адресньзх сигналов, второй вход KOTopoio соединен с первым выходом блока управления, второй выход последнего под7слючен к первому входу первого счетчика, выходы которого соединен с входами первого дешифратора , первьнЧ выход последнего со. единен с вторым входом блока управления, третий вход н третий выход ко7;орого подключены к первому выходу и первому входу первого триггера, четвертый вккод блока управления .соединен с перв1- 1 входом формирователя числовых сигналов, первый втлход которого подключен к первому входу второй cxeNBd сравнения, выход последней ,соединен с первыми входами первого и второго элементов И, выход первого элемента И соединен с первым , входом первого элемента ИЛИ, выход которого подключен к входу первого блока местного управления, второй вход второй схемы сравнения соединен с пятым выходом блока управления, ; а третий вход является входом устройства, ввелеиы второй блок местного управления, коммутатор тестовых сигналов, второй элемент ИЛИ, третий , чехвертай и пятый элементы И и регистр адреса, первый вход которого соединен с выходом второго элемента ИЛИ, а второй вход и выход подключены соответственно к первому выходу и к третьему входу формирова теля адресных сигналов, четвертый, пятый и шестой входы и третий выход которого соединены соответственно с шестг:11М|, седьмым и четвертым выходами и с четвертым входом блока управления, пятый вход которого подключен

S

к второму выходу первого дешифратора и первого/ входу третьего элемента И, второй вход которого соединен с пятым выходом блока управления, а выход - с седьмым входом формирователя адресных сигналов, четвертый выход которого подключен к шестому входу блока управления и второму входу формирователя числовых сигналов, третий и четвертый входы которого соединены соответственно с восьмым и пятым выходами блока управления, седьмой вход .которого подключен

к первому внходу коммутатора тестовых сигналов и пятому входу формирователя числовых сигналов, шестой вход которого соединен с восьмым входом блока управления и вторым выходом коммутатора тестовых сигна™ лов, третий выход которого подключен к первому входу второго элемента ИЛ.И, второй вход последнего соединен с В53ХОДОН четвертого элемента И, первый вход которого подключен к девятому выходу блока управления к первому входу кo яwтaтopa тестовых сигналов, второй вход и

четвертый, пятый и шестой выходы которого соединены соответственно; с десятым выходоми девятым ,десятым и одиннадцатым входами блока управления, третий и четвертый входы KOMf siтатора тестовых сигналов подключены соответственно к пятому выходу блока управления и первому входу второго блока местного управления и к восьмому выходу блока управления и второму входувторого блока местного управления, третий вход и первый выход которого соединены соответственно с одиннадцатым выходом блока управления и с вторым входом четвертого элемента И и двенадцатым входом блока управления, двенадцатой выход которого подключен к второму входу первого счетчика, третий и четвертый входы которого соединены соответствено с третьим выходом блока управления .и с вторым выходом второго блока местного управления, третий и чет,вертый выходы которого подключены. соответственно к вторым входам первого и второго элементов И, а пятый и шестой выходы - соответственно к седьмому и к в.осьмому входам формирователя числовых сигналов, девятый вход которого соединен с вторым выходом первой схемы сравнения., выход второго элемента И соединен с вторым входом первого элемента ИЛИ, седьмой, восьмой и девятый выходы BOioporo блока местного управления подключены соответственно к тринадцатому и четырнадцатому входам блока управления и к пятнадцатому входу блока управления и первому входу пятого элемента И, второй вход которого соединен с тринадцатым выходом блока управления, а выход - с вторым входом первого триггера, второй выход которого подключен к шестнадцатому входу блока управления, семнадцатый вход которого соединен с выходом первого блока местного управления, а четырнадцатый выход является выходом устройства.

Второй блок местного управления содержит второй счетчик, второй де-j шифратор, второй триггер, третий, четвертый и пятый элемент ИДИ, элемент НЕи шестой,седьмой и восьмой элементы И, причем первые входы шестого и седьмого элементов И и второй счетчик являются соответственно первым, -вторым и третьим входами блока,выход шестого элемента И подключен к второму входу второго счетчика, выходы которого соединены с входами второго дешифратора, первый и второй выходы которого подключены соответственно к вторым входам .шестого и седьмого и элементов И и к первому входу восьмого элемента 5 И, второй вход которого соединен с

первым входом седьмого элемента И, выходы седьмого и восьмого элементов И подключены соответственно к входам второго триггера, третий и четвертый выходы второго дешифратора соединены соответственно с первыми входами третьего, четвертого и соответственно пятого элементов ИЛЦ и с вторыми входами третьего и четвертого элементов ИЛИ, выход третьего элемента ИЛИ подключен к входу элемента НЕ, первый выход второго дешифратора является первым выходом блока и соединен с третьим входом четвертого элемента ИЛИ, выход седьмого элемента И, второй и третий выходы второго дешифратора и выход пятого элемента ИЛИ являются соответственно вторым, третьим, четвертым и пятым выходами блока, выход второго триггера является шестым выходом блока и соединен с вторым входом пятого элемента ИЛИ, выходы элемента НЕ и четвертого элемента ИЛИ являются соответственно седьмым и восьмым выходами блока.

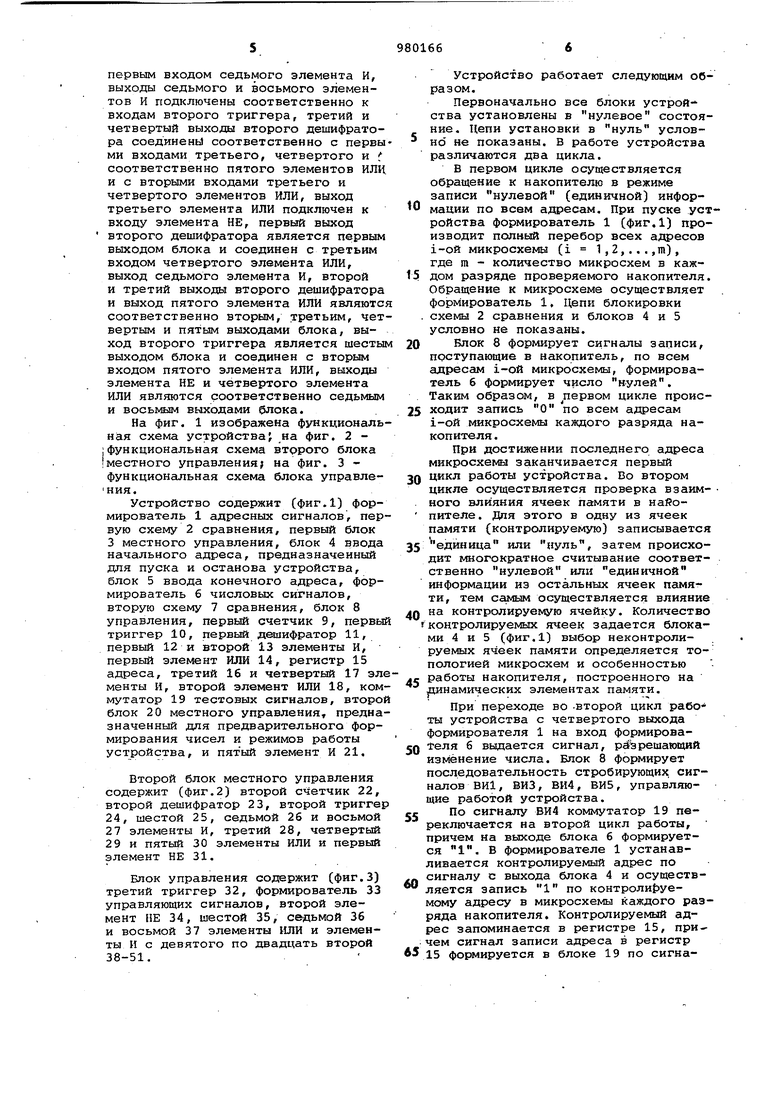

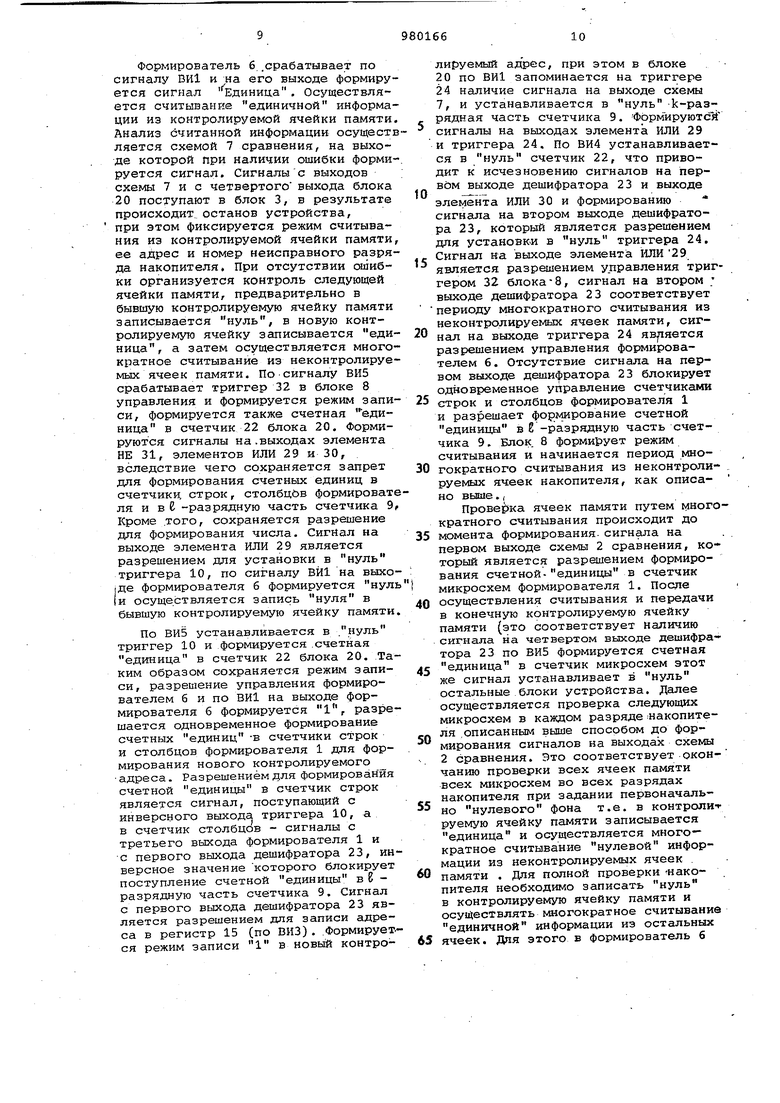

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 :функциональная схема второго блока местного управления; на фиг. 3 функциональная схема блока управлеНИЯ.

Устройство содержит (фиг.1) формирователь 1 адресных сигналов, первую схему 2 сравнения, первый блок 3 местного управления, блок 4 ввода начального адреса, предназначенный для пуска и останова устройства, блок 5 ввода конечного адреса, формирователь б числовых сигналов, вторую схему 7 сравнения, блок 8 управления, первый счетчик 9, первый триггер 10, первый дешифратор 11, первый 12 и второй 13 элементы И, первый элемент ИЛИ 14, регистр 15 адреса, третий 16 и четвертый 17 элементы И, второй элемент ИЛИ 18, коммутатор 19 тестовых сигналов, второй блок 20 местного управления предназначенный для предварительного формирования чисел и режимов работы устройства, и пятый элемент И 21.

Второй блок местного управления содержит (фиг.2) второй счетчик 22, второй дешифратор 23, второй триггер 24, шестой 25, седьмой 26 и восьмой 27 элементы И, третий 28, четвертый 29 и пятый 30 элементы ИЛИ и первый элемент НЕ 31.

Блок управления содержит (фиг.З) третий триггер 32, формирователь 33 управляющих сигналов, второй элемент НЕ 34, шестой 35, седьмой 36 и восьмой 37 элементы ИЛИ и элементы И с девятого по двадцать второй 38-51.

Устройство работает следующим образом.

Первоначально все блоки устройства установлены в нулевое состояние. Цепи установки в нуль условно не показаны. В работе устройства различаются два цикла.

В первом цикле осуществляется обращение к накопителю в режиме записи нулевой (единичной) инфорoмации по всем адресам. При пуске устройства формирователь 1 (фиг.1) производит полный перебор всех адресов i-ой микросхемы (i 1,2,...,m), где m - количество микросхем в каж5дом разряде проверяемого накопителя. Обращение к микросхеме осуществляет формирователь 1. Цепи блокировки схемы 2 сравнения и блоков 4 и 5 условно не показаны.

Блок 8 формирует сигналы записи,

0 поступающие в накопитель, по всем адресам i-ой микросхемы, формирователь 6 формирует число нулей. Таким образом, в первом цикле происходит запись О по всем адресам

5 i-ой микросхемы каждого разряда накопителя .

При достижении последнего адреса микросхемы заканчивается первый цикл работы устройства. Во втором

0 цикле осуществляется проверка взаим- ного влияния ячеек памяти в найопителе. Для этого в одну из ячеек памяти (контролируемую) записывается

единица или нуль, затем происхо5дит многократное считывание соответственно нулевой или единичной информации из остальных ячеек паияяти, тем самым осуществляется влияние на контролируемую ячейку. Количество

0 контролируемых ячеек задается блоками 4 и 5 (фиг.1) выбор неконтролируемых ячеек памяти определяется топологией микросхем и особенностью работы накопителя, построенного на

5 намических элементах памяти.

При переходе во -второй цикл работы устройства с четвертого выхода формирователя 1 на вход формирователя 6 вьщается сигнал, разрешающий

0 изменение числа. Блок 8 формирует последовательность стробирующих сигналов ВИ1, ВИЗ, ВИ4, ВИ5, управляющие работой устройства.

По сигналу ВИ4 коммутатор 19 пе5реключается на второй цикл работы, причем На выходе блока 6 формируется 1. В формирователе 1 устанавливается контролируемый адрес по сигналу с выхода блока 4 и осуществ0ляется запись 1 по контроли{эуемому адресу в микросхемы каждого разряда накопителя. Контролируемый адрес запоминается в регистре 15, при чем сигнал записи адреса в регистр

5 15 формируется в блоке 19 по сигналу ВИЗ из блока 8. Для выявления взаимного влияния ячеек памяти в накопителях и для эффективной провеки на правильность хранения информации в контролируемом адресе необходмо осуществлять длительное обращение к ячейкам памяти, расположенным в той же строке и в том же столбце, что и контролируемая ячейка памяти. Длительность обращения в режиме считывания к неконтролируемым ячейкам памяти, равная периоду регенерации задается счетчиком 9, счетная единица в который формируется в блоке 8 элементами И 48 и 50 после срабатывания коммутатора 19, в котором запоминается момент перехода с первого цикла работы устройства во второй на время режима записи единиц в контролируемый адрес. Сигнал, сформированный на выходе коммутатора 19, является разрешением для изменения режима и числа. В блоке 8 срабатывает триггер 32 (фиг.З), формирователь 6 {фиг.1) срабатывает по сигналу ВИ4. Таким образом, блок 8 формирует режим считывания, а с выхода формирователя б выдается число, все разряды которого равны нут лю.

Формирователь 1 содержит три счетчика: строк, столбцов и микросхем. Во втором цикле работы устройства формируется счетная единица по сигналу ВИ1 в счетчик строк по разрешению, поступающему с.инверсного плеча триггера 10, параллельно , формируется счетная единица по сигналу 1ВЙ1 Bi счетчик 9, .при полном переборе адресов строк осуществляется заполнение 6 разрядов, п-разрядного счетчика 9 (2 - количество ячеек памяти в строке (столбце) накопителя) , при этом на втором выход деши1|)ратора 11 формируется сигнал, который разрешает формирование сигнала записи информации из регистра 15 в счетчики строк и столбцов формирователя 1 , счетной единицы в триггер 10 и в k-разрядную часть счетчика 9 (k п - i), при этом в счетчиках строк и столбцов формирователя 1 сформировывается контролируемый адрес. По сигналу ВИЗ срабатывает триггер 10 и k-разрядная . часть счетчика 9, а по сигналу ВИ5 1-разрядная часть счетчика 9 обнуляется. Следовательно k разрядов счетчика 9 подсчитывают заполнение I разрядов счетчика 9. Триггер 10 сигналом с инверсного выхода блокирует формирование счетной единицы в счетчик строк формирователя 1, а сигналом с прямого выхода разрешает формирование счетной единицы (по ВИ1) в счетчик столбцов формирователя 1. Контролируешлй адрес сохраняется в формирователе 1 в течение времени между сигналами ВИЗ и ВИ1, а обращение к накопителю осуществляв ется между сигналами ВИ1 и ВИЗ, что исключает обращение к контролируемой ячейке памяти. При полном переборе адресов столбцов ячее-к памяти происходит заполнение разрядов счетчика 9, что приводит к формированию сигнала на втором выходе дешифратора 11, действие которого описано выше. В период многократного обращение в режиме считывания нулевой информации из неконтролируемых ячеек памяти происходит взаимное

5 влияние на информацию, хранимую в контролируемой ячейке памяти., и проверяется правильность считанной информации из неконтролируемых ячеек памяти схемой 7 сравнения,

0 на выходе которой при наличии ошибки , формируется сигнал ошибки.

Блок 20 формирует сигнал в период многократного обращения в режиме считывания к неконтролируемым ячейкам памяти. Сигналы с выхода схемы 7 и третьего выхода блока 20 поступают в блок 3, на выходе которого при этом формируется сигнал, останавливающий работу формирователя 33

0 (фиг.З) блока В. При останове устройства происходит фиксация периода неконтролируемого считывания, адреса неисправной ячейки памяти и номера неисправного разряда накопителя.

5 При отсутствии ошибок, в период многократного считывания происходит заполнение k разрядов счетчика 9 (фиг.1) и на первом выходе дешифратора 11.формируется сигнал, который

0 разрешает формирование управляющего сигнал в блок 20. Блок 8 по сигналу ВИ5 формирует счетную единицу в счетчик 22 (фиг.2) блока 20 Формируется сигнал на третьем выходе дее шифратора 23, который соответствует режиму считывания из контролируемой ячейки памяти. Сигнал на выходе элемента НЕ 31 блокирует формирование счетных единиц в счетчики строк и столбцов формирователя 1 и в 2-разрядную часть счетчика 9. Сигнал-на выходе элемента ИЛИ 29 является разрешением для формирования сигнала на выходе триггера 32 (фиг.З) в блоке 8. Сигнал на выходе

5 элемента ИЛИ 30 (фиг.2) является разрешением для формирования сигнала на выходе формирователя б (фиг,1). Таким образом, к моменту осуществления считывания из контролируемой .

0 ячейки памяти 2 -разрядная часть счетчика 9 и триггер 10. находятся в прежнем состоянии, в счетчиках строк и столбцов формирователя 1 записан адрес контролируемой ячейки

5 памяти.

Формирователь б .срабатывает по сигналу ВИ1 и на его выходе формируется сигнал Единица , Осуществляется считывание единичной информации из контролируемой ячейки памяти Анализ йчитанной информации осущестляется схемой 7 сравнения, на выходе которой при наличии ошибки форми руется сигнал. Сигналыс выходов схемы 7 и с четвертого выхода блока 20 поступают в блок 3, в результате происходит останов устройства, при этом фиксируется режим считывания из контролируемой ячейки памяти ее адрес и номер неисправного разряда накопителя, При отсутствии сяпибки организуется контроль следующей ячейки памяти, предварительно в бывшую контролируемую ячейку памяти записывается нуль, в новую контролируемую ячейку Зсцтисывается единица, а затем осуществляется многократное считывание из неконтролируемых ячеек памяти. По-сигналу ВИЗ срабатывает триггер 32 в блоке 8 управления и формируется режим записи, формируется также счетная единица в счетчик 22 блока 20. Формируются сигналы на.выходах элемента НЕ 31, элементов ИЛИ 29 и 30, вследствие чего сохраняется запрет для формирования счетных единиц в счетчики, строк, столбцов формирователя и в С -разрядную часть счетчика 9 Кроме того, сохраняется разрешение для формирования числа. Сигйал на выходе элемента ИЛИ 29 является разрешением для установки в нуль триггера 10, по сигналу ВЙ1 на выхо|де формирователя б формируется нуль |и осуществляется запись нуля в бывшую контролируемую ячейку памяти

По ВИ5 устанавливается в .нуль триггер 10 и формируется .счетная единица в счетчик 22 блока 20. Таким образом сохраняется режим записи, разрешение управления формирователем б и по ВИ1 на выходе формирователя б формируется 1, разрешается одновременное формирование счетных единиц -в счетчики строк и столбцов формирователя 1 для формирования нового контролируемого адреса. Разрешением для формированйя счетной единицы в счетчик строк является сигнал, поступающий с инверсного выхода триггера 10, а в счетчик столбцов - сигналы с третьего выхода формирователя 1 и с первого выхода дешифратора 23, инверсное значение которого блокирует поступление счетной единицы в 8 разрядную часть счетчика 9. Сигнал с первого выхода дешифратора 23 является разрешением для записи адреса в регистр 15 (по ВИЗ) . .Формирует.ся режим записи 1 в новый контролируемый адрес, при этом в блоке 20 по ВИ1 запоминается на триггере 24 наличие сигнала на выходе схемы 7, и устанавливается в нуль -k-pasрядная часть счетчика 9. ФррмируютсЙ сигналы на выходах элемента ИЛИ 29 и триггера 24. По ВИ4 устанавливается в нуль счетчик 22, что приводит к исчезновению сигналов на первом выходе дешифратора 23 и выходе

10 элемента ИЛИ 30 и формированию сигнаша на втором выходе дешифратора 23, который является разрешением для установки в нуль триггера 24. Сигнал ка выходе элемента ИЛИ 29

5 является разрешением у.правления триггером 32 блока-8, сигнал на втором ; выходе дешифратора 23 соответствует периоду многократного считывания из неконтролируемых ячеек памяти, сиг0нал на выходе триггера 24 яв пяется разрешением управления формирователем 6. Отсутствие сигнала на первом выходе дешифратора 23 блокирует одновременное управление счетчиками

5 строк и столбцов формирователя 1 и разрешает формирование счетной единицы в 2 -разрядную часть счетчика 9. Блок. 8 формирует режим считывания и начинается период мно0гократного считывания из неконтроли- . руемых ячеек накопителя, как описано выше.I

Проверка ячеек памяти путем многократного считывания происходит до

5 момента формирования, сигнала на первом выходе схемы 2 сравнения, который является разрешением формирова:ния счетной- единицы в счетчик микросхем формирователя 1. После осуществления считывания и передачи

0 в конечную контролируемую ячейку памяти (это соответствует наличию сигнала на четвертом выходе дешифратора 23 по ВИЗ формируется счетная единица в счетчик микросхем этот

5 же сигнал устанавливает в нуль остальные блоки устройства. Далее осуществляется проверка следующих микросхем в каждом разряде «акопителя .описанным выше способом до фор0мирования сигналов на выходах схемы 2 сравнения. Это соответствует окончанию проверки всех ячеек памяти всех микросхем во всех разрядах накопителя при задании первоначаль5но нулевого фона т.е. в контролит руемую ячейку памяти записывается единица и осуществляется многократное считывание нулевой информации из неконтролируемых ячеек .

0 памяти . Для полной проверки -накопителя необходимо записать нуль в контролируемую ячейку памяти и осуществлять ьдаогократное считывание единичной информации из остальных ячеек. Для этого в формирователь б

5 введен триггер, который управляется счетной единицей, поступающей в счетчик микросхем формиро вателя 1 при наличии сигнала на втором выходе схемы 2 сравнения, при срабатывании которого все блоки устройства устанавливаются в нуль. Таким образом, введение в предлагаемое устройство блока 20, коммутатора 19 и регистра 15 повышает надежность устройства и позволяет проверять взаимное влияние ячеек памяти как в.накопителях, построенных на статических элементах памяти, так и в накопителях, построенных на динамических элементах памя,ти. Технико-экономическое преимущество устройства заключается в его более высокой надежности по сравнени с прототипом. Формула изобретения 1, Устройство для контроля оперативной памяти, содержащее формирователь-адресных сигналов, схемы сравнения, формирователь числовых -сигналов, блок управления, первый счетчик, первый триггер, первый дешифра.тор, элементы И, первый элемент ИЛИ первый блок местного управления, блок ввода начального адреса, выход которого подключен к первому входу формирователя адресных сигналов, и блок ввода конечного адреса, выход которого соединен с первым входом первой схемы сравнения, первый выход и второй и третий входы которой подключены соответственно к первому входу блока управления и к первому и второму выходам формирователя адресных сигналов, второй вход кото рого соединен с первым выходом блока управления, второй выход последнего подключен к первому входу первого счетчика, выходы которого соединены с входами первого дешифрато ра, первый выход последнего соеди-нен с вторым входом блока управления, трегий вход и третий вв1ход которого подключены к первому выходу и первому входу первого триггера, четвер тый выход блока управления соединен с первым входом формирователя число вых сигналов, первый выход которого подключен к первому входу второй схемы сравнения, выход последней соединен с первыми входами первого и второго элементов И, выход первог элемента И соединен с первым входом первого элемента ИЛИ, выход которог подключен к входу первого блока мес ного управления, второй вход второй схемы сравнения соединен с пятым выходом блока управления, а третий вход является входом устройства, отличающееся тем, что, с елью повышения надежности устройства в него введены второй блок местного управления (, коммутатор тестовых сигналов, второй элемент ИЛИ, третий, четвертый и пятый элементы И и регистр адреса, первый вход которого соединен с выходом второго элемента ИЛИ, а второй вход и выход подключены соответственно к первому выходу и к третьему входу формирователя адресных сигналов, четвертый, пятый и шестой входы и третий выход которого соединены соответственно с шестым, седьмым и четвертым выходами и с четвертым входом блока управления, пятый вход которого подключен к второму выходу первого дешифратора и,первому входу третьего элемента И, йторой вход которого соединен с пятъал выходом блока управления, а заходы с седьмым входом формирователя адресных сигналов, четвертый выход которого подключен к шестому входу блока управл;ения и второму входу формирователя числовых сигналов, третий и четвертый входы которого соединены соответственно с восьмым и пятым выходами блока управления, седьмой вход которого подключен- к первому выходу коммутатора тестовых сигналов и пятому входу формирователя числовых сигналов, шестой вход которого соединен с восьмым входом блока управления и вторым выходом коммутатора тестовых сигналов, третий выход которого подключен к первому входу второго элемента ИЛИ, второй вход последнего соединен с выходом четвертого элемента И, первый вход которого подключен к. девятому выходу блока управления и первому входу коммутатора тестовых сигналов , второй вход и четвертый, пя- тый и шестой выходы которого соединены соответственно с десятым выхо-. дом и девятым, десятым и одиннадцатым входами блока управления, третий- и четвертый входы коммутатора тестовых сигналов подключены соответственно к пятому выходу блока управления и первому входу второго блока местного управления и к восьмому выходу блока управлеЕ1ия и второму входу второго блока местного управления, третий вход и первый выход которого соединены соответственно с одиннадцатым выходом блока управления и с вторым входом четвертого элемента Ии двенадцатым входом блока управления, двенадцать выход которого подключен к второму входу первого счетчика, третий и четвертый входы которого соединены соответственно с третьим выходом блока управления и с вторым выходом второго блока местного управления, третий и четвертый выходы которого подключены соответственно к вторым входам первого и второго элементов И, а пятый и шестой выходы - соответстт венно к седьмому и к восьмому входам формирователя числовых сигналов, девятый ВХОД которого соединен с вторьам выходом первой схемы сравнения, выход второго элемента И соединен с вторым входом первого элемента ИЛИ, седьмой, восьмой и девятый выходы второго блока местного управления подключены соответатвенно к тринадцатому и Четырнадцатому входам блока управления и к пятнадцатому входу блока управления и первому входу пятого элемента И, второй |вход которого соединен с тринадцатым выходом блока управления, а выход - с вторым входом первого триггера, второй выход которого подключен к шестнадцатому входу, блока управления, семнадцатый вход которого со единен с выходом первого блока местного управления а четырнадцатый

выход является выходом устройства.

2. Устройство по П.1, о-тл и чающее ся тем, что второй блок местного управление содержит второй счетчик, второй дешифратор, второй триггер, третий, четвертый и пятый элементы ИЛИ, элемент НЕ и . шестой, седьмой и восьмой элементы И, причем первые входы шестого и седьмого элементов И и второго счетчика являются соответственно первым, вторым и третьим входами блока, выход шестого элемента И подключен к второму входу второго счетчика.

которого соединены с входами второго дешифратора, первый и второй выходы которого подключены соответственно к вторым входам шестого и седьмого элементов Ник первому входу восьмого элемента И, второй

вход которого соединен с первым входом седьмого элемента И, выходы седьмого и восьмого элементов И подключены соответственно к входам второго триггера, третий и четвертый выходы второго дешифратора соединены соответственно с первыми входами третьего, четвертого и пятого элементов ИЛИ .и с вторыми входами третьего и четвертого элементов ИЛИ, выход третьего элемента ИЛИ подключен к входу элемента НЕ, первый выход

-второго дешифратора является первым выходом блока и соединен с третьим входом четвертого элемента ИЛИ, выход седьмого элемента И, второй и третий выходы второго дешифратора и выход пятого элемента ИЛИ являются соответственно вторым, третьим, четвертыми пятым выходами блока, выход второго триггера является шестым выходом блока и соединен с вторым входом пятого элемента-ИЛИ, выходы элемента НЕ и четвертого элемента ИЛИ являются соответственно седьмым и восьмьп«1 выходами блока

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР №407398, кл. С 11 С 29/00, 1970.

2.Авторское свидетельство СССР №769642, кл. G 11 С 29/0.0, 1979 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля накопителей | 1982 |

|

SU1048521A1 |

| Устройство для контроля оперативной памяти | 1983 |

|

SU1295455A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Буферное запоминающее устройство | 1980 |

|

SU932566A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для ввода информации | 1983 |

|

SU1109732A1 |

| Устройство для контроля памяти | 1982 |

|

SU1020865A1 |

| Устройство для сжатия информации | 1982 |

|

SU1043711A1 |

Авторы

Даты

1982-12-07—Публикация

1981-06-18—Подача