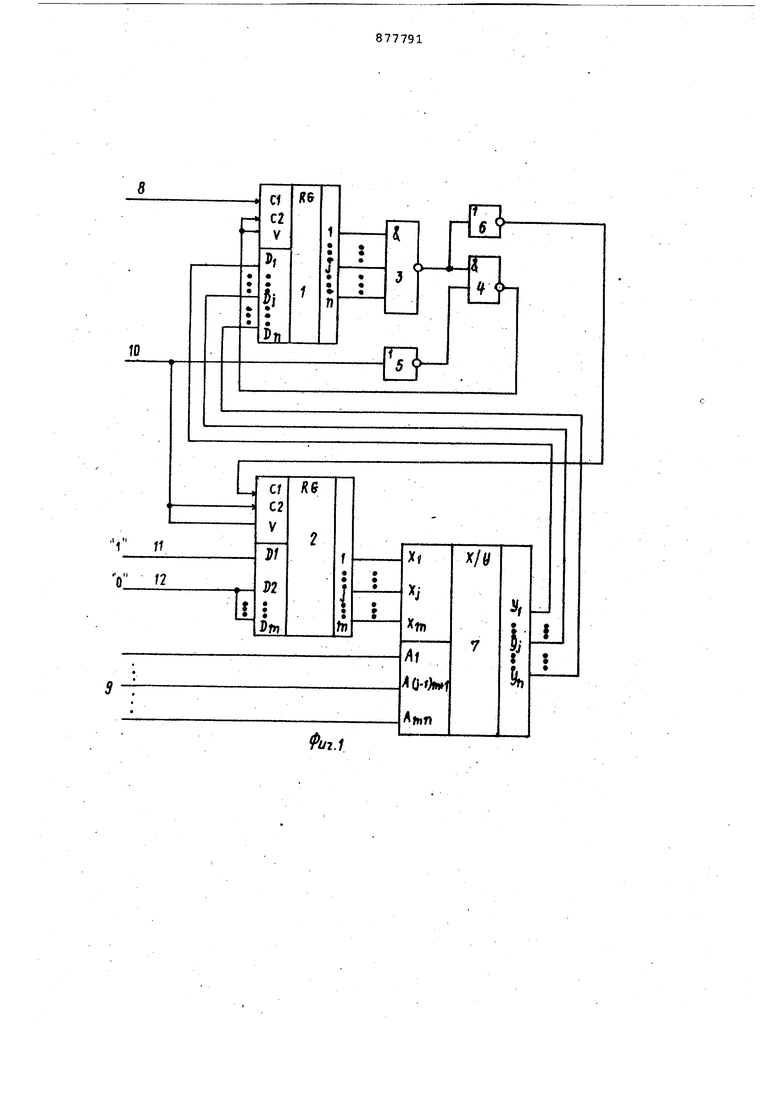

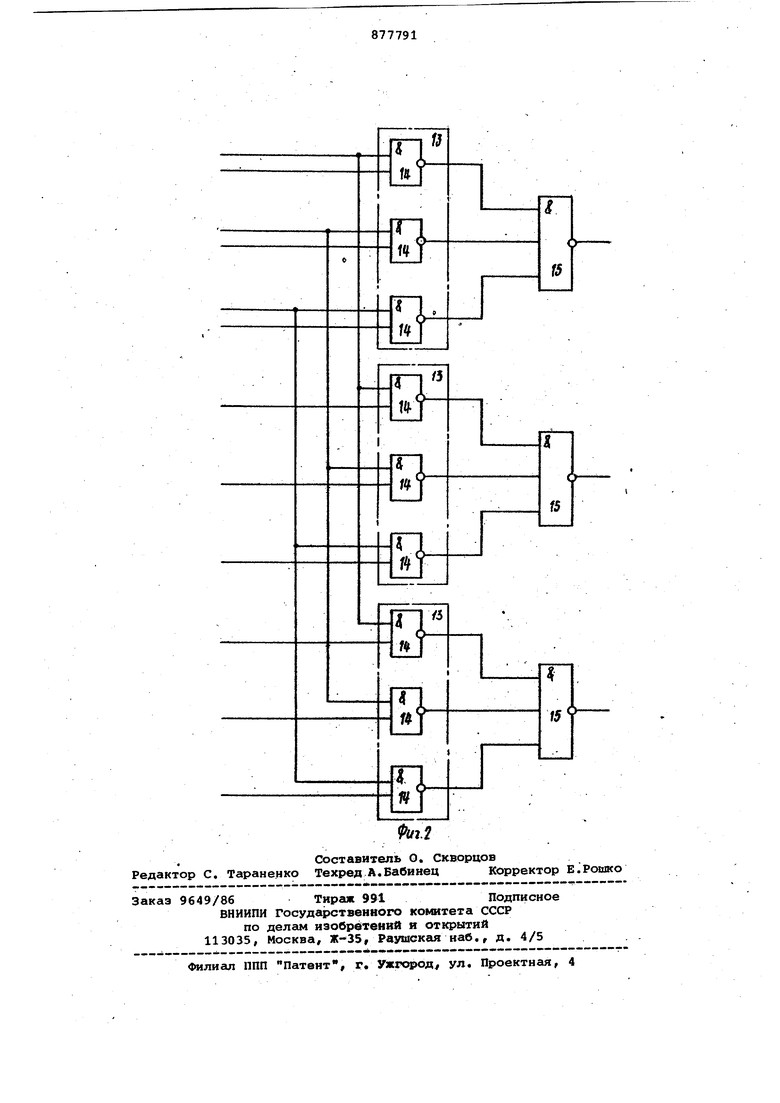

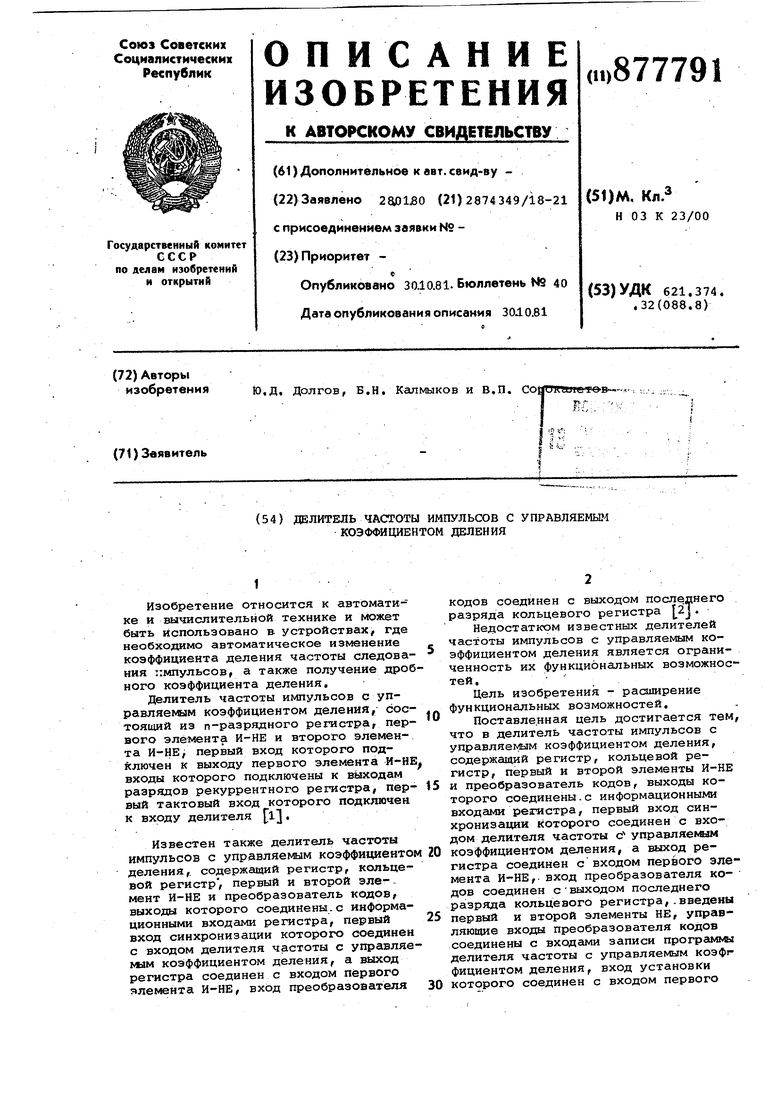

1 Изобретение относится к автоматике и вычислительной технике и может: быть использовано в устройствах где необходимо автоматическое изменение коэффициента деления частоты следования ::мпульсов, а также получение дроб ного коэффициента деления. Делитель частоты импульсов с управляемым коэффициентом деления, соетоящий из п-разрядного регистра, первого элемента И-НЕ и второго элемента И-НЕ, первый вход которого подйлючен к выходу первого элемента Н-НЕ входы которого подключены к выходам разрядов рекуррентного регистра, пёрвый тактовый вход которого подключен к входу делителя l. Известен также делитель частоты импульсов с управляемым коэффициенто деления, содержащий регистр, кольцевой регистр , первый и второй эле-, мент И-НЕ и преобразователь кодов, выходы которого соединены.с информационными входами ретастра, первый вход синхронизации которого соединен с входом делителя частоты с управляе мом коэффициентом деления, а выход регистра соединен с входом первого элемента И-НЕ, вход преобразователя кодов соединен с выходом последнего разряда кольцевого регистра 2j. Недостатком известных делителей частоты импульсов с управляемым коэффициентом деления является ограниченность их функциональных возможностей. Цель изобретения - расширение функциональных возможностей. Поставленная цель достигается тем, что в делитель частоты импульсов с управляемым коэффициентом деления, содержащий регистр, кольцевой регистр, первый и второй элементы И-НЕ и преобразователь кодов, выходы которого соединены.с информационными входами реатистра, первый вход синхронизации которого соединен с входом делителя частоты с управляекплм коэффициентом деления, а выход регистра соединен с входом первого элемента И-НЕ,. вход преобразователя ко- дов соединен свыходом последнего разряда кольцевого регистра,.введены первый и второй элементы НЕ, управляющие входы преобразователя кодов соединены с входами записи программы делителя частоты с управляемым коэфг фициентом деления, вход установки которого соединен с входом первого элемента НЕ, выход которого соединен с первым входом второго элемента И-Н второй вход которого соединен с входом второго элемента НЕ и выходом первого элемента И-НЕ, дополнительны входы которого соединены с дополните ными выходами регистра, второй вход синхронизации и вход управления кото рого соединены с выходом второго эле мента И-НЕ, а выход второго элемента НЕ соединен с первым входом.синхронизации кольцевого регистра, второй вход синхронизации и вход управления которого соединены с входом установ ки делителя частоты с управляе1«ым коэффициентом деления, шина единичного логического сигнала соединена первым информационным входом кольце вого регистра, остальные информацио ные входы которого соединены с шиной нулевого логического сигнала, а дополнительные вьпсоды кольцевого регистра соединены с дополнительными выходами преобразователя кодов, . Преобразователь кодов содержит группы двухвходовых элементов И-НЕ и многовходовые элементы И-НЕ, выходы которых соединены с выходами преобразователя кодов, а входы каждого из многовходовых элементов И-НЕ сое динены с выходами двухвходовых элементов И-НЕ соответствующей группы, Лервые входы двухвходовых элементов И-НЕ соединены с соответствуквдими управляющими входами преобразователя кодов, дополнительныйi-и вход которого соединен с вторыми входами 1-ы двухвходовых элементов И-НЕ каждой из групп двухвходовых элементов И-НЕ а второй вход последнего двухвходового элемента И-НЕ каждой из групп двухвходовых элементов Й-НЕ соединен с входом преобразователя кодов. На фиг. 1 приведена структурная схема делителя частоты импульсов с управляемым коэффициентом деления; на фиг. 2 - структурная схема преобразователя кодов. Делитель частоты импульсов с упр ляемым коэффициентом деления содер жит регистр 1, кольцевой регистр 2, первый 3 и второй 4 элементы И-НЕ, первый 5 и второй 6 элементы НЕ и преобразователь 7 кодов, выходы которого соединены с информационными входами регистра 1, первый вход син хронизации которого соединен с входом 8 делителя частоты с управляемо коэффициентом деления, а выход регистра 1 соединен с входом первого элемента И-НЕ 3, вход прйобразовате ля 7 кодов соединен с выходом последнего разряда кольцевого регистра 2, управляющие входы преобразователя 7 кодов соединены с входами 9 записи программы делителя частоты с управляемым коэффициентом деления, вход 10 установки которого соединен с входом первого элемента 5 НЕ, выход которого соединен с первым входом второго элемента 4 И-НЕ, второй вход которого соединен с входом второго элемента б НЕ и выходом первого элемента 3 И-НЕ, дополнителиные входы которого соединены с дополнительными выходами регистра 1, второй вход синхронизации и вход управления .которого соединены с выходом второго элемента 4 И-НЕ, а выход второго элемента 6 НЕ соединен с первым, «входом синхронизации кольцевого регистра 2, второй вход синхронизации и вход управления которого соединены с входом установки делителя частоты с управляемым коэффициентом деления, шина 11 единичного логического сигнала соединена с первым информационным входом кольцевого регистра 2, остальные информационные входы которого соединены с шиной 12 нулевого логического сигнала, а дополнительные выходы кольцевого регистра 2 соединены с дополнительными выходами преобразователя 7 кодов.с Цреобразователь 7 кодов содержит группы 13 двухвходовых элементов 14 И-НЕ и многовходовые элементы 15 И-НЕ, выходы которых соединены с выходами преобразователя 7-кодов, а входы каждого из многовходовых элементов 15 И-НЕ соединены с выходами двух входовых элементов 14 И-НЕ соответ твующей группы 13, первые входы дв5 входовых элементов 14 И-НЕ соединены с соответствующими управляю щими входами преобразователя 7 кодов дополнительный i-й вход которого соединен с вторыми входами i -ых двухвходовых элементов 14 И-НЕ каждой из групп двухвходовых элементов И-НЕ, а второй вход последнего двухвходового элемента 14 И-НЕ каждой из групп 13 двухвходовых элементов И-НЕ соединен с входом преобразователя 7 кодов. Устройство работает следующим образом. При поступлении на вход 10 установки одиночного импульса кольцевой регистр 2 приходит в состояние, соответствующее коду на его информационных входах, и на вход преобразователя 7 кодов поступает М-разрядный код 100.0,0 Преобразователь 7 кодов в соответствии с заданной программой преобразует входной код состояния разрядов кольцевого регистра 2 в выходной код, подаваемый на информационные входы регистра 1, . Сигн Yj j I , 2 ,... , n), подаваемый на J-й, информационный вход регистра 1, определяется в преобразователе 7 кодов из соотношения} Ч:--ii Atj-f)i nxv; - коэффициенты, примимаюцие значения О или 1 в в соответствии с кодо , программы; - состояние i-ro разря да кольцевого регистра 2. Импульс установки, проходя через элемент 5 НЕ,и элемент 4 И-НЕ, посту пает на вход управления и второй вхо синхронизации регистра 1, и разряды ре.гистра 1 устанавливаются в состояния/ соответствующие коду на информа цибнных входах. Изменение состояний регистра 1 происходит под действием импульсов, поступгшзщих на вход 8 при отсутствии сигнала установки на вход 10 управления. Коэффициент дЬле ния К(,2,...,т) определяется количест ом состояний регистра L от ус тановленного до состояния логической 1 каждого разряда, И-Разрядный код 11. этого состояния поступает на элемент 3 И-ИЛИ, Сигнал с выхода это гр элеме1 та через элемент б НЕ посту .на первый вход сйнхронизг1ции кольцевого регистра 2 и сдвигает логическую 1 в следуквдий его разряд, изменяя код состояния кольцевого регистра 2. Преобразователь 7 кодов по дйет на информационные входы регистра 1 следующий эапрограшмированный код, который под действием toro же сигнала с выхода элемента 3 Й-НЁ, проходящего через элемент 4 И-НЕ и поступакадего на вход управления и второй вход синхронизации регистра 1 устанавливает его в соответствующее состояние, определяющее следунлций коэффициент деления k (i 1,2,... ,m Так происходит изменение коэффициента деления , К, «««г tn На выходе делителя появляются по ;рдному импульсу от К , К, . . , Кц), К , . входных. Эти импульсы могут быть использованы для управления различны ми процессами с изменяемой зремен ной программой, а также составляют последовательность с частотой в К драз меньшей, чем -у входной последовательности, где Формула изобретения 1. Делитель частоты импульсов с управляемом коэффициентом деления, содержащий регистр, кольцевой ре- гистр, первый и второй элементы И-НЕ и преобразователь кодов, выходы кото рого соединены с информационны вхо дами регистра, первый вход синхронизации которого соединен с входом делителя частоты с управляемым коэффициентом деления, а выход регистра соединен с входом первого элемента И-НЕ, вход преобразователя кодов соединен с выходом последнего разряда кольцевого регистра, о т л и ч а ю щ и и с я тем, что, с целью расширения функциональных возможностей, в него введены первый и второй элементы НЕ, управляющие входы преобразователя кодов соединены с входами записи программы делителя частоты с управляемым коэффициентом деления, вход установки -которого соединен с входом-первого элемента НЕ, выход которого соединен с первым входом второго элемента И-НЕ, второй вход которого соединен с входом второго элемента НЕ и выходом перво- . го. элемента И-НЕ, дополнительные входы которого соединены с дополнительнын и выходами регистра, второй .вход синхронизации и вход управления которого .соединены с выходом второго элемента И-НЕ, а выход второго. элемента НЕ соединен с первым входом синхронизации кольцевого регистра, второй вход синхронизации и вход управления которого соединены с входом установки делителя частоты с управляемым коэффициентом деления, шина единичного логического сигнала соединена с первым информационным входом кольцевого регистра, остальные информационные, входы которого соединены с шиной нулевогологического сигнала, а дополнительное выходы кольцевого регистра соединены с дополнительными выходами преобразователя кодов. -. 2. Делитель по п. 1, о т л и .ч а ю щ и и с я. тем, что преобразователь кодов содержит группы двухвходовых элементов И-НЕ и многовходовые элементы И-НЕ, выходы которых соединены с выходами пр.еобразователя кодов , а входы, каждого из кшоговходовых элементов И-НЕ соединены с выходами двухвхоДовых элементов И-НЕ соответствующей группы, первые входы двух- , входовых элементов И-НЕ соединены с соответствующими управляющими входами ппеобЬазователя кодов, дополнительный i-й вход которого соединен с вторыми входами I-ых ДВУХВХОДОВЫХ элеейтов И-НЕ каждой из групп вухвходовых элементов И-НЕ соеинен с входом преобразователя кодов. Источники информации, ринятые во внимание экспертизе 1.Акцептованная заявка Великобригании 1501279,кл.Н 03 К 21/36,1979.1 2, Авторское свидетельство СССР 354578, кл. И 03 К 23/00, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор тональных сигналов верхних частот для электромузыкального инструмента | 1978 |

|

SU769606A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1990 |

|

RU2015539C1 |

| Устройство для приема последовательного кода | 1980 |

|

SU960893A1 |

| Делитель частоты с переменным коэффициентом деления | 2021 |

|

RU2762529C1 |

| Цифровой имитатор воздушных давлений | 1985 |

|

SU1265728A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

| СПОСОБ ДИСКРЕТНОГО КОНТРОЛЯ РАССТОЯНИЙ ДО ИСТОЧНИКА КОЛЕБАНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2028579C1 |

| Устройство для обмена информацией | 1986 |

|

SU1363228A1 |

| Генератор случайного процесса | 1983 |

|

SU1100622A1 |

| Адаптивный умножитель частоты | 1989 |

|

SU1793538A1 |

Авторы

Даты

1981-10-30—Публикация

1980-01-28—Подача