Изобретение относится к автоматике и вычислительной технике, а также к системам автоматического управления и может найти применение в системах числового программного управления, в измерительных и вычислительных устройствах.

Известен цифро-частотный умножитель, содержащий частотный вход, делитель частоты, состоящий из n-1 последовательно включенных триггеров, n импульсно-потенциальных элементов И, элемент ИЛИ, n установочных входов и выходной триггер [1]. Недостатком умножителя являются большие аппаратные затраты за счет использования импульсно-потенциальных элементов и многовходового элемента ИЛИ.

Известен цифро-частотный интегратор, содержащий n-разрядный счетчик приращений Δ x(t), задающий программу выбора двоичных символов yi, n-разрядный счетчик приращений Δ y(t), формирующий значение подынтегральной функции, линейку из n вентилей "опроса" значений двоичных символов yi, элемент ИЛИ, формирующий выходной поток приращений ν (t) [2]. Недостатком интегратора являются большие аппаратные затраты за счет использования триггеров с импульсными выходами в n-разрядном счетчике приращений Δ x(t), задающем программу выбора двоичных символов yi, и многовходового элемента ИЛИ.

Наиболее близким к предлагаемому делителю частоты является устройство для деления частоты с переменным коэффициентом деления, содержащее n-разрядный двоичный счетчик с входами разрешения счета, установки в начальное нулевое состояние, разрешения деления, синхровходом, выходом переполнения, подключенным к выходу переполнения делителя, инверсный выход синхронизации, к выходу устройства не подключенный, n-разрядную шину управления, двухвходовый элемент И-НЕ, выход которого является прямым информационным выходом устройства, причем второй вход элемента И-НЕ подключен к входу расширения устройства, первый вход элемента И-НЕ подключен к выходу n-входового элемента ИЛИ-НЕ и к инверсному выходу делителя, входы элемента ИЛИ-НЕ подключены к выходам элементов И, при этом выход первого элемента И подключен к первому входу элемента ИЛИ-НЕ, выход n-го элемента И подключен к последнему n-у входу элемента ИЛИ-НЕ, первый вход каждого элемента И подключен к инверсному выходу разрядного триггера двоичного счетчика, первый вход первого элемента И подключен к инверсному выходу первого разрядного триггера двоичного счетчика, первый вход n-го элемента И подключен к инверсному выходу n-го разрядного триггера двоичного счетчика, предпоследний вход каждого из элементов И подключен к инверсному выходу синхронизации двоичного счетчика, последний вход каждого из элементов И подключен к управляющему входу, последний вход первого элемента И подключен к n-у управляющему входу, последний вход n-го элемента И подключен к первому управляющему входу, начиная с второго элемента И, входы элементов И с второго по предшествующий предпоследнему подключены к прямым выходам разрядных триггеров двоичного счетчика, младшим по отношению к элементу И, каждый i-й вход (i изменяется от 2 до k) каждого k-го элемента И (k изменяется от 2 до n) подключен к прямому выходу r-го разрядного триггера двоичного счетчика (r изменяется от k-1 до 1) [3].

Недостатками данного устройства являются большие аппаратные затраты на реализацию многовходовых элементов И и многовходового элемента ИЛИ-НЕ, большая нагрузка на прямые выходы разрядных триггеров двоичного счетчика.

Цель изобретения - сокращение аппаратных затрат, уменьшение выходной нагрузки двоичного счетчика.

Цель достигается тем, что в делитель частоты с переменным коэффициентом деления, содержащий n-разрядный двоичный счетчик с входами разрешения счета, установки в начальное нулевое состояние, разрешения деления, синхровходом, выходом переполнения, подключенным к выходу переполнения делителя, инверсный выход синхронизации, к выходу устройства не подключенный, n-разрядную шину управления, двухвходовый элемент И-НЕ, вход расширения делителя частоты, информационный выход делителя, введены n элементов 2ИЛИ-И-НЕ, причем выход первого элемента 2ИЛИ-И-НЕ соединен с первым входом элемента И-НЕ, второй вход которого соединен с инверсным выходом синхронизации двоичного счетчика, выход элемента И-НЕ является информационным выходом делителя частоты, выход расширения которого соединен с выходом первого элемента 2ИЛИ-И-НЕ, первые входы элементов 2ИЛИ-И-НЕ с первого по n-й соединены соответственно с инверсными разрядными выходами двоичного счетчика с первого по n-й, второй вход i-го элемента 2ИЛИ-И-НЕ (i изменяется от 1 до n-1) соединен с выходом (i+1)-го элемента 2ИЛИ-И-НЕ, второй вход n-го элемента 2ИЛИ-И-НЕ является входом расширения делителя частоты, третьи входы элементов 2ИЛИ-И-НЕ с первого по n-й соединены соответственно с прямыми разрядными выходами двоичного счетчика с первого по n-й, четвертые входы элементов 2ИЛИ-И-НЕ с первого по n-й соединены соответственно с разрядами шины управления с n-го по первый.

В известных устройствах деление частоты осуществляется за счет суммирования многовходовым элементом ИЛИ-НЕ импульсов, вырабатываемых поразрядными многовходовыми элементами И, что требует больших аппаратных затрат на реализацию как элементов И, так и элемента ИЛИ-НЕ, включенных параллельно друг другу, повышенных требований к нагрузочной способности разрядных выходов двоичного счетчика. Существенным отличием предлагаемого делителя частоты является деление частоты за счет последовательного (итеративного) преобразования потенциальных (по отношению к сигналу на входе синхронизации) управляющих сигналов с шины управления и от разрядов счетчика на элементах 2ИЛИ-И-НЕ, включенных последовательно, с выделением выходного информационного сигнала из потенциального (по отношению к сигналу на входе синхронизации) сигнала на выходе расширения предлагаемого делителя. Сигнал на выходе расширения получается путем последовательного преобразования с использованием элементов 2ИЛИ-И-НЕ сигналов от прямого и инверсного выходов разряда счетчика, сигнала с шины управления и сигнала с выхода последующего элемента 2ИЛИ-И-НЕ. Элементы 2ИЛИ-И-НЕ образуют итеративную (последовательную) цепочку, в которой на каждом элементе на первой ступени в первой паре сигнал с выхода каждого последующего элемента преобразуется с сигналом с инверсного выхода счетчика, во второй паре сигнал с шины управления преобразуется с сигналом от прямого выхода счетчика, причем на нечетный элемент 2ИЛИ-И-НЕ поступает инверсный управляющий сигнал с шины управления, а на четный - прямой сигналы с шины управления, затем на второй ступени сигналы обоих пар преобразуются в сигнал выхода элемента 2ИЛИ-И-НЕ. Сигнал на выходе расширения делителя не является простой суммой сигналов со счетчика, шины управления, сигналов с выходов элементов 2ИЛИ-И-НЕ и описывается оригинальным выражением. Использование итеративной цепочки элементов 2ИЛИ-И-НЕ для получения сигнала на выходе расширения делителя частоты уменьшает аппаратные затраты на реализацию делителя частоты за счет использования четырехвходовых элементов на разряд, уменьшает необходимую нагрузочную способность двоичного счетчика за счет использования прямых и инверсных выходов разряда счетчика лишь на одном элементе 2ИЛИ-И-НЕ.

Анализ литературы показал, что совокупность свойств и признаков, составляющих сущность изобретения, не известна, поэтому данное техническое решение соответствует критерию "существенные отличия".

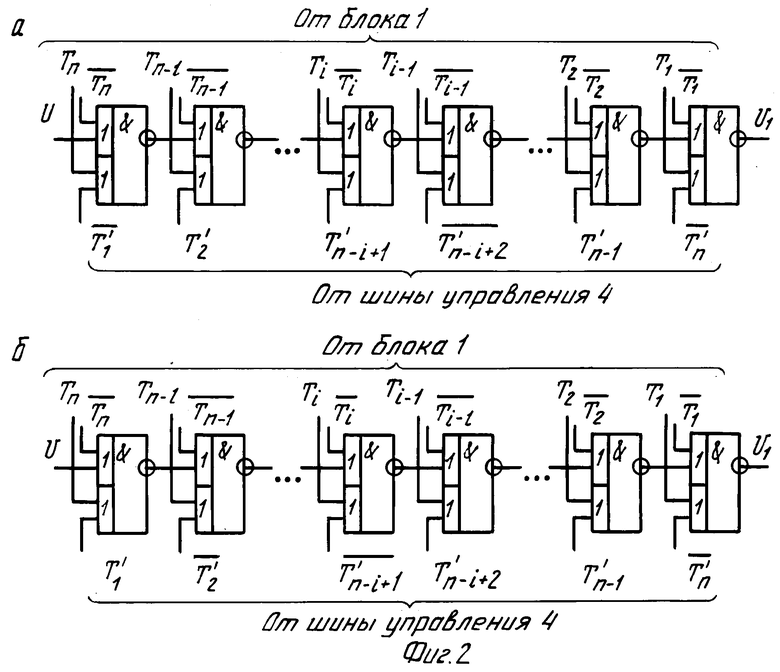

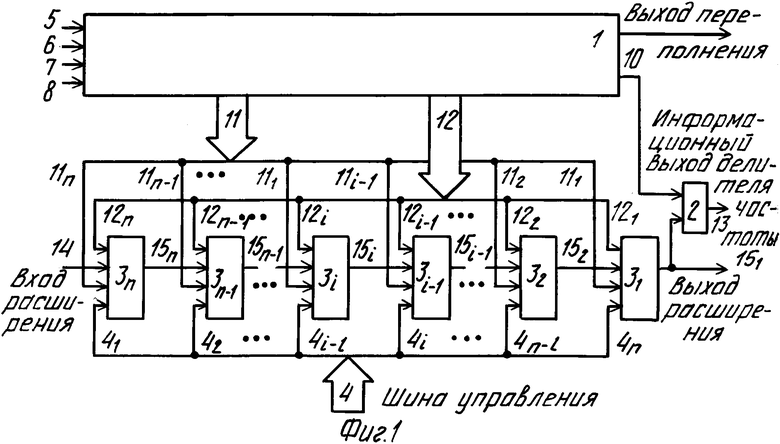

На фиг. 1 изображена структурная схема предлагаемого делителя частоты; на фиг.2 - итеративная схема элементов 2ИЛИ-И-НЕ.

Делитель частоты с переменным коэффициентом деления содержит двоичный счетчик 1, элемент И-НЕ 2, n элементов 2ИЛИ-И-НЕ 3i (31, 32, ...., 3i, ..., 3n), шину 4 управления. Двоичный счетчик 1 имеет первый 5, второй 6, третий 7, четвертый 8 входы, первый выход 9, второй выход 10, подключенный к первому входу элемента И-НЕ 2, третий n-разрядный выход 11, каждый разряд которого 11i (111, 112, ..., 11i-1, 11i, ..., 11n-1, 11n) подключен к третьим входам соответствующих элементов 2ИЛИ-И-НЕ 3i (31, 32, ..., 3i-1, 3i, ..., 3n-1, 3n), четвертый n-разрядный выход 12, каждый разряд которого 12i, (121, 122, ..., 12i-1, 12i, ..., 12n-1, 12n) подключен к первым входам соответствующих элементов 2ИЛИ-И-НЕ 3i (31, 32, ..., 3i-1, 3i, ..., 3n-1, 3n). Элемент И-НЕ 2 имеет выход 13. Старший элемент 2ИЛИ-И-НЕ 3i (3n) имеет второй вход 14. Выход 15i (15n, ..., 15i, ..., 152) каждого из элементов 2ИЛИ-И-НЕ 3i, кроме 31, подключен к второму входу предыдущего элемента 3i-1 (3n-1, . . ., 3i-1, ..., 31). Выход 151 подключен к первому входу элемента И-НЕ 2. Выходы 4i шины 4 управления (4n, 4n-1, ..., 4i, 4i-1, ..., 42, 41) подключены к четвертым входам соответствующих элементов 2ИЛИ-И-НЕ 3i (31, 32, ..., 3i-1, 3i, ..., 3n-1, 3n).

Делитель частоты работает следующим образом.

На первый вход 5 счетчика 1 поступает сигнал разрешения счета. Второй вход 6 счетчика 1 служит для подачи на него сигнала установки счетчика в начальное нулевое состояние. Третий вход 7 счетчика 1 служит для подачи на него импульсной (тактовой) последовательности с частотой Fo. Четвертый вход 8 счетчика 1 служит для подачи на него сигнала разрешения деления. На первом выходе 9 счетчика 1 формируется сигнал переполнения после поступления на его третий вход 7 последовательности из 2n импульсов частоты Fo. На втором выходе 10 счетчика 1 формируется сигнал, инверсный входной тактовой частоте -  . На третьем выходе 11 счетчика 1 формируются потенциальные относительно частоты Fo сигналы, соответствующие количеству поступивших импульсов на третий вход 7 счетчика 1 в двоичном коде. На четвертом выходе 12 счетчика 1 формируются сигналы, инверсные сигналам на третьем выходе 11 счетчика. На выходе 13 элемента И-НЕ 2 формируется последовательность импульсов Fyза период работы счетчика 1. Цепочка элементов 2ИЛИ-И-НЕ 3i (31, 32, . .., 3i-1, 3i, ..., 3n-1, 3n) служит для получения потенциального относительно частоты Fo сигнала разрешения на выходе 151 младшего элемента 2ИЛИ-И-НЕ 3i (31). Второй вход 14 старшего элемента 2ИЛИ-И-НЕ 3i (3n) используется для расширения разрядности делителя частоты. На шину 4 управления подается n-разрядный двоичный код числа/ задающего коэффициент деления/ причем старший разряд еода числа управления подается на четвертый вход 4n младшего элемента 2ИЛИ-И-НЕ 3i (31)/ младший оазряд кода управления подается на четвертый вход 41 старшего элемента 2ИЛИ-И-НЕ 3i (3n). Средняя частота Fy импульсной последовательности на выходе 13 элемента И-НЕ 2 определяется выражением

. На третьем выходе 11 счетчика 1 формируются потенциальные относительно частоты Fo сигналы, соответствующие количеству поступивших импульсов на третий вход 7 счетчика 1 в двоичном коде. На четвертом выходе 12 счетчика 1 формируются сигналы, инверсные сигналам на третьем выходе 11 счетчика. На выходе 13 элемента И-НЕ 2 формируется последовательность импульсов Fyза период работы счетчика 1. Цепочка элементов 2ИЛИ-И-НЕ 3i (31, 32, . .., 3i-1, 3i, ..., 3n-1, 3n) служит для получения потенциального относительно частоты Fo сигнала разрешения на выходе 151 младшего элемента 2ИЛИ-И-НЕ 3i (31). Второй вход 14 старшего элемента 2ИЛИ-И-НЕ 3i (3n) используется для расширения разрядности делителя частоты. На шину 4 управления подается n-разрядный двоичный код числа/ задающего коэффициент деления/ причем старший разряд еода числа управления подается на четвертый вход 4n младшего элемента 2ИЛИ-И-НЕ 3i (31)/ младший оазряд кода управления подается на четвертый вход 41 старшего элемента 2ИЛИ-И-НЕ 3i (3n). Средняя частота Fy импульсной последовательности на выходе 13 элемента И-НЕ 2 определяется выражением

Fy = Fо· N / 2n, (1) где N=Tn′·2n-1+Tn-1′·2n-1+...+Ti′·2i-1+... +T2′·21+T1′·2 Ti′·2i-1, (2)

Ti′·2i-1, (2)

Ti'={0; 1} - логическое состояние i-х разрядов кода управления.

Логическое выражение для выхода 13 имеет вид

Fy= , (3) где V1 - функция выхода 151.

, (3) где V1 - функция выхода 151.

Схема реализации функции V1 представляет собой итеративную цепочку элементов 2ИЛИ-И-НЕ 3i (фиг. 2а)

→·( +U))˙˙˙)). (4=1)

+U))˙˙˙)). (4=1)

Логическое выражение для выхода 151 при n четном имеет вид (фиг. 2б)

→·( +U))˙˙˙)), (4=2) где U - значение логического сигнала на входе 14 расширения делителя при отсутствии расширения, U=1 (n - нечетное, фиг.2 а) или U=0 (n - четное, фиг.2 б);

+U))˙˙˙)), (4=2) где U - значение логического сигнала на входе 14 расширения делителя при отсутствии расширения, U=1 (n - нечетное, фиг.2 а) или U=0 (n - четное, фиг.2 б);

Ti, - логические состояния i-х разрядов счетчика 1.

- логические состояния i-х разрядов счетчика 1.

В известном устройстве деление частоты осуществляется за счет суммирования n-входовым элементом ИЛИ-НЕ импульсов, вырабатываемых поразрядными элементами И, с количеством входов Mi (i изменяется от 1 до n; Mi изменяется от 3 до i+2). Причем выходы элементов И заводятся параллельно на элемент ИЛИ-НЕ. Аппаратные затраты схемы, содержащей n элементов И и элемент ИЛИ-НЕ, по количеству входов (L1) и по количеству выходов (К1) равны

L1= Mi+n =

Mi+n =  (i+2)+n; (5)

(i+2)+n; (5)

К1=n. (6)

В предлагаемом делителе аппаратные затраты схемы, содержащей n четырехвходовых элементов 2ИЛИ-И-НЕ, по количеству входов (L2) и по количеству выходов (К2) равны

L2=4.n; (7)

K2=n. (8)

Итак, К1=К2=n.

Сравним L1 и L2:

L1-L2=  (i+2)+n-4·n =

(i+2)+n-4·n =  (i+2)-3

(i+2)-3 . (9)

. (9)

Выражение (9) показывает, что во втором случае достигнуто существенное снижение аппаратных затрат.

В известном делителе каждый прямой выход i-го разряда счетчика нагружен на Pi входов элементов И, а каждый инверсный выход разряда счетчика нагружен на один вход одного элемента И. Величина Pi убывает с ростом веса разряда счетчика и равна нулю для самого старшего:

Pi=n-i, где i изменяется от 1 до n.

В предлагаемом делителе каждый инверсный выход и каждый прямой выход разряда счетчика нагружен на один вход одного элемента 2ИЛИ-И-НЕ. В предлагаемом делителе существенно снижается нагрузка на прямые выходы разрядов счетчика.

С целью расширения разрядности предлагаемого делителя частоты необходимо выход расширения первого устройства подсоединить к входу расширения второго устройства, образующего совместно с первым делитель частоты удвоенной разрядности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 2020 |

|

RU2752485C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 2004 |

|

RU2273043C1 |

| Делитель частоты с переменным коэффициентом деления | 2021 |

|

RU2762529C1 |

| Управляемый двигатель частоты | 1985 |

|

SU1325691A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Управляемый делитель частоты следования импульсов | 1980 |

|

SU930682A1 |

| УСТРОЙСТВО ДЛЯ УЧЕТА И КОНТРОЛЯ ПОТРЕБЛЕНИЯ ЭЛЕКТРОЭНЕРГИИ | 1992 |

|

RU2035820C1 |

| Устройство для самонастраивающейся токовой защиты электродвигателя | 1986 |

|

SU1339735A1 |

| Генератор треугольных функций | 1978 |

|

SU720426A1 |

Изобретение относится к автоматике и вычислительной технике, а также к системам автоматического управления и может найти применение в системах числового программного управления, в измерительных и вычислительных устройствах. Цель изобретения - сокращение аппаратурных затрат и уменьшение выходной нагрузки двоичного счетчика. Делитель частоты с переменным коэффициентом деления содержит двоичный счетчик 1, элемент И - НЕ 2, n элементов 2 ИЛИ - И - НЕ 3 и шину 4 управления, соединенные между собой функционально. 2 ил.

ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ, содержащий n-разрядный двоичный счетчик, вход разрешения счета, вход установки в начальное состояние, вход синхронизации, вход разрешения деления, выход переполнения, n-разрядную шину управления и элемент И - НЕ, отличающийся тем, что, с целью сокращения аппаратурных затрат и уменьшения выходной нагрузки двоичного счетчика, в него введены n элементов 2ИЛИ - И - НЕ, причем выход первого элемента 2ИЛИ - И - НЕ соединен с первым входом элемента И - НЕ, второй вход которого соединен с инверсным выходом синхронизации двоичного счетчика, выход элемента И - НЕ является информационным выходом делителя частоты, выход расширения которого соединен с выходом первого элемента 2ИЛИ - И - НЕ, первые входы всех элементов 2ИЛИ - И - НЕ соединены соответственно с инверсными разрядными выходами n-разрядного двоичного счетчика, второй вход i-го элемента 2ИЛИ - И - НЕ (i =  ) соединен с выходом (i + 1)-го элемента 2ИЛИ - И - НЕ, второй вход n-го элемента 2ИЛИ - И - НЕ является входом расширения делителя частоты, третьи входы всех элементов 2ИЛИ - И - НЕ соединены соответственно с прямыми разрядными выходами n-разрядного двоичного счетчика, четвертые входы всех элементов 2ИЛИ - И - НЕ соединены соответственно с n разрядами шины управления.

) соединен с выходом (i + 1)-го элемента 2ИЛИ - И - НЕ, второй вход n-го элемента 2ИЛИ - И - НЕ является входом расширения делителя частоты, третьи входы всех элементов 2ИЛИ - И - НЕ соединены соответственно с прямыми разрядными выходами n-разрядного двоичного счетчика, четвертые входы всех элементов 2ИЛИ - И - НЕ соединены соответственно с n разрядами шины управления.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Канатное устройство для подъема и перемещения сыпучих и раздробленных тел | 1923 |

|

SU155A1 |

| Экспресс-информация | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1994-06-30—Публикация

1990-12-25—Подача