LO

,с

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1988 |

|

SU1737710A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU993451A1 |

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Цифровой фазометр | 1986 |

|

SU1348744A1 |

| Устройство для деления чисел | 1985 |

|

SU1247862A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Устройство для управления синусоидальными вибрациями | 1985 |

|

SU1269112A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

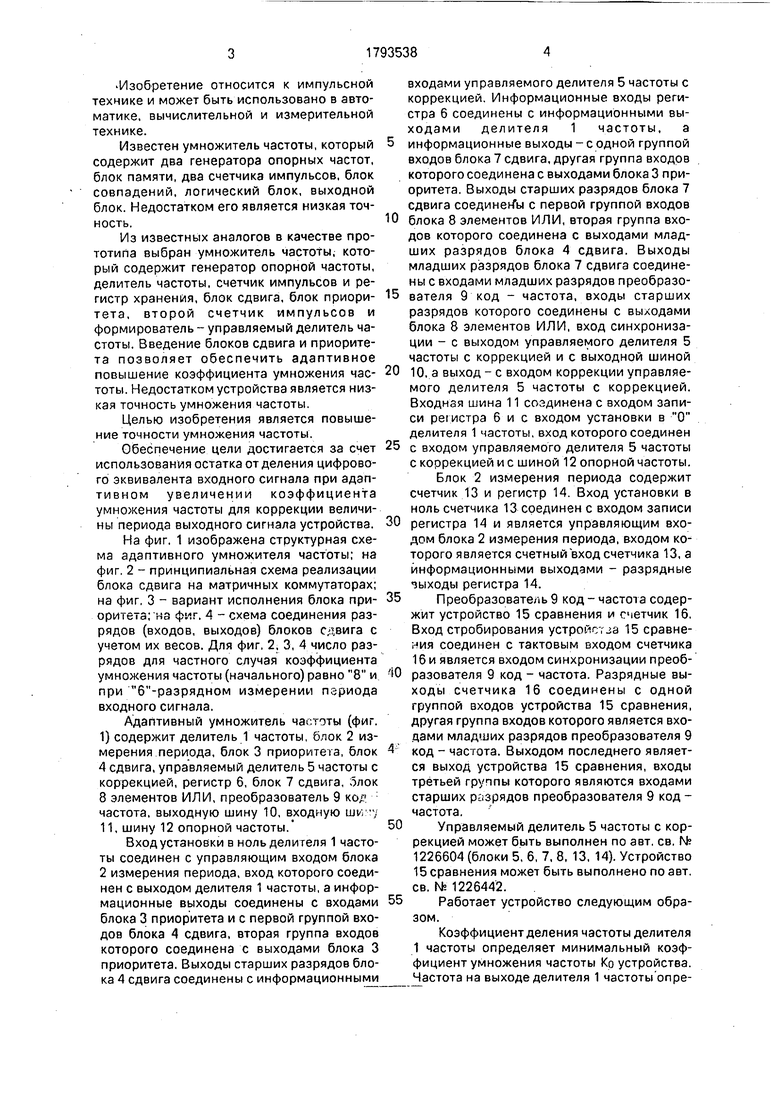

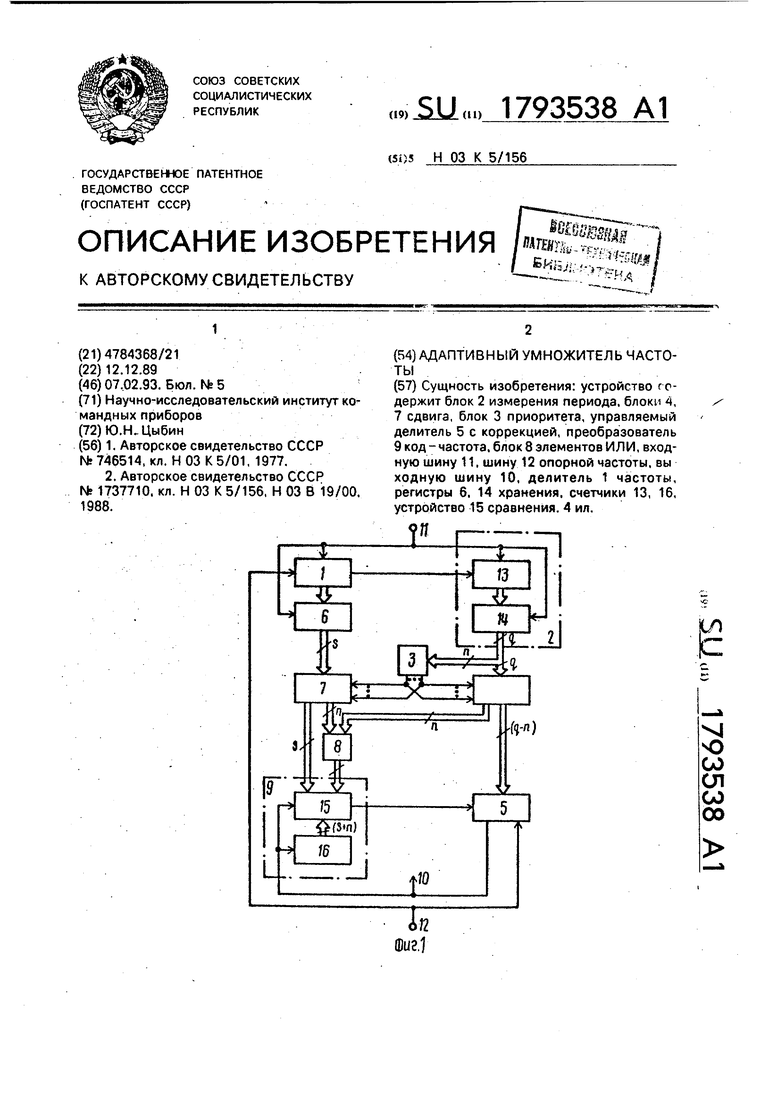

Сущность изобретения: устройство г о- держит блок 2 измерения периода, блоки 4, 7 сдвига, блок 3 приоритета, управляемый делитель 5 с коррекцией, преобразователь 9 код - частота, блок 8 элементов ИЛИ, входную шину 11. шину 12 опорной частоты, вы ходкую шину 10, делитель 1 частоты, регистры 6. 14 хранения, счетчики 13, 16, устройство 15 сравнения. 4 ил. /

VI о со ел

GJ 00

Изобретение относится к импульсной технике и может быть использовано в автоматике, вычислительной и измерительной технике.

Известен умножитель частоты, который содержит два генератора опорных частот, блок памяти, два счетчика импульсов, блок совпадений, логический блок, выходной блок. Недостатком его является низкая точность.

Из известных аналогов в качестве прототипа выбран умножитель частоты, который содержит генератор опорной частоты, делитель частоты, счетчик импульсов и регистр хранения, блок сдвига, блок приоритета, второй счетчик импульсов и формирователь - управляемый делитель частоты. Введение блоков сдвига и приоритета позволяет обеспечить адаптивное повышение коэффициента умножения частоты. Недостатком устройства является низкая точность умножения частоты.

Целью изобретения является повышение точности умножения частоты.

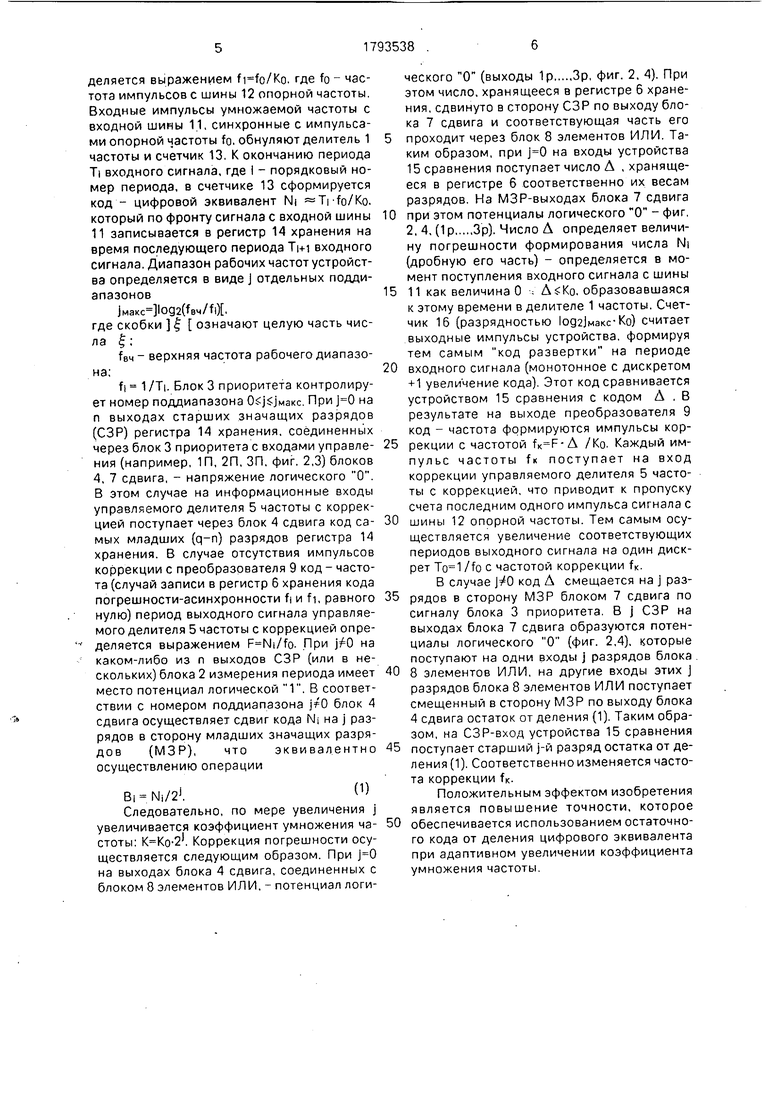

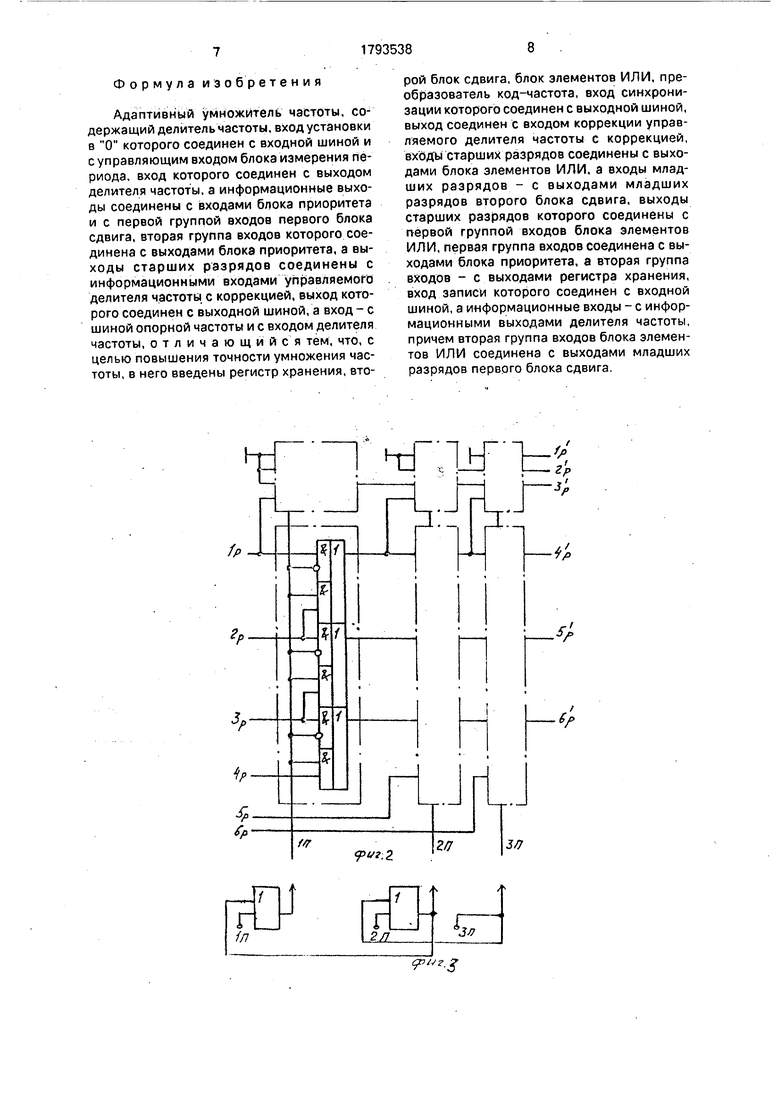

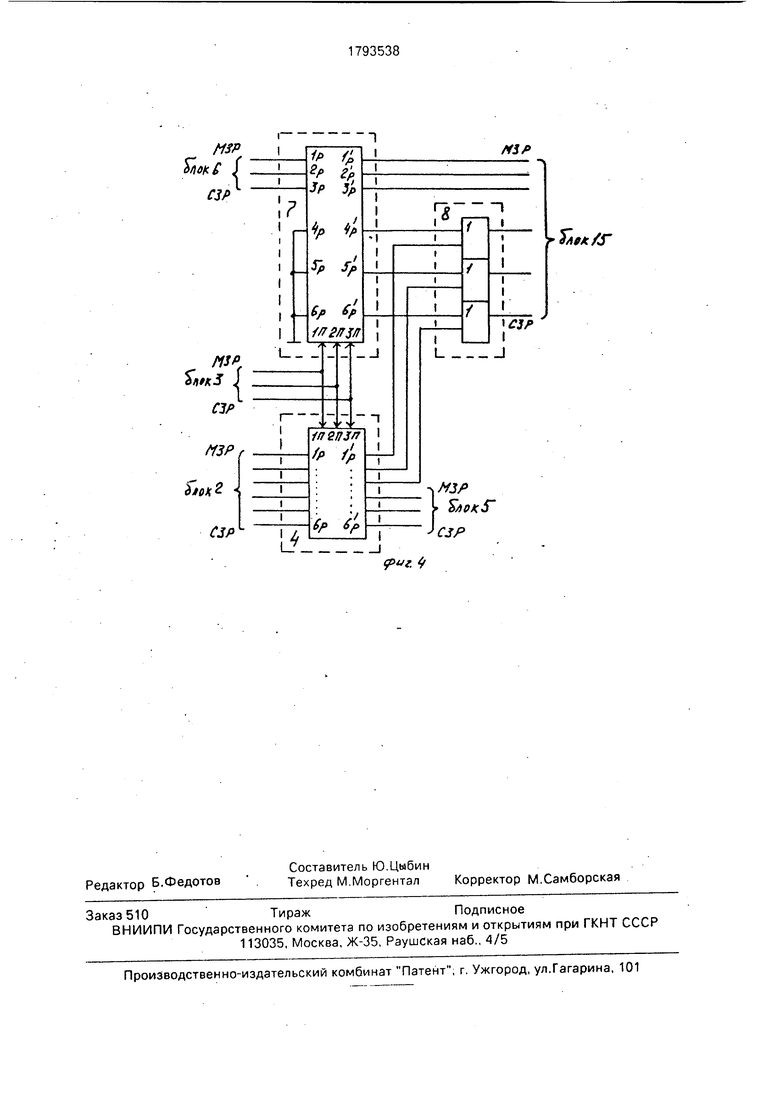

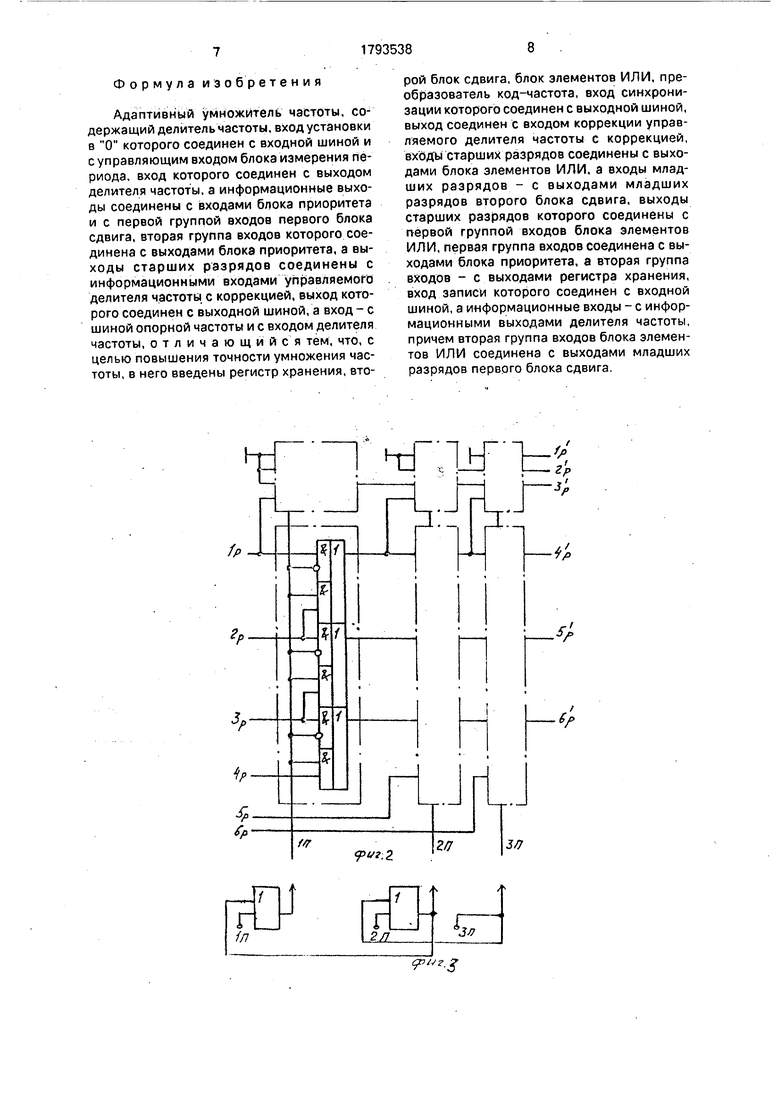

Обеспечение цели достигается за счет использования остатка от деления цифрового эквивалента входного сигнала при адаптивном увеличении коэффициента умножения частоты для коррекции величины периода выходного сигнала устройства. На фиг. 1 изображена структурная схема адаптивного умножителя частоты; на фиг. 2 - принципиальная схема реализации блока сдвига на матричных коммутаторах; на фиг, 3 - вариант исполнения блока приоритета; из фиг. 4 - схема соединения разрядов (входов, выходов) блоков сдвига с учетом их весов. Для фиг, 2, 3, 4 число разрядов для частного случая коэффициента умножения частоты (начального) равно 8 и при т 6 -разрядном измерении периода входного сигнала.

Адаптивный умножитель частоты (фиг. 1) содержит делитель 1 частоты, блок 2 измерения периода, блок 3 приоритета, блок 4 сдвига, управляемый делитель 5 частоты с коррекцией, регистр б, блок 7 сдвига, 5лок 8 элементов ИЛИ, преобразователь 9 код : частота, выходную шину 10, входную ши. -v; 11, шину 12 опорной частоты.

Вход установки в ноль делителя 1 частоты соединен с управляющим входом блока 2 измерения периода, вход которого соединен с выходом делителя 1 частоты, а информационные выходы соединены с входами блока 3 приоритета и с первой группой входов блока 4 сдвига, вторая группа входов которого соединена с выходами блока 3 приоритета. Выходы старших разрядов блока 4 сдвига соединены с информационными

входами управляемого делителя 5 частоты с коррекцией. Информационные входы регистра 6 соединены с информационными выходами делителя 1 частоты, а

информационные выходы - с одной группой входов блока 7 сдвига, другая группа входов которого соединена с выходами блока 3 приоритета. Выходы старших разрядов блока 7 сдвига соединен ы с первой группой входов

блока 8 элементов ИЛИ, вторая группа входов которого соединена с выходами младших разрядов блока 4 сдвига. Выходы младших разрядов блока 7 сдвига соединены с входами младших разрядов преобразо5 вателя 9 код - частота, входы старших разрядов которого соединены с выходами блока 8 элементов ИЛИ, вход синхронизации - с выходом управляемого делителя 5 частоты с коррекцией и с выходной шиной

0 10, а выход - с входом коррекции управляемого делителя 5 частоты с коррекцией. Входная шина 11 соэдинена с входом записи регистра бис входом установки в О делителя 1 частоты, вход которого соединен

5 с входом управляемого делителя 5 частоты

с коррекцией и с шиной 12 опорной частоты.

Блок 2 измерения периода содержит

счетчик 13 и регистр 14. Вход установки в

ноль счетчика 13 соединен с входом записи

0 регистра 14 и является управляющим входом блока 2 измерения периода, входом которого является счетный вход счетчика 13, а информационными выходами - разрядные чыходы регистра 14.

5 Преобразователь 9 код - частота содержит устройство 15 сравнения и счетчик 16, Вход стробирования устройства 15 сравнения соединен с тактовым входом счетчика 16 и является входом синхронизации преоб0 разователя 9 код - частота. Разрядные выходы счетчика 16 соединены с одной группой входов устройства 15 сравнения, другая группа входов которого является входами младших разрядов преобразователя 9

код - частота. Выходом последнего является выход устройства 15 сравнения, входы третьей группы которого являются входами старших разрядов преобразователя 9 код - частота.

0 Управляемый делитель 5 частоты с коррекцией может быть выполнен по авт. св. N; 1226604 (блоки 5, 6, 7, 8, 13, 14). Устройство 15 сравнения может быть выполнено по авт. св. № 1226442.

5 Работает устройство следующим образом.

Коэффициент деления частоты делителя 1 частоты определяет минимальный коэффициент умножения частоты Ко устройства. Частота на выходе делителя 1 частоты определяется выражением f i fo/Ko, где fo - частота импульсов с шины 12 опорной частоты. Входные импульсы умножаемой частоты с входной шины 1.1, синхронные с импульсами опорной частоты fo, обнуляют делитель 1 частоты и счетчик 13. К окончанию периода TI входного сигнала, где I - порядковый номер периода, в счетчике 13 сформируется код - цифровой эквивалент Ni Trfo/Ko. который по фронту сигнала с входной шины 11 записывается в регистр 14 хранения на время последующего периода Ti+i входного сигнала. Диапазон рабочих частот устройства определяется в виде J отдельных подди- апазонов

JMaKC log2(fB4/fl),

где скобки Ј означают целую часть числа Ј;

т8ч - верхняя частота рабочего диапазона:

fi 1 /Т|. Блок 3 приоритета контролирует номер поддиапазона OSJ JMSKC. При на п выходах старших значащих разрядов (СЭР) регистра 14 хранения, соединенных через блок 3 приоритета с входами управления (например, 1П, 2П, ЗП, фиг. 2,3) блоков 4, 7 сдвига, - напряжение логического О. В этом случае на информационные входы управляемого делителя 5 частоты с коррекцией поступает через блок 4 сдвига код самых младших (q-n) разрядов регистра 14 хранения. В случае отсутствия импульсов коррекции с преобразователя 9 код - частота (случай записи в регистр 6 хранения кода погрешности-асинхронности fi и fi, равного нулю) период выходного сигнала управляемого делителя 5 частоты с коррекцией определяется выражением F Ni/fo. При на каком-либо из п выходов СЭР (или в нескольких) блока 2 измерения периода имеет место потенциал логической 1. В соответствии с номером поддиапазона блок 4 сдвига осуществляет сдвиг кода N на j разрядов в сторону младших значащих разрядов (МЗР), что эквивалентно осуществлению операции

Bl Ni/2i.(1) Следовательно, по мере увеличения j увеличивается коэффициент умножения частоты: К Ко-2 . Коррекция погрешности осуществляется следующим образом. При на выходах блока 4 сдвига, соединенных с блоком 8 элементов ИЛИ, - потенциал логического О (выходы 1р,...,3р, фиг. 2, 4). При этом число, хранящееся в регистре 6 хранения, сдвинуто в сторону СЭР по выходу блока 7 сдвига и соответствующая часть его проходит через блок 8 элементов ИЛИ. Таким образом, при на входы устройства 15 сравнения поступает число Д , хранящееся в регистре 6 соответственно их весам разрядов. На МЗР-выходах блока 7 сдвига

0 при этом потенциалы логического О - фиг. 2, 4, (1р,...,3р). Число Л определяет величину погрешности формирования числа NI (дробную его часть) - определяется в момент поступления входного сигнала с шины

5 11 как величина 0 -; . образовавшаяся к этому времени в делителе 1 частоты. Счетчик 16 (разрядностью 1од2 макс-Ко) считает выходные импульсы устройства, формируя тем самым код развертки на периоде

0 входного сигнала(монотонное с дискретом + 1 увеличение кода). Этот код сравнивается устройством 15 сравнения с кодом Д , В результате на выходе преобразователя 9 код - частота формируются импульсы кор5 рекции с частотой /Ко. Каждый импульс частоты f к поступает на вход коррекции управляемого делителя 5 частоты с коррекцией, что приводит к пропуску счета последним одного импульса сигнала с

0 шины 12 опорной частоты. Тем самым осуществляется увеличение соответствующих периодов выходного сигнала на один дискрет /fo с частотой коррекции fK.

В случае код Д смещается на j раз5 рядов в сторону МЗР блоком 7 сдвига по сигналу блока 3 приоритета. В j C3P на выходах блока 7 сдвига образуются потенциалы логического О (фиг. 2,4), которые поступают на одни входы j разрядов блока .

0 8 элементов ИЛИ, на другие входы этих J разрядов блока 8 элементов ИЛИ поступает смещенный в сторону МЗР по выходу блока 4 сдвига остаток от деления (1). Таким образом, на СЗР-вход устройства 15 сравнения

5 поступает старший j-й разряд остатка от деления (1). Соответственно изменяется частота коррекции fie.

Положительным эффектом изобретения является повышение точности, которое

0 обеспечивается использованием остаточного кода от деления цифрового эквивалента при адаптивном увеличении коэффициента умножения частоты.

Формула изобретения

Адаптивный умножитель частоты, содержащий делитель частоты, вход установки которого соединен с входной шиной и с управляющим входом блока измерения периода, вход которого соединен с выходом делителя частоты, а информационные выходы соединены с входами блока приоритета и с первой группой входов первого блока сдвига, вторая группа входов которого соединена с выходами блока приоритета, а выходы старших разрядов соединены с информационными входами управляемого делителя частоты с коррекцией, выход которого соединен с выходной шиной, а вход- с шиной опорной частоты и с входом делителя частоты, отличающийся тем, что, с целью повышения точности умножения частоты, в него введены регистр хранения, втоi-d T tf ljf Ъ

LJ -, I--J t-- Zp

рой блок сдвига, блок элементов ИЛИ, преобразователь код-частота, вход синхронизации которого соединен с выходной шиной, выход соединен с входом коррекции управляемого делителя частоты с коррекцией, входы старших разрядов соединены с выходами блока элементов ИЛИ, а входы младших разрядов - с выходами младших разрядов второго блока сдвига, выходы старших разрядов которого соединены с первой группой входов блока элементов ИЛИ, первая группа входов соединена с выходами блока приоритета, а вторая группа входов - с выходами регистра хранения, вход записи которого соединен с входной шиной, а информационные входы - с информационными выходами делителя частоты, причем вторая группа входов блока элементов ИЛИ соединена с выходами младших разрядов первого блока сдвига.

1pfL

4

ЗР}}

4p4

tf ff

fffMW

W

ар

{

f13P

fffSffJ/7

// If

fro г

CSP

f/ 6/

m/

1 i

i i

l

i i I

C3f

I

L J

I

-l/vj/9 I 5/)

JCJP

фиг. 4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Дискретный умножитель частоты следования импульсов | 1977 |

|

SU746514A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Умножитель частоты | 1988 |

|

SU1737710A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1993-02-07—Публикация

1989-12-12—Подача