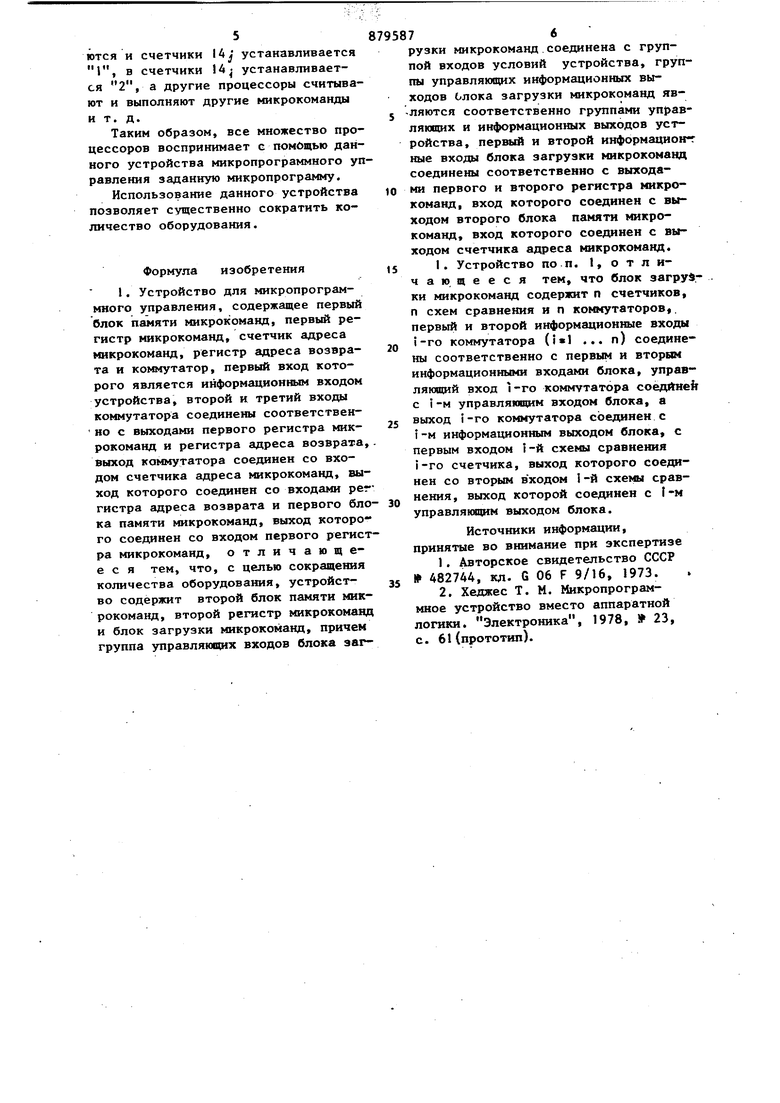

Изобретение относится к области вычислительной техники и может быть использовано- при разработке и конструировании мультимикропроцессорных вычислительных систем класса S1MD. Известно устройство для микропрог раммного управления 1J, в состав кот рого входят два запоминающих блока (в первом содержится адресная информация микрокоманд, а во втором операционные части микрокоманд), два дешифратора адреса, регистр адре са, счетчик микрокоманд и буферный регистр. Из известных устройств наиболее близким по технической сущности к изобретению является устройство для микропрограммного управления 2, содержащее мультиплексор выбора адрес подключенный входами к выходам мультиплексора тест-условия, соединенного с регистром тест-условия, мультиплексора адреса ветвления, соединенного с регистром адреса возврата, и счетчика адреса, соединенный выходом со входом регистра адреса, а входом - с выходом мультиплексора выбора адреса, подклгоченмьм ко входу блока памяти микрокоманд, соединенного выходом со входом регистра микро команд, подключенного шлходом ко входам регистров тест-условия и адреса возврата и мультиплексоров тест-условия и адреса ветвлесшя. Недостатком таких устройств является большой объем оборудования при осуществлении микропрограммногоууправления в мультимикропроцессорных системах класса STMD. Целью изобретения является сокращение количества оборудования. , Поставленная цель достигается тем что устройство для микропрограммного управления, содержащее первьШ блок памяти микрокоманд первый микрокоманд, счетчик адреса микрокоманд регистр адреса возврата и коммутатор, первый вход которого является информационным входом устройства, второй и третий входы коммутатора соединены соответственно с выходами первого регистра микрокоманд и регистра адреса возврата, выход коммутатора соединен со входом счетчика микрокоманд, выход которого соединен со входами регистра адреса возврата и первого блока памяти микр команд, выход которого соединен со входом первого регистра микрокоманд, содержит второй блок -памяти микроманд, второй регистр микрокоманд и блок загрузки микрокоманд. Группа управляющих входов блока загрузки микрокоманд соединена с группой входов условий устройства. Группа уп равляющих информационных выходоэ бло ка загрузки микрокомавд являются соо ветственно группами управлянядих и информационных выходов устройства. Первый н второй информационные входы блока загрузки микрокоманд соединены соответственно с выходами первого и второго регистра микрокоманд, вход которого соединен с выходом вто рого блока памяти микрокоманд, вход которого соединен с выходом счетчика адреса микрдкоманд. Кроме того, блок загрузки микроко манд содержит п счетчиков, п схем уп равления и п коммутаторов. Первый и второй информационные входы -го коммутатора ( 1... п) соединены соответственно с nepB№t и вторым информационными входами блока, управляювщй вход 1-го коммутатора соединен с {-м управляищим входом блока, а i то кутатора соединен с {-м информгщионкым выходом блока, с первьЕМ входом I -и скегол сравнения и с входом 1-го счетчика, выходкоторо го соединен со вторым входом 1-й схемы сравнения, выход которой соеди нен с f-M управляшснм выходом блока;На чертеже представлена структурная схема устройства. Оно содержит коммутатор 1, информационный вход 2 устройства, счетчик адреса микрокоманд 3, регистр ад реса возврата 4, второй 5 и первый 6 блоки микрокоманд, второй 7 и пер: вый 8 регистры микрокоманд, блок 9 загрузки микрокоманд, группу входов 10 условий, группы управляющих и информационных 12 выходов устройства. Блок загрузки микрокоманд 9 содержит коммутаторы счетчи ки i 4 j и схемы сравнения 15п . Устройство работает следующим образом. С информационного входа 2 устрой. ства через коммутатор в счетчик адреса микрокоманд 3 поступает адрес начальной команды микропрограммы, которая считывается из блоков памяти 6,5 в регистры 8,7 и поступает затем на коммутаторы 13п блока 9. При этом счетчики 14,- устанавливаются в О . После этого ветствии с естественным порядком выборки микрокоманд из блоков памяти 6,5 с выходов регистров микрокоманд 8,7 через коммутаторы 13 блока 9 на инфбрмациониые выходь устройства поступают raкpoкoмaнды, которые затем выполняются множеством процессоров. После этого на вход 10 группы коммутатора 13 приходит 1, на выход коммутатора проходит информация с первого информационного входа блока 9,а на вход 10 группы коммутатора - О о При этом на выход коммутатора 13 проходит информация to второго информационного входа блока 9, Таким образом, на информационный выход 12 устройства через регистр микрокоманд 8 поступает информация из первого блока памяти микрокоманд 6, а через регистр микрокоманд 7 - информация с блока памяти микрокоманд 5, В соответствии с размещением микропрограммы в блоках памяти 6, 5 процессоры выполняют те или иные микрокоманды. Далее согласно размещению микропрограммы в блоке 6 одни процессоры выполняют команду блокировки, отключаясь от дальнейшей работы по сигналу блокировки с управлякяцего выхода 11 , при несовпадении, фиксируемом схемой сравнения 15v . Одновременно согласно размещению микропрограммы в блоке 5 другие процессоры выполняют другую микрокоманду. При этом на одни входы 10 группы приходит 1, а на другие входы 10 группы - О. Соответственно на выходы 12j через блок 9 поступает информация из блока памяти микрокоманд 6 или информация из блока па- Мяти 5 и согласно размещению микропрограммы одни процессоры считывают и выполняют микрокоманды и команду блокировки, по которой они отключа- ются и счетчики устанавливается I, в счетчики А устанавливается 2, а другие процессоры считывают и выполняют другие микрокоманды и т. д.

Таким образом, все множество процессоров воспринимает с помощью данного устройства микропрограммного уп равления заданную микропрограмму.

Использование данного устройства позволяет существенно сократить количество оборудования.

Формула изобретения

I. Устройство для микропрограммного управления, содержащее первый блок памяти микрокоманд, первый регистр микрокоманд, счетчик адреса микрокоманд, регистр адреса возврата и коммутатор, первый вход которого является информационным входом устройства, второй и третий входы коммутатора соединены соответственно с выходами первого регистра микрокоманд и регистра адреса возврата, выход коммутатора соединен со входом счетчика адреса микрокоманд, выход которого соединен со входами per гистра адреса возврата и первого бло ка памяти микрокоманд, выход которого соединен со входом первого регист ра микрокоманд, отличающееся тем, что, с целью сокращения количества оборудования, устройство содержит второй блок памяти микрокоманд, второй регистр микрокоманд и блок загрузки микрокоманд, причем группа управляюощх входов блока заг795876

рузки микрокоманд соединена с группой входов условий устройства, группы управляющих информационных выходов Слока загрузки микрокоманд яв5 -ляются соответственно группами управляющих и информационных выходов устройства, первый и второй информационг ные входы блока загрузки микрокоманд соединены соответственно с выходаto ми первого и второго регистра микрокоманд, вход которого соединен с выходом второго блока памяти микрокоманд, вход которого соединен с выходом счетчика адреса микрокоманд.

)5 Устройство по п. 1, отличающееся тем, что блок загруйки микрокоманд содержит п счетчиков, п схем сравнения и п коммутаторов первый и второй информационные входы

2Q i-ro коммутатора («1 ... п) соединены соответственно с первым и вторвш информационными входами блока, управляющий вход 1-го коммутатора соедйней с i-м управляяяцим входом блока, а

25 выход i-ro коммутатора соединен.с i-м информационным выходом блока, с первым входом i-и схемы сравнения i-ro счетчика, выход которого соединен со вторым входом 1 -и схемы сравJ- нения, выход которой соединен с t-м управлякшщм выходом блока.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 35 482744, кд. G 06 F 9/16, 1973.

2.Хеджес Т. М. Микропрограммное устройство вместо аппаратной логики. Электроника, 1978, 23, с. 61(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1981 |

|

SU962944A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1798781A1 |

| Микропрограммное устройство управления | 1980 |

|

SU955060A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

Авторы

Даты

1981-11-07—Публикация

1980-03-21—Подача