Изобретение относится к вычислительной технике и может быть использовано при разработке и конструировании мультимикропроцессорных вычислительных систем.

Известно устройство микропрограммного управления, в которое входят дв.а запоминающих блока (в первом содержится адресная информация микрокоманд, а во втором - операционные части микрокоманд), два дешифратора адреса, регистр адреса, счетчик микрокоманд и буферный регистр, причем первый запоминающий блок подключен последовательно к второму запоминающему блоку через счетчик микрокоманд и дешифратор адреса и соединен с входом буферного регистра ij.

Недостатками устройства являются невозможность работы с микроподпрограммами, а также большое количество оборудования, необходимое для организации микропрограммного управления по одной программе в мультипроцессорных системах.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее первый и второй блоки памяти микрокоманд, первый и второй регистры микрокоманд.

блок загрузки микрокоманд, счетчик адреса микрокоманд, регистр адреса возврата и коммутатор выбораадреса, первый вход которого является информационным входом устройства, а второй и третий выходы соединены соответственно с выходами первого регистра микрокоманд и регистра адреса возврата, выход коммутатора выбо10ра адреса соедине с входом счетчика адреса микрокоманд, выход которого соединен с входом регистра адре са возврата и входами первого и второго блоков памяти микрокоманд, выхо15ды которых соединены с входами первого и второго регистров микрокоманд, ВЫХО.ДЫ которых являются первыми и вторыми входами блока загрузки микрокоманд, входы условий устрой20ства являются управляющими блока загрузки, а информационные управляющие выходы блока загрузки информационными и управляющими выходами устройства f2j.

25

Недостатком данного устройства также является большой объем оборудования для реализации блока загрузки микрокоманд, состоящего из ; и коммутаторов выбора блока памяти,

30 J м счетчиков и VI схем сравнения.

Цель изобретения - сокращение ко. ичества оборудования.

Поставленная цель достигается тем что в устройство микропрограммного управления, содержащее первый и второй блоки памяти микрокоманд, первый и второй регистры микрокоманд, yi коммутаторов выбора блока памяти, счетчик адреса микрокоманд, регистр адреса возврата и коммутатор адреса первый вход которого является адресным входом устройства, а второй и третий входы соединены соответственно- с выходами первого регистра микрокоманд и регистра адреса возврата, выход коммутатора адреса соединен с информационным входом счетчика адреса микрокоманд, выход которого соединен с информационным входом регистра адреса возврата и адресными входами первого и второго блоков памяти микрокоманд, выходы которых соединены соответственно с информационными входами первого и второго регистров микрокоманд, выходы которых подключены к -первым и вторым информационным входам и коммутаторов выбора блока памяти, управляющие входы которых являются входами условий устройства, а выходы - информационными выходами устройства, йведен VI -разрядный блок памяти магазинного типа, информационные входы которого подключены к входам условий устройства, управляющий вход - к выходу первого регистра микрокоманд, а выходы являются управляющими выходами устройства.

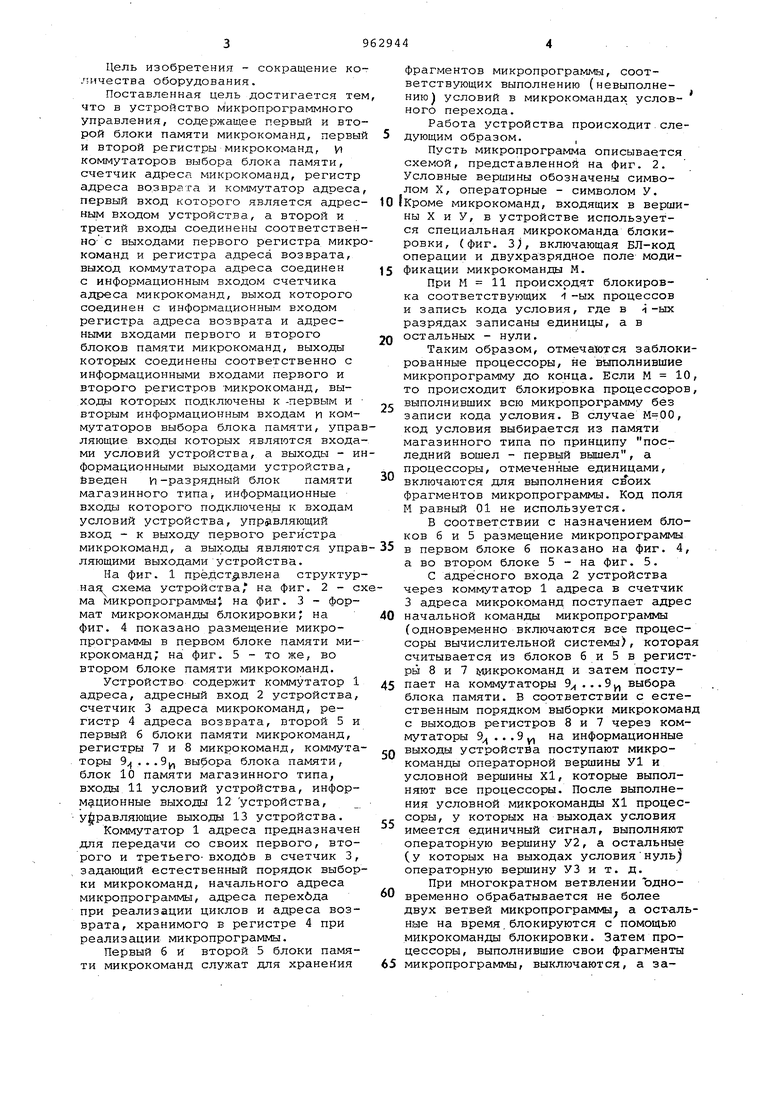

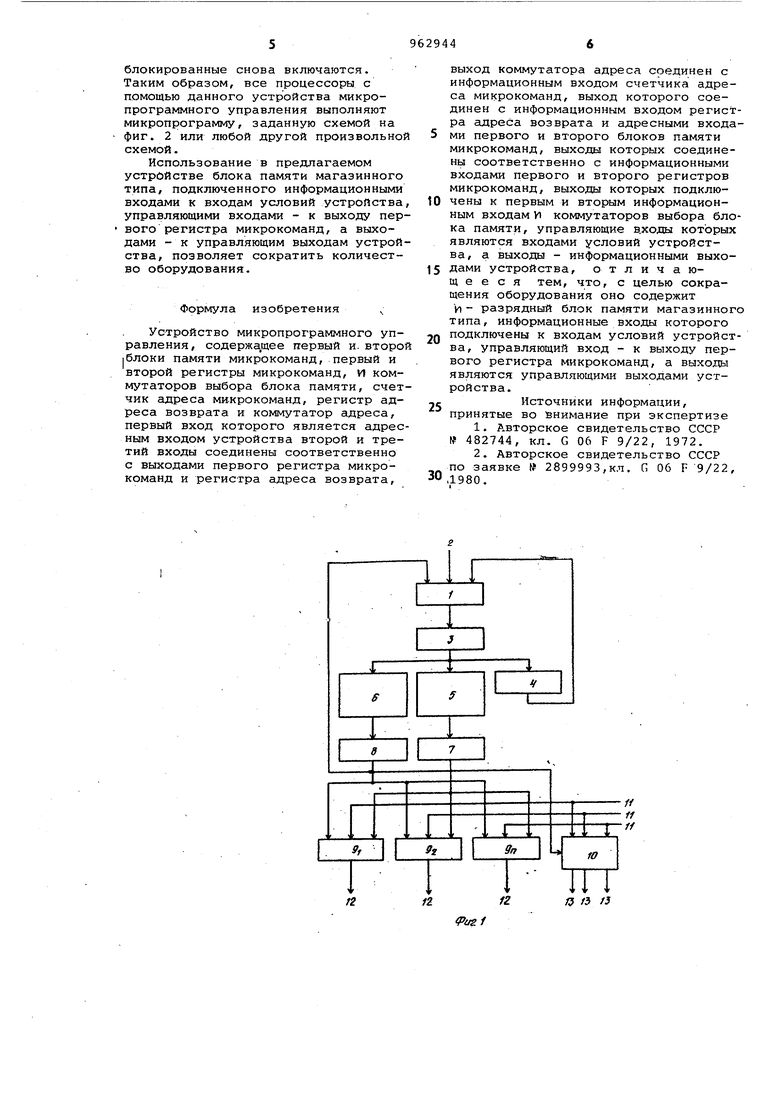

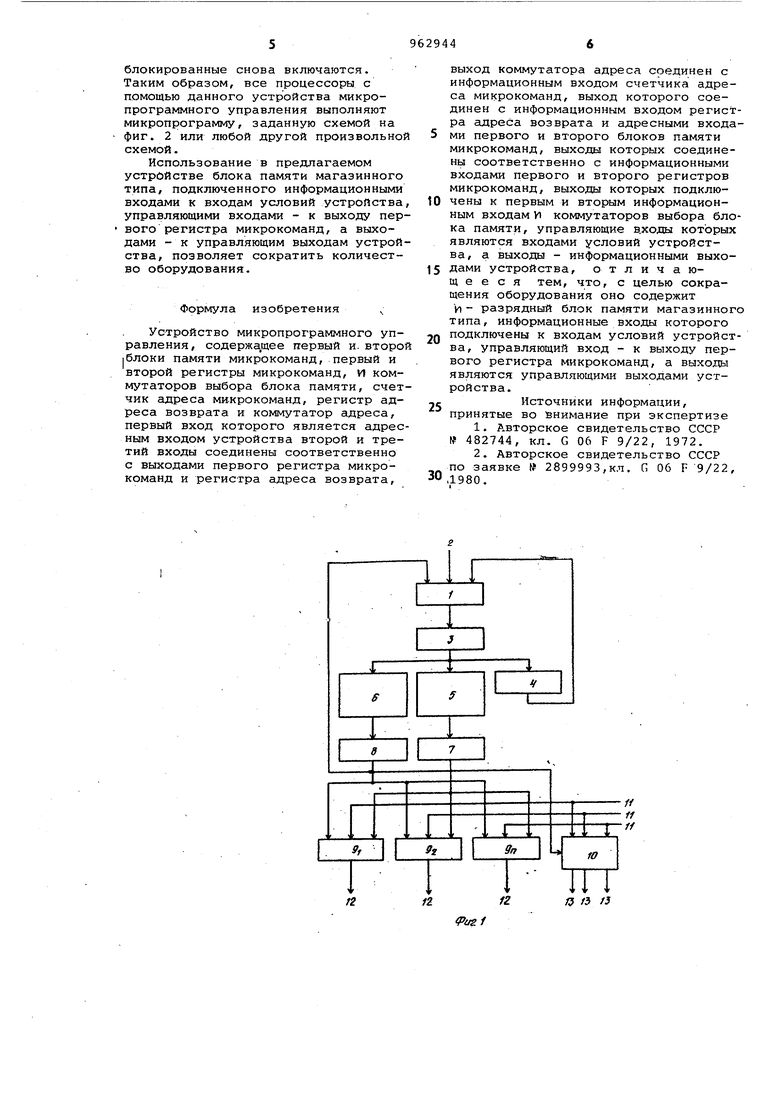

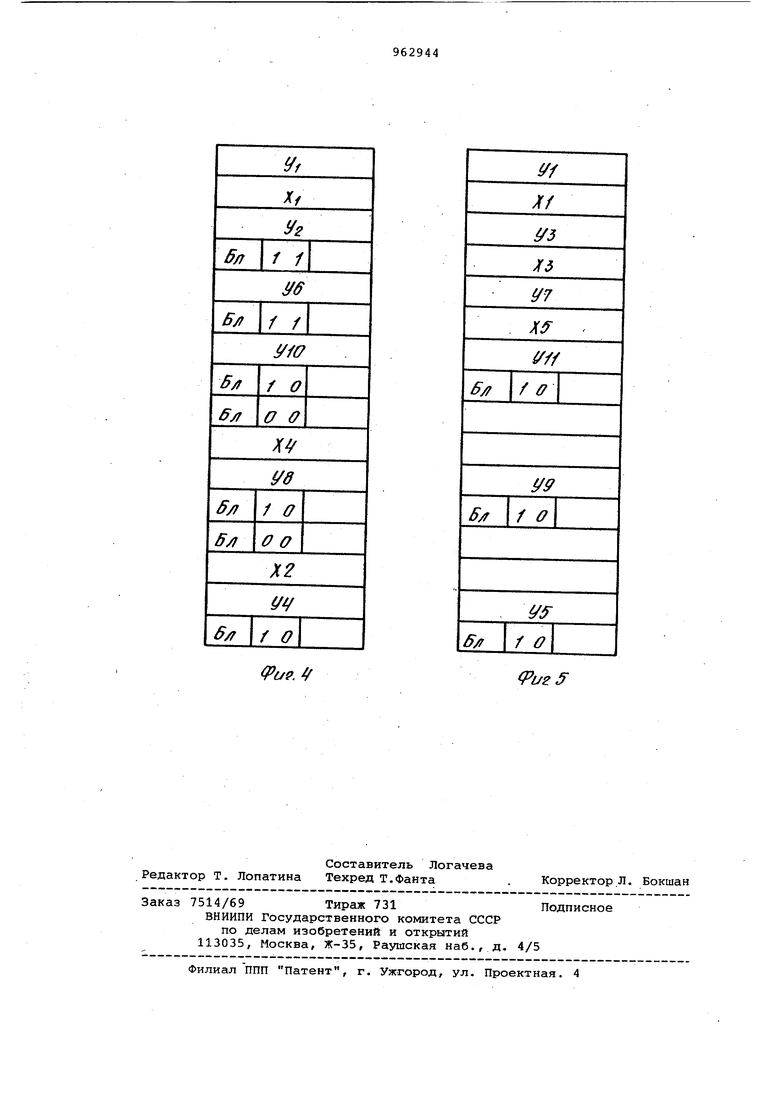

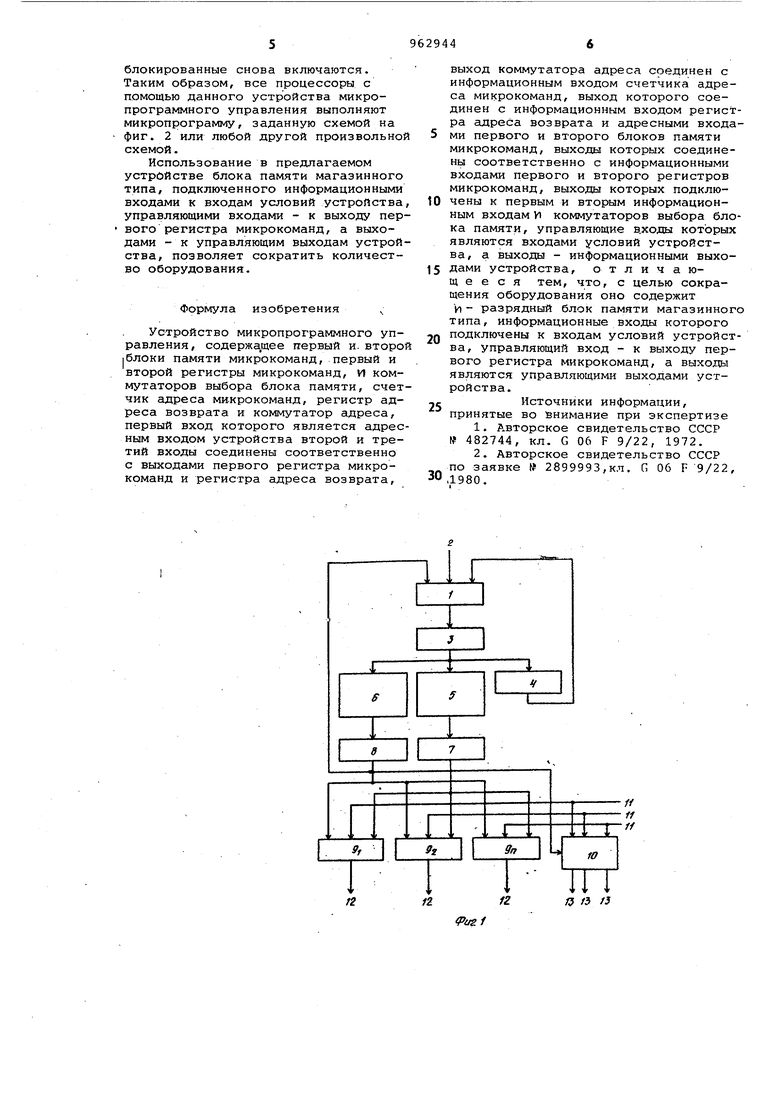

На фиг. 1 прёдст.влена структурная схема устройства на фиг. 2 - сх ма микропрограммы на фиг. 3 - формат микрокоманды блокировки; на фиг. 4 показано размещение микропрограммы в первом блоке памяти микрокоманд; на фиг. 5 - то же, во втором блоке памяти микрокоманд.

Устройство содержит коммутатор 1 адреса, адресный вход 2 устройства, счетчик 3 адреса микрокоманд, регистр 4 адреса возврата, второй 5 и первый б блоки памяти микрокоманд, регистры 7 и 8 микрокоманд, коммутаторы 9...9j вырора блока памяти, блок 10 памяти магазинного типа, входы 11 условий устройства, информ ционные выходы 12 устройства, управляющие выходы 13 устройства.

Коммутатор 1 адреса предназначен для передачи со своих первого, второго и третьего- входив в счетчик 3, задающий естественный порядок выборки микрокоманд, начального адреса микропрограммы, адреса перехбда при реализации циклов и адреса возврата, хранимого в регистре 4 при реализации микропрограммы.

Первый 6 и второй 5 блоки памяти микрокоманд служат для хранения

фрагментов микропрограммы, соответствующих выполнению (невыполнению условий в микрокомандах условного перехода.

Работа устройства происходит следующим образом.

Пусть микропрограмма описывается схемой, представленной на фиг. 2. Условные вершины обозначены символом X, операторные - символом У. (кроме микрокоманд, входящих в вершины X и У, в устройстве используется специальная микрокоманда блокировки, (фиг. 3), включающая БЛ-код операции и двухразрядное поле модификации микрокоманды М.

При М 11 происходят блокировка соответствующих -t -ых процессов и запись кода условия, где в -i-ьлх разрядах записаны единицы, а в остальных - нули.

Таким образом, отмечаются заблокированные процессоры, не вьтолнившие микропрограмму до конца. Если М 10 то происходит блокировка процессоров выполнивших всю микропрограмму без записи кода условия. В случае , код условия выбирается из памяти магазинного типа по принципу последний вошел - первый вышел, а процессоры, отмеченные единицами, включаются для выполнения своих фрагментов микропрограммы. Код поля М равный 01 не используется.

В соответствии с назначением блоков 6 и 5 размещение микропрограммы в первом блоке б показано на фиг. 4, а во втором блоке 5 - на фиг. 5.

С адресного входа 2 устройства через коммутатор 1 адреса в счетчик 3 адреса микрокоманд поступает адрес начальной команды микропрограммы (одновременно включаются все процессоры вычислительной системы), котора считывается из блоков б и 5 в регистры 8 и 7 дакрокоманд и затем поступает на коммутаторы 9 9и выбора блока памяти. В соответствии с естественным порядком выборки микрокоман с выходов регистров 8 и 7 через коммутаторы 9 ... 9 на информационные выходы устройства поступают микрокоманды операторной вершины У1 и условной вершины XI, которые выполняют все процессоры. После выполнения условной микрокоманды Х1 процессоры, у которых на выходах условия имеется единичный сигнал, выполняют операторную вершину У2, а остальные (у которых на выходах условиянульj операторную вершину УЗ и т. д.

При многократном ветвлении одновременно обрабатывается не более двух ветвей микропрограммы а остальные на время,блокируются с помощью микрокоманды блокировки. Затем процессоры, выполнившие свои фрагменты микропрограммы, выключаются, а заблокированные снова включаются. Таким образом, все процессоры с помощью данного устройства микропрограммного управления выполняют микропрограмму, заданную схемой на фиг. 2 или любой другой произвольной схемой.

Использование в предлагаемом устройстве блока памяти магазинного типа, подключенного информационными входами к входам условий устройства управляющими входами - к выходу первого регистра микрокоманд, а выходами - к управляющим выходам устройства, позволяет сократить количество оборудования.

Формула изобретения

Устройство микропрограммного управления, содержа,щее первый и. второй |блоки памяти микрокоманд, первый и второй регистры микрокоманд, vi коммутаторов выбора блока памяти, счетчик адреса микрокоманд, регистр адреса возврата и коммутатор адреса, первый вход которого является адресным входом устройства второй и третий входы соединены соответственно с выходами первого регистра микрокоманд и регистра адреса возврата.

выход коммутатора адреса соединен с информационным входом счетчика адреса микрокоманд, выход которого соединен с информационным входом регистра адреса возврата и адресными входами первого и второго блоков памяти микрокоманд, выходы которых соединены соответственно с информационными входами первого и второго регистров микрокоманд, выходы которых подклю0чены к первым и вторым информационным входам У1 коммутаторов выбора блока памяти, управляющие в.ходы которых являются входами условий устройства, а выходы - информационными выхо5 Дами устройства, отличающееся тем, что, с целью сокращения оборудования оно содержит и - разрядный блок памяти магазинного типа, информационные входы которого подключены к входам условий устройст0ва, управляющий вход - к выходу первого регистра микрокоманд, а выходы являются управляющими выходами устройства.

Источники информации,

5 принятые во йнимание при экспертизе

1.Авторское свидетельство СССР № 482744, кл. G 06 F 9/22, 1972.

2.Авторское свидетельство СССР по заявке 2899993,кл. G 06 F 9/22,

,1980.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1980 |

|

SU879587A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1151962A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Устройство для восстановления работы процессора | 1984 |

|

SU1191910A1 |

| Устройство управления каналами | 1972 |

|

SU545983A1 |

| Микропрограммное устройство управления | 1980 |

|

SU955060A1 |

| Микропрограммный процессор | 1978 |

|

SU741269A1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042190C1 |

| Микропрограммное устройство управления | 1982 |

|

SU1156071A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

/2/г

Г5 1Ъ 13

44ig/

Howm

6/} I /у I

.3

Uff.

f Xf У5 )(5 У7

JL. //

f ff

6/f

f О

5/f

/ О

fPueff

Авторы

Даты

1982-09-30—Публикация

1981-01-28—Подача