(54) ЦИФРОВОЙ СИНТЕЗАТОР ФУНКЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор функций | 1976 |

|

SU596977A1 |

| Функциональный генератор | 1979 |

|

SU809125A1 |

| СИСТЕМА ЦИФРОВОГО СТЕРЕОФОНИЧЕСКОГО РАДИОВЕЩАНИЯ | 1991 |

|

RU2019041C1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

| ЦИФРОВАЯ СИСТЕМА РАДИОВЕЩАНИЯ | 1992 |

|

RU2048704C1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Устройство для управления вентильным преобразователем | 1984 |

|

SU1185545A1 |

| СИСТЕМА ЦИФРОВОГО ТЕЛЕВИДЕНИЯ | 2001 |

|

RU2208917C2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 1999 |

|

RU2163380C1 |

I

Изобретение относится к oGjiacrvi автоматики, а именно, к электронным устройствам, предназначенным для работы в контуре управления прочностными испытательными установками.

В основном изобретении по авт. ев, № 596977 описан цифровой синтезатор функций, и.спользуемый для работы в контуре упрэмгения .прочностными испытательными установками. Этот цифровой синтезатор вырабатывает аналоговые управляющие сигналы синусоидальной. пилообразной и трапецеидальной формы, а также сложнофункциональные аналоговые сигналы, изменяющиеся по програмлге от электронной вычислительной машины ЭВМ, Кроме того, данный синтезатор функции позволяет изменять амплитуду, форму и фазу выходных аналоговых управляющих сигналор для каждого независимого функционального канала управления.

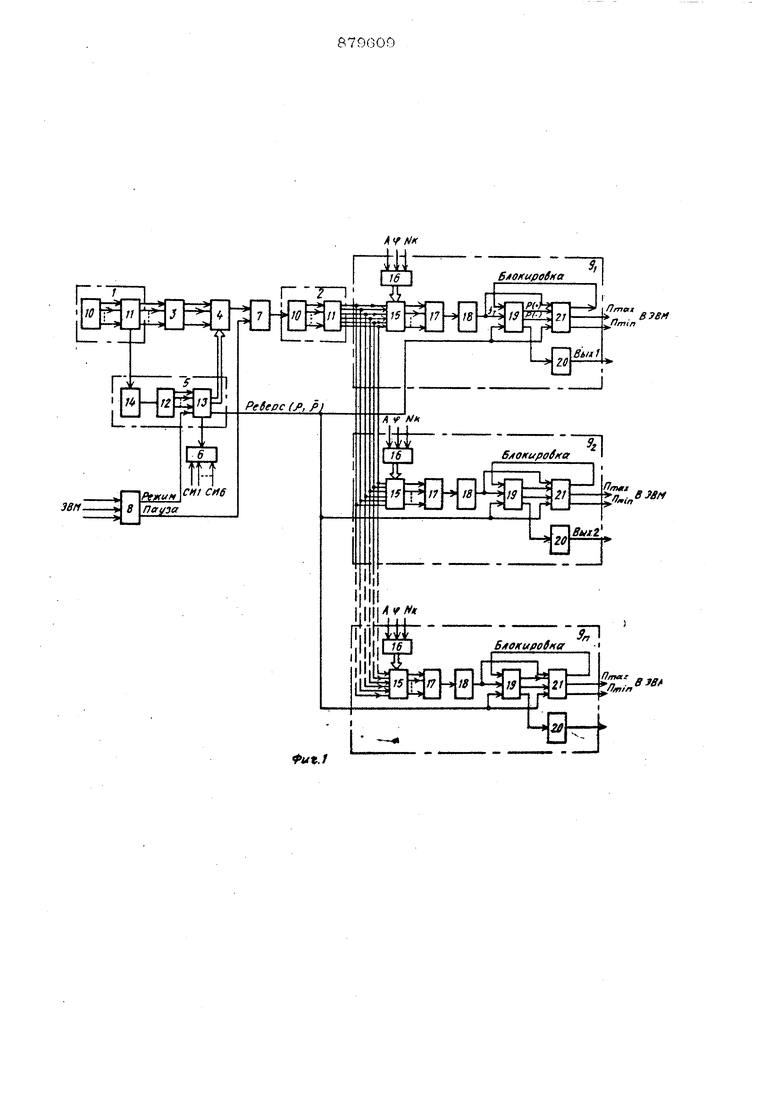

Данный синтезатор функций содержит формирователь серий имлульсов, вход которого является входом задающей частоты

.синтезатора, а выходы через блок формирования комбинаций серий икшульсов coe-j динены с соответствующими одноименными входами блока выборки серий импульсов, управляющие входы которого подключены к соответствующим утфавляюшим вы. ходам программного блока, первый управляющий вход которого подключен к одног1менном.у выходу формирователя серий WMпульсов, а второй - к выходу режима ре10гистра режима.

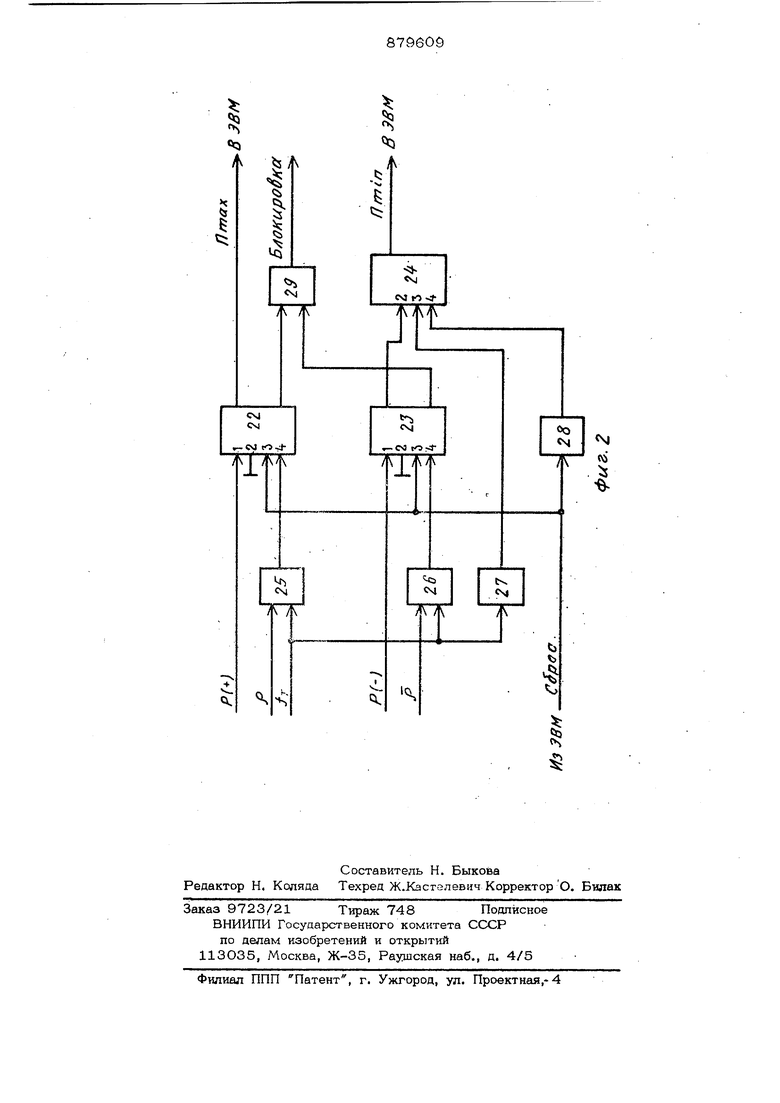

Выход блока выборки серии ит отульсов через схему И, к второму входу которой подключен выход Пауза регистра режима, соединен со вторым формтфователем

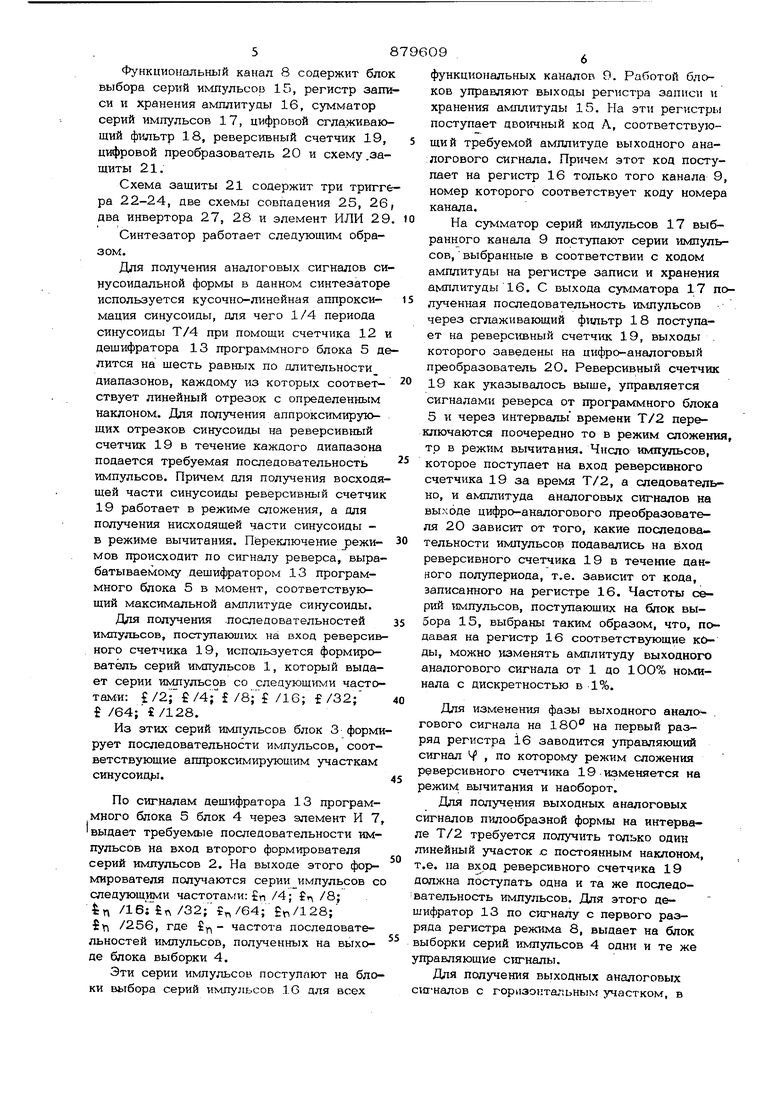

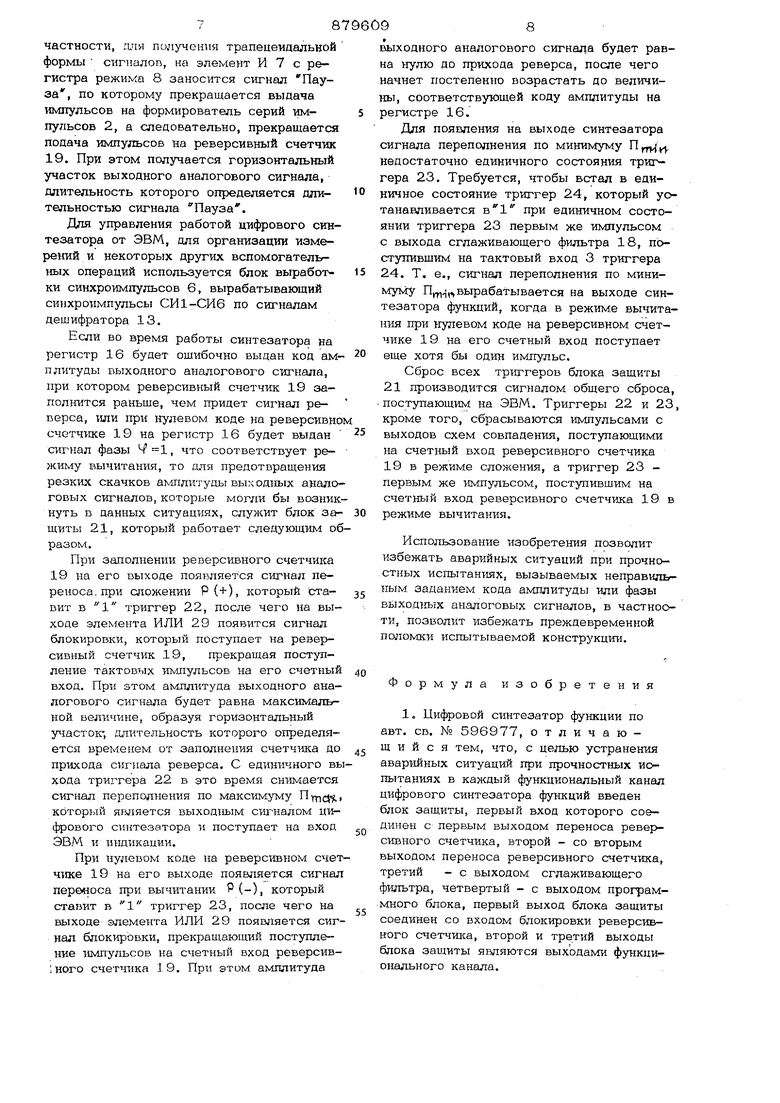

15 серий г1мпульсов, служащим для H3Mejieния амплитуды выходных аналоговых сигналов. Выходы второго формирователя серий и шульсов соединены с одноименными входами всех ф нкциональных каналов, вхо20ды реверса которых объединены и подключены к однот-гменному выходу программного блока, а выходы являются функциональными выxoдa ra синтезатора. 38 Кажаый функциональный канал имеет свой блок выбора серий имлульсов, сумматор серий им1тульсов, сглаживающий фильтр, реверсивный счетчик, цифро-аналоговый преобразователь, а также регистр записи и хранения амплитуды, входы задания амплитуды фазы и номера канала которого являются соответствующими входами функционального канала, а выходы соединены с управляющими входами блока выборки серий импульсов, входы последовательностей импульсов которого подключе ны к одноименным входам функционального канала, а выходы - к одноименным входам сумматора, серий импульсов, выход ко торого через сглаживающий фильтр соединен со счетным входом реверсивного счет чика, вход реверса которого подключен к одноименному входу функционального канала, а выход соединен со входом цифро-ана логоБого преобразователя, выход которого является выходом функционального канала. Недостатком данного синтезатора яв- ляется то, что при неправильном задании кода амплитуды или фазы могут произойти резкие скачки амплитуды выходных аналоговых сигналов, которые могут привести к аварии при проведении испытаний. Так, например, гфи задании кода a шлитуды больше 1ОО%, при котором реверсивный счетчик заполнится раньше, чем гфидет сигнал реверса, переключающий сложения на режим вычитания, про изойдет сброс счетч1жа в йулевое состояние. При этом произойдет скачок амплиту ды выходного аналогового сигнала из максимума в мгшимум, что может гфивести к аварии при проведении прочностных испытаний. Если же при нулевом коде на таыходах реверсивного счетчика на регистр записи и хранения амплитуды . подать код О, а сигнал фазы Ч 1, что соответствует режиму вычиташгя, то при отсутствии защиты произойдет скачок амплитуды выходного аналогового сигнала из мин 1мума в максимум, что также может привести к аварии при испытаниях. Цепью изобретения является устранение аварийных ситуаций при прочностных испытаниях, выявляемых негфавильным заданием кода амплитуды или фазы выходных аналоговых сигналов. Для достижения поставленной цели в цифровой синтезатор в каждый функциональный канал цифрового синтезатора функций введен блок защиты, первый вход которого соединен с первым выходом пере9носа реверсивного счетчика,, второй - со вторым выходом переноса реверсивного счетчика, третий - с выходом сглаживающего фильтра, четвертый - с выходом программного блока, первый выход блока защиты соединен со входом блокировки реверсивного счетчика, второй и третий выходы блока защиты являются выходами функционального канала. Кроме того, блок защиты содержит триггеры, элементы И, элемент НЕ и элемент ИЛИ, причем уотановочный вход первого триггера явл ется первым входом блока защиты, вход сброса первого триггера соединен с выходом первого элемента И, первый вход которого является четвертым входом блока защиты, установочный вход второго триггера является вторым входом блока защиты, вход сброса второго триггера соединен с выходом второго элемента И, первый вход которого является пятым входом блока защиты, информационные входы первого и второго триггеров подключены к шине нулевого потенциала, тактовые входы первого и второго триггеров и вход второго элемента НЕ объединены и подключены к шине общего сброса, нулевые выходы первого и второго триггера подключены к соответствующему входу элемеета ИЛИ, выход которого является первым выходом блока защиты, единичный выход, второго триггера соединен с информационным входом третьего триггера, тактовый вход которого подключен к выходу первого элемента НЕ, .вход которого соединен со вторыми входами элементов И и являются третьим входом блока защиты, вход сброса третьего триггера соединен с выходом второго элемента НЕ, единичные выходы первого и третьего триггеров являются вторым и третьим выходшу1и блока защиты. На фиг. 1 изображена структурная схема цифрового синтезатора функций; на фиг. 2 - блок защиты. Цифровой синтезатор функций содержит формкровате ш серий импульсов 1 и 2, блок формирования комбинаций серий импульсов 3, блок выборки серий импульсов 4, программный блок 5, блок выработки синхроимпульсов 6, элемент И 7, регистр, режима 8 и функциональные каналы Ц -9, Формирователи серий импульсов 1 и 2 содержат двоичный счетчик 10 и блок логических ключей 11. Программный блок 5 содержит реверсивный счетчик 12, дешифратор 13 и логический ключ 14. Функциональный канал 8 содержит блок выбора серий импульсов 15, регистр запи си и хранения амплитуды 16, сумматор серий импульсов 17, цифровой сгла.живак щий фильтр 18, реверсивный счетчик 19, цифровой преобразователь 20 и схему .защиты 21. Схема защиты 21 содержит три тригге ра 22-24, две схемы совпадения 25, 26 два инвертора 27, 28 и элемент ИЛИ 29 Синтезатор работает следующим образом. Для получения аналоговых сигналов си нусоидальной формы в данном синтезаторе используется кусочно-линейная аппроксимация синусоиды, для чего 1/4 периода синусоиды Т/4 при помощи счетчика 12 и дешифратора 13 программного блока 5 де лится на шесть равных по длительности диапазонов, каждому из которых соответствует линейный отрезок с определенным наклоном. Для получения аппроксимирующих отрезков синусоиды на реверсивный счетчик 19 в течение каждого диапазона подается требуемая последовательность импульсов. Причем для получения восходящей части синусоиды реверсивный счетчик 19 работает в режиме сложения, а для получения нисходящей части синусоиды в режиме вычитания. Переключение режимов происходит по сигналу реверса, вырабатываемому дешифратором 13 программного блока 5 в момент, соответствующий максимальной амплитуде синусоиды. Для получения .последовательностей импульсов, поступающих на вход реверсивного счетчика 19, используется формирователь серий импульсов 1, который выдает серии импульсов со следующими частотам-и: /16; /32; /64;€ /128. Из этих серий импульсов блок 3 форми рует последовательности импульсов, соответствующие аппроксимирующим участкам синусоид з1. По сигналам дешифратора 13 программного блока 5 блок 4 через элемент И 7 выдает требуемые последовательности импульсов на вход второго формирователя серий импульсов 2. На выходе этого формирователя получаются серии импульсов со следующ1ши частотами: п /4; г, /8; Чп /32;г„/64; п/128; $V /256, где iy - частота последовательностей импульсов, полученных на выходе блока выборки 4. Эти серии имлульсов поступают на блоки выбора серий импульсов 10 для всех функциональных каналов 9. Работой блоков управляют выходы регистра записи и хранения амплитуды 15. На эти регистры поступает двоичный код А, соответствующий требуемой амплитуде выходного аналогового сигнала. Причем этот код поступает на регистр 16 только того канала 9, номер которого соответствует коду номера канала. На сумматор серий импульсов 17 выбранного канала 9 поступают серии кмпульгсов, выбранные в соответствии с кодом амплитуды на регистре записи и хранения амплитуды 16. С выхода сумматора 17 полученная последовательность икшульсов через сглаживающий фильтр 18 поступает на реверсивный счетчик 19, выходы . которого заведены на цифро-аналоговый преобразователь 2О. Реверсивный счетчик 19 как указывалось выше, управляется сигналами реверса от программного блока 5 и через интервалы времени Т/2 переключаются поочередно то в режим, сложения, то в режим вычитания. Число импульсов, которое поступает на вход реверсивного счетчика 19 за время Т/2, а следовательно, и амплитуда аналоговых сигналов на выходе цифро-аналогового преобразователя 20 зависит от того, какие последовательности импульсов подавались на вход реверсивного счетчика 19 в течение данного полупериода, т.е. зависит от кода, записанного на регистре 16. Частоты серий тгмпульсов, поступаюших на блок выоора 15, выбраны таким образом, что, подавая на регистр 16 соответствующие , можно изменять амплитуду выходного аналогового сигнала от 1 до 100% номинала с дискретностью в 1%. Для изменения фазы выходного аналоового сигнала на 180 на первый разяд регистра 1б заводится управляющий игнал Ч , по которому режим сложения еверсивного счетчика 19 изменяется на ежим вычитания и наоборот. Для получения выходных аналоговых игналов пилообразной формы на интервае Т/2 требуется получить только один инейный участок с постоянным наклоном, .е. па вход реверсивного счетчика 19 олжна поступать одна и та же последоательность импульсов. Для этого деифратор 13 по сигналу с первого разяда регистра режима 8, выдает на блок ыборки серий импульсов 4 одни и те же правляющие сигналы. Для получения выходных аналоговых иг-налов с горизонтальным участком, в

частности, сшя получения трапецеидальной формы сигналов, на элемент И 7 с регистра режима 8 заносится сигнал Пауза, по которому прекращается выдача импульсов на формирователь серий импульсов 2, а следовательно, прекращается подача импульсов на реверсивный счетчик 19. При этом получается горизонтальный участок выходного аналогового сигнала, длительность которого определяется длительностью сигнала Пауза.

Для управления работой цифрового синтезатора от ЭВМ, для организации измерений и некоторых других вспомогательных операций используется блок выработки синхроимпульсов 6, вырабатывающий синхроимпульсы СИ1-СИ6 по сигналам дешифратора 13.

Если во время работы синтезатора на регистр 16 будет ошибочно выдан код амплитуды выходного аналогового сигнала, при котором реверсивный счетчик 19 заполнится раньше, чем придет сигнал реверса, или при нулевом, коде на реверсивно счетчт-же 19 на регистр 16 будет выдан сигнал фазы Ч 1, что соответствует ре- жиму вычитания, то для предотвращения резких скачков амплитуды выходных аналоговых сигналов, KOTOpi ie могли бы возникнуть в данных ситуациях, служит блок защиты 21, который работает следующим образом.

При заполнении реверсивного счетчика 19 на его выходе появляется сигнал переноса, при сложении Р (+), который стаBvrr в 1 триггер 22, после чего на выходе элемента ИЛИ 29 появится сигнал блокировки, который поступает на реверсивный счетчик 19, прекращая поступление тактовых импульсов на его счетный вход. При этом амплитуда выходного аналогового сигнала будет равна максимальной величине, образуя горизонтальный участок-, длительность которого определяется временем от заполнения счетчика до прихода сигнала реверса. С единичного выхода триггера 22 в это время снимается сигнал пepeпoлнeнvIя по максимуму Tntif который является выходным сш-налом цифрового cviHTGsaTopa и поступает на вход ЭВМ и индикации.

При нулевом коде на реверсивном счетчике 19 на его выходе появляется сигнал пере«оса при вычитании Р{-), который ставит в 1 триггер 23, после чего на выходе элемента ИЛИ 29 появляется сигнал блокировки, прекращающий поступление импульсов на счетный вход реверсив; ного счетчика 19. При этом амплитуда

выходного аналогового сигнала будет равна угулю до прихода реверса, после чего начнет постепенно возрастать до величины, соответствующей коду амплитуды на регистре 16.

Для пояЕшения на выходе синтезатора сигнала переполнения по минимуму недостаточно единичного состояния триггера 23. Требуется, чтобы встал в единичное состояние триггер 24, который уотанавливается в при единичном состоянии триггера 23 первым же импульсом с выхода сглаживающего фильтра 18, поступившим на тактовый вход 3 триггера 24. Т. е., сигнал переполнения по минимуму ,,, вырабатывается на выходе синтезатора функций, когда в режиме вычитания при 1улевом коде на реверсивном счетчике 19 на его счетный вход поступает еще хотя бы один имхгульс.

Сброс всех триггеров блока защиты 21 производится сигналом общего сброса, поступающим на ЭВМ. Триггеры 22 и 23 кроме того, сбрасываются импульсами с выходов схем совпадения, поступающими на счетный вход реверсивного счетчика 19 в режиме сложения, а триггер 23 первым же 1мпульсом, поступившим на счетный вход реверсивного счетчика 19 в режиме вычитания.

Использование изобретения позволит избежать аварийных ситуаций при прочностных испытаниях, вызываемых неправильгным заданием кода амплитуды или фазы выходных аналоговых сигналов, в частности, позволит избежать преждевременной поломки испытываемой конструкции.

Формула изобретения

Л.п

Авторы

Даты

1981-11-07—Публикация

1980-03-28—Подача