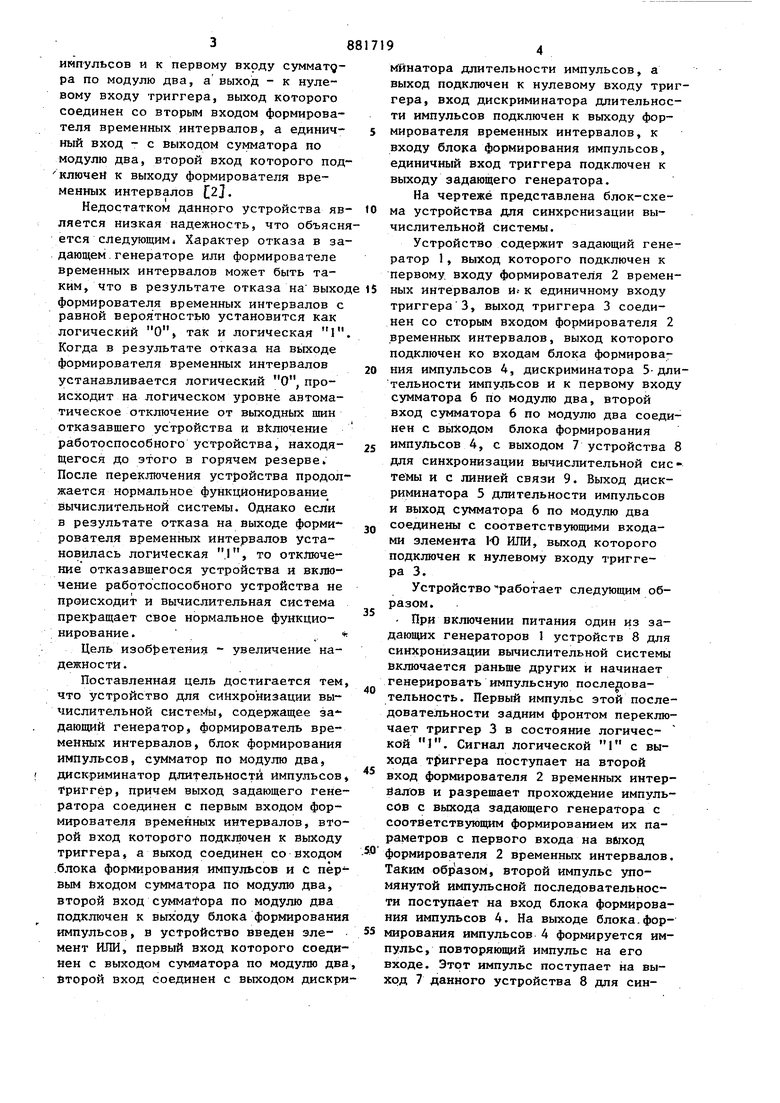

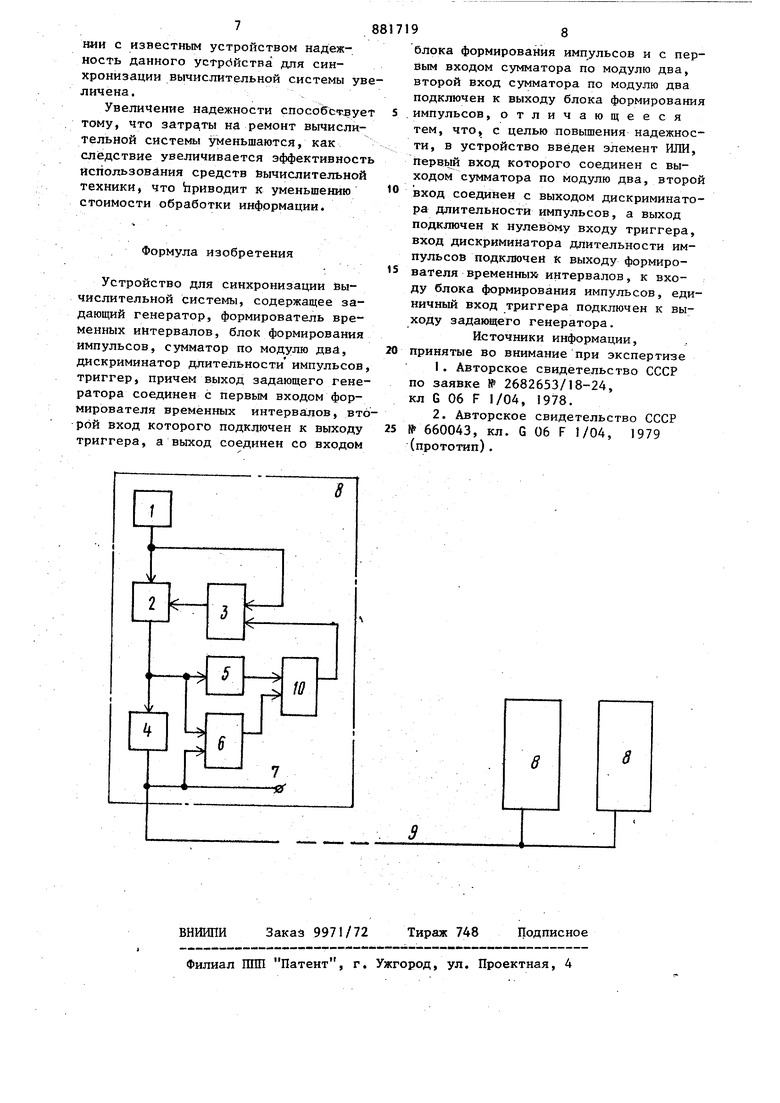

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах тактового питания вычислительных комплексов на базе перестраиваемых однородных структур, а также многомашинных вычислительных комплексов. Известно устройство для синхронизации вычислительной системы, которое содержит задающий генератор, фор мирователь временных интервалов, согласующий блок, сумматор по модулю два, триггер и счетчик. Синхронизация осуществляется таким образом, чт при отказе задающего генератора или формирователя временных интервалов, когда на выходе формирователя времен ных интервалов устанавливается О, формирование тактовых импульсов в выходных шинах начинает осуществлять ся от задающего генератора другого устройства для синхронизации, находя щегося до этого в горячем резерве СП Недостатком известного устройства является низкая надежность, так как при отказе задающего генератора или формирователя временных интервалов, когда на выходе последнего устанавливается логическая I, формирование тактовых импульсов в выходных шинах прекращается. Наиболее близким по технической сущности является устройство для синхронизаци группы блоков обработки данных, содержащее задающий генератор, выход которого подключен к первому входу формирователя временных интервалов, второй вход которого соединен с выходом триггера, а выход со входом согласующегося блока. Устройство содержит также сумматор по модулю два, дискриминатор длительности импульсов, представляющий из себя последовательно соединенные интегратор и пороговый блок, вход дискриминатора дтительности импульсов подключен к выходу блока формирования импульсов и к первому входу сумматдра по модулю два, а выход - к нулевому входу триггера, выход которого соединен со вторым входом формирователя временных интервалов, а единичный вход - с выходом сумматора по модулю два, второй вход которого под ключей к выходу формирователя временных интервалов 2J. Недостатком данного устройства яв ляется низкая надежность, что объясн ется следующим. Характер отказа в за дающем . генераторе или формирователе временных интервалов может быть таким, что в результате отказа на выхо формирователя временных интервалов с равной вероятностью установится как логический О, так и логическая 1 Когда в результате отказа на выходе формирователя временных интервалов устанавливается логический О, происходит на логическом уровне автоматическое отключение от выходных шин отказавшего устройства и включение работоспособного устройства, находящегося до этого в горячем резерве После переключения устройства продол жается нормальное функционирование вычислительной системы. Однако если в результате отказа на выходе формирователя временных интервалов установилась логическая .I, то отключение отказавшегося устройства и включение работоспособного устройства не происходит и вычислительная система прекращает свое нормальное функционирование. , Цель изоб{)етения - увеличение надежности. Поставленная цель достигается тем что устройство для синхронизации вычислительной системы, содержащее задающий генератор, формирователь временных интервалов, блок формирования импульсов, сумматор по модулю два, дискриминатор длительности импульсов триггер, причем выход задающего гене ратора соединен с первым входом формирователя временных интервалов, вто рой вход которого подколочен к выходу триггера, а выход соединен со входом блока формирования импульсов и с пер вым йходом сумматора по модулю два, второй вход сумматора по модулю два подключен к выходу блока формировани импульсов, в устройство введен элемент ИЛИ, первый вход которого соеди нен с выходом сумматора по модулю дв второй вход соединен с выходом дискр минатора длительности импульсов, а выход подключен к нулевому входу триггера, вход дискриминатора длительности импульсов подключен к выходу формирователя временных интервалов, к входу блока формирования импульсов, единичный вход триггера подключен к выходу задающего генератора. На чертеже представлена блок-схема устройства для синхронизации вычислительной системы. Устройство содержит задающий генератор 1, выход которого подключен к первому, входу формирователя 2 временных интервалов и-- к единичному входу триггера 3, выход триггера 3 соединен со сторым входом формирователя 2 временных интервалов, выход которого подключен ко входам блока формирования импульсов 4, дискриминатора 5-длительности импудьсов и к первому входу сумматора 6 по модулю два, второй вход сумматора 6 по модулю два соединен с выходом блока формирования импульсов 4, с выходом 7 устройства 8 для синхронизации вычислительной сие темы и с линией связи 9. Выход дискриминатора 5 длительности импульсов и выход сумматора 6 по модулю два соединены с соответствующими входами злемента Ю ИЛИ, выход которого подключен к нулевому входу триггера 3, Устройство работает следующим образом, - При включении питания один из задающих генераторов 1 устройств 8 для синхронизации вычислительной системы включается раньше других и начинает генерировать импульсную последовательность. Первый импульс зтой последовательности задним фронтом переключает триггер 3 в состояние логической 1. Сигнал логической 1 с выхода триггера поступает на второй вход формирователя 2 временных интервалов и разрешает прохождение импульсов с выхода задающего генератора с соответствующим формированием их параметров с первого входа на выход формирователя 2 временных интервалов. Таким образом, второй импульс упомянутой импульсной последовательности поступает на вход блока формирования импульсов 4. На выходе блока.формирования импульсов 4 формируется импульс, повторяющий импульс на его входе. Этот импульс поступает на выход 7 данного устройства 8 для син5хронизации вычислительной системы и через линию 9 на выход 7 других устройств 8 для синхронизации. Поскольку логические сигналы на первом и втором входах сумматора 6 по модулю два данного устройства 8 совпадают, на выходе сумматора 6 по модулю два будет логический О. Дискриминатор длительности импульсов формирует на своем выходе также логический О, поскольку длительность единичных сиг налов на его входах не превьшает установленных значений. Отсутствие лог ческой 1 на входах элемента 10 ИЛИ приводит к отсутствию информации на нулевом входе триггера 3. Триггер 3 продолжает оставаться в состоянии логической I. Аналогично поступают на выходы 7 устройств 8 для синхрони зации вычислительной системы третий, четвертый и т.д. импульсы упомянутой импульсной последовательности. Если задающий генератор 1 данного устройства 8 оказался менее инициативным и начал генерировать при вклю чении питания импульсов последовательность не первым, то импульс с инициативного задающего генератора I поступает на второй вход сумматора 6 по модлую два, когда на первом входе этого сумматора будет логический О Несовпадение логических сигналов на входах сумматора 6 по модулю два при водит к формированию на его выходе логической 1. Эта логическая 1 поступает через элемент 10 ИЛИ на ну левой вход триггера 3 и переключает его в состояние логической О или, если триггер 3 к этому моменту находится в состоянии логического О, запрещает ему переключение в состояние логической 1. Для организации нормального функционирования устройства 8 можно использовать К-триггер в качестве нулевого входа - вход R, а в качестве единичного - вход С, при этом на входе J и К должны быть поданы соответственно логическая 1 и логический О. В этом случае нулевой -Входлмеет больший приоритет, чем единичный, и переключение триггера в 1 происходит только в том случае, когда информация на установочном (нулевом) входе отсутствует. Если в промежутках между импульсами, действующими на нулевом входе триггера 3, произошло переключение его в 1, то к моменту действия импульса на первом входе формирователя 2 вре96менных интервалов триггер 3 сбрасывается импульсами инициативного устройства 8, поступающими на нулевой вход триггера 3 из линии сйязи 9, и прохозгдение импульсов на выход формировате- ля 2 временных интервалов запрещается. Таким образом, импульсы устчройств 8 с менее инициативными задающими ге нераторами I в линию связи 9 поступать не будут. Если в результате отказа электронных компонентов схем на выходе формирователя 2 временных интервалов инициативного устройства 8 формируется постоянный логический О, то одно из работоспособных устройств 8 захватывает инициативу. Триггер этого устройства не сбрасывается в О и единичный сигнал с его выхода разрешает прохождение импульсов задающего генератора 1 в линию связи 9 и на выходе 7 устроств 8 для синхронизации вычислительной системы. В отличие от известного устройства данное устройство 8 для синхронизации вычислительной системы позволяет сохранить работоспособность вычисли-уельной системы, если в результате отказа электронных компонентов схем на выходе формирователя 2 временных интервалов устанавливается постоянно уровень логической 1. Дискриминатор 5 длительности импульсов определяет, когда длительность сигнала логической f на выходе формирователя 2 временных интервалов превышает устанрвленное значение. Если это произошло, то на выходе дискриминатора 5 длительности импульсов формируется логическая 1, которая поступает через элемент 10 ИЛИ на нулевой вход .триггера 3, устанавливает этот триггер в логический О. Нулевой сигнал с выхода триггера 3, действуя на втором входе формирователя 2 временных интервалов, запрещает формирование на его выходе логической 1. При этом предполагается, что работоспособность формирователя 2 временнь1х интервалов по второму входу при упоминавшемся отказе компонентов не нарушается. После установления на выходе формирователя 2 временных интервалов логического О происходит переключение устройств 8.с изменени ем их инициативы, что ранее уже рассматривалось. Вычислительная система продолжает свое нормальное функционирование. Таким образом, в сравне7НИИ с известным устройством надежность данного устройства для синхронизации вычислительной системы уве личена. Увеличение надежности способствует тому, что затраты на ремонт вычислительной системы уменьшаются, как следствие увеличивается эффективность ИСПОЛЬЗОВАНИЯ средств вычислительной техники, что приводит к уменьшению стоимости обработки информации. Формула изобретения Устройство для синхронизации вычислительной системы, содержащее задающий генератор, формирователь временных интервалов, блок формирования импульсов, сумматор по модулю два, дискриминатор длительности импульсов триггер, причем выход задающего генератора соединен с первым входом формирователя временных интервалов, вто рой вход которого подключен к выходу триггера, а выход соединен со входом 98 блока формирования импульсов и с первым входом сумматора по модулю два, второй вход сумматора по модулю два подключен к выходу блока формирования импульсов, отличающееся тем, что с целью повышения надежности, в устройство введен элемент ИЛИ, первый вход которого соединен с выходом сумматора по модулю два, второй вход соединен с выходом дискриминатора длительности импульсов, а выход подключен к нулевому входу триггера, вход дискриминатора длительности импульсов подключен к выходу формирователя временных- интервалов, к входу блока формирования импульсов, единичный вход триггера подключен к выходу задающего генератора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке № 2682653/18-24, кл G 06 F 1/04, 1978. 2.Авторское свидетельство СССР № 660043, кл. G 06 F 1/04, 1979 (прототип).

8

8

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации блоков вычислительной системы | 1979 |

|

SU898408A1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1983 |

|

SU1092744A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ПАРАМЕТРОВ НАПРЯЖЕНИЯ | 1990 |

|

RU2018147C1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство для синхронизации вычис-лиТЕльНОй СиСТЕМы | 1978 |

|

SU809133A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для сопряжения цифровой вычислительной машины | 1987 |

|

SU1444793A1 |

| Устройство для синхронизации | 1980 |

|

SU941976A1 |

Авторы

Даты

1981-11-15—Публикация

1980-02-13—Подача