Изобретение относится к дискретной автоматике и вычислительной техники и может быть использовано в системах синхронизации вычислительных машин. Известно устройство синхронизации двух параллельно работающих блоков обработки данных 1. Недостатком этого устройства является его низкая надежность, так как при выходе из строя датчика тактовых сигналов одного из блоков работа всего комплекса нарушается. Известно устройство синхронизации нескольких вычислительных машин, которое содержит генератор, выход которого подключен к первому входу формирователя временных интервалов, второй вход которого соединен с выходом триггера, а выход - со входом согласующего блока, счетчик, схему выработки импульсов сброса счетчика 12. Недостатком этого устройства является то, что при выходе его из строя работоспособность этой машины наруша ется. Быстродействие устройства огра ничено, так как частота генератора должна в 2 раз превышать тактовую частоту машины, где п - число разрядов счетчика. Наиболее близкое к предлагаемому является устройство для синхронизации группы блоков обработки данных, содержащее генератор, формирователь временных интервалов, согласующий блок, сумматор по модулю два, дискриминатор импульсов по длительности, выполненный на интегрирующем звене и пороговом элементе, триггер. Выход генератора подключен к информационному входу формирователя временных интервалов, выход формирователя временных интервалов подключен ко входу согласуквдего блока и ко входу сумматора, другой вход сумматора соединен с выводом согласующего блока. Выход сумматора подключен к первому входу триггера, второй вход триггера соединен с выходом дискриминатора импульсов по длительности, вход которого подключен к выходу согласующего блока. Выход триггера нагружен на управлякядйй вход формирователя временных интервалов 3. . Недостатком этого устройства является то, что оно реализует однофазную систему тактового питания. Большинство современных вычислительных машин используют для синхронизации

работы блоков многофазные системы тактового питания.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения возможности формирования многофазного сигнала.

Поставленная цель достигается тем что в устройство для синхронизации блоков вычислительной системы, содержащее генератор, первый сумматор по модулю два, дискриминатор импульсов по длительности, первый триггер, формирователь временных интервалов, причем выход дискриминатора импульсов по длительности соединен с нулевым входом первого триггера, выход которого соединен с управляющим входом формирователя временных интервалов , первый выход которого соединен с первым информационным входом согласующего блока и с первым входом первого сумматора по модулю два, второй вход которого соединен с первым выходом согласующего блока, содержит формирователь фаз, второй триггер, коммутатор, второй сумматор по модулю два, элемент ИЛИ, причем выход генератора соединен со входом формирователя фаз, первый и второй выходы которого соединены соответственно с первым и вторым информационными входами формирователя временных интервалов и коммутатора, управляющий вход коммутатора соединен с выходом второго триггера, а выход коммутатора соединен ,с единичным входом первого триггера, второй выход формирователя временных интервалов соединен со вторым входом согласующего блока и с первым входом второго сумматора по модулю два, первый и второй выходы согласующего блока соединены соответственно с единичным и нулевым входами второго триггера, выходами устройства и вторыми входами второго и первого сумматоров по модулю два соответственно, выходы сумматоров по модулю два соединены с входами элемента ИЛИ, выход которого соединен со входом дискриминатора импульсов по длительности.

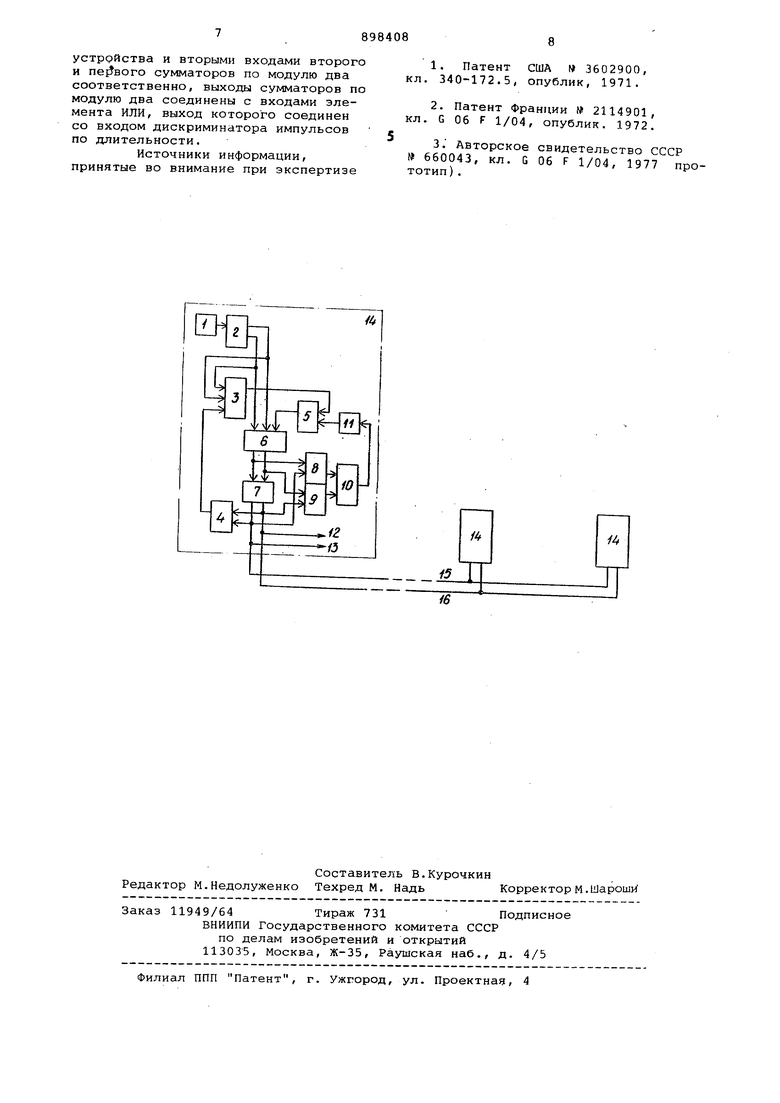

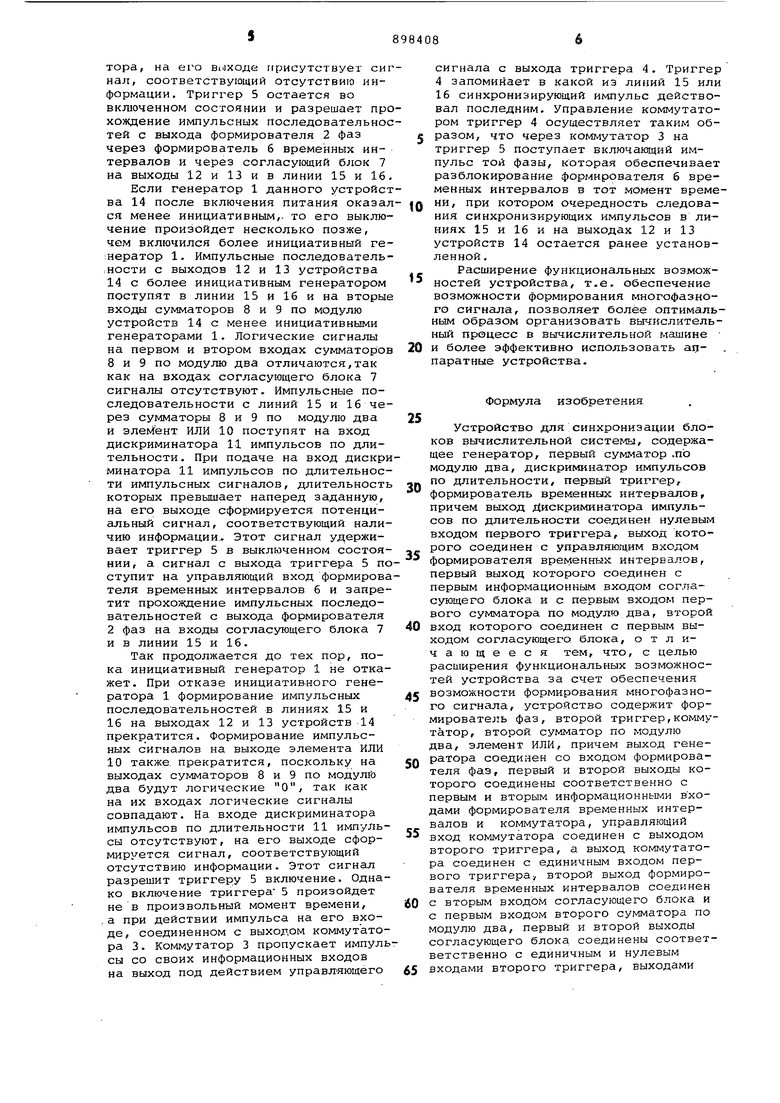

На чертеже представлена блок-схема устройства для синхронизации блоков вычислительной системы.

Устройство содержит генератор 1, выход которого соединен со входом формирователя 2 фаз, выходы которог соединены с первым и вторым входами коммутатора 3, третий вход которого соединен с выходом первого триггера 4, а выход коммутатора 3 соединен с первым входом второго триггера 5, выход которого соединен с управляющим входом формирователя б временны интервалов.

Выходы формирователя б временных интервалов соединены с соответствующими входами согласующего блока 7

с первыми входами первого 8 и второго 9 сумматоров, по модулю два соответственно. Вторые входы этих сумматоров соединены с соответствующими выходами согласующего блока 7, выходы которого соединены с первым и вторым входами триггера 4 соответственно. Выходы сумматоров 8 и 9 по модулю два, соединены со входом элемента ИЛИ 10, выход которого соединен со входом дискриминатора 11 импульсов по длительности. Выход дискриминатора 11 импульсов по длительности соединения со вторым входом триггера 5. Выходы 12 и 13 соединены с выходами согласующего блока 7 и являются выходами устройства 14 для синхронизации блоков вычислительной системы. Устройства 14 для синхронизации подключаются выходами 12 и 13 соответственно к линиям 15 и 16.

Устройство работает следующим образом.

При включении питания один из генераторов 1 включается раньше других и начинает генерировать импульсную последовательность. Сигналы этой последовательности поступают на вход формирователя 2 фаз. На выходах формирователя 2 фаз формируются импульсные последовательности с необходимыми фазовыми соотношениями .Эти иг-тульсные последовательности поступают на информационные входы коммутатора 3. Сигнал с выхода триггера 4 поступает на управляющий вход когу1мутатора 3 и разрешает прохождение сигналов импульсной последовательности с одного из информационных входов коммутатора 3 на его выход. Сигналы с выхода коммутатора 3 включают триггер 5,а сигнал с выхода триггера 5 поступает на управляющий вход формирователя 6 временных интервалов, и разрешает формирование на его выходах сигналов с .заданными параметрами. Эти сигналы являются сигналами фаз тактового питания и через согласующий блок 7 поступают на выходы 12 и 13 данного устройства 14 и через линии 15 и 16 на выходы 12 и 13 других устройств 14. Если синхронизирующие импульсы в линиях 15 и 16 поступают с данного устройства 14, то сигналы на первом входе и первом выходе соответствующего блока 7 совпадают. CyzviMaTop 8 по модулю два формирует на своем выходе О. Аналогично совпадают сигналы на втором входе и втором выходе согласующего блока 7, и на выходе сумматора 9 по модулю два также имеем логический О. Отсутствие импульсных сигналов на входах элемента ИЛИ 10 приводит к тому, что импульсные сигналы на выходе этого элемента также отсутствуют. Отсутствие импульсных сигналов н входе дискриминатора импульсов по длительности ,11 не вызывает включение дискриминатора, на его В1оходе присутствует сигнал, соответствующий отсутствию информации. Триггер 5 остается во включенном состоянии и разрешает прохождение импульсных последовательностей с выхода формирователя 2 фаз через формирователь б временных интервалов и через согласующий блок 7 на выходы 12 и 13 и в линии 15 и 16.

Если генератор 1 данного устройства 14 после включения питания оказался менее инициативным,, то его выключение произойдет несколько позже, чем включился более инициативный генератор 1. Импульсные последователь.ности с выходов 12 и 13 устройства 14 с более инициативным генератором поступят в линии 15 и 16 и на вторые входы сумматоров 8 и 9 по модулю устройств 14 с менее инициативными генераторами 1. Логические сигналы на первом и втором входах сумматоров 8 и 9 по модулю два отличаются,так как на входах согласующего блока 7 сигналы отсутствуют. Импульсные последовательности с линий 15 и 16 через сумматоры 8 и 9 по модулю два и элемент ИЛИ 10 поступят на вход дискриминатора Ц импульсов по длительности . При подаче на вход дискриминатора 11 импульсов по длительности импульсных сигналов, длительность которых превышает наперед заданную, на его выходе сформируется потенциальный сигнал, соответствующий наличию информации.. Этот сигнал удерживает триггер 5 в выключенном состоянии, а сигнал с выхода триггера 5 поступит на управляющий вход формирователя временных интервалов б и запретит прохождение импульсных последовательностей с выхода формирователя 2 фаз на входы согласующего блока 7 и в линии 15 и 16.

Так продолжается до тех пор, пока инициативный генератор 1 не откажет. При отказе инициатив-ного генератора 1 формирование импульсных последовательностей в линиях 15 и 16 на выходах 12 и 13 устройств 14 прекратится. Формирование импульсных сигналов на выходе элемента ИЛИ 10 также прекратится, поскольку на выходах сумматоров 8 и 9 по модули два будут логические О, так как на их входах логические сигналы совпадают. На входе дискриминатора импульсов по длительности 11 импульсы отсутствуют, на его выходе сформируется сигнал, соответствующий отсутствию информации. Этот сигнал разрешит триггеру 5 включение. Однако включение триггера 5 произойдет не в произвольный момент времени, а при действии импульса на его входе, соединенном с выходом коммутатора 3. Коммутатор 3 пропускает импульсы со своих информационных входов на выход под действием управляющего

сигнала с выхода триггера 4. Триггер 4 запоминает в какой из линий 15 или 16 синхронизирующий импульс действовал последним. Управление коммутатором триггер 4 Осуществляет таким образом, что через коммутатор 3 на триггер 5 поступает включающий импульс той фазы, которая обеспечивает разблокирование формирователя 6 временных интервалов в тот момент времени, при котором очередность следования синхронизирующих импульсов в линиях 15 и 16 и на выходах 12 и 13 устройств 14 остается ранее установленной .

Расширение функциональных возможностей устройства, т.е. обеспечение возможности формирования многофазного сигнала, позволяет более оптимальным образом организовать вычислительный процесс в вычислительной машине

и более эффективно использовать aijпаратные устройства.

Формула изобретения

Устройство для синхронизации блоков вычислительной системы, содержащее генератор, первый сумматор .по модулю два, дискриминатор импульсов

по длительности, первый триггер,

формирователь временных интервалов, причем выход Дискриминатора импульсов по длительности соединен нулевым входом первого триггера, выход которого соединен с управляющим входом

формирователя временных интервалов, первый выход которого соединен с первым информационным входом согласующего блока и с первым входом первого сумматора по модулю два, второй

вход которого соединен с первым выходом согласующего блока, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения

ВОЗМОЖНОСТИ формирования многофазного сигнала, устройство содержит формирователь фаз, второй триггер,коммутатор, второй сумматор по модулю два, элемент ИЛИ, причем выход генеpafopa соединен со входом формирователя фаз, первый и второй выходы которого соединены соответственно с первым и вторым информационными входами формирователя временных интервалов и коммутатора, управляющий

вход коммутатора соединен с выходом второго триггера, а выход коммутатора соединен с единичным входом первого триггера, второй выход формирователя временных интервалов соединен

с вторым входом согласующего блока и с первым входом второго сумматора по модулю два, первый и второй выходы согласующего блока, соединены соответветственно с единичным и нулевым

входами второго триггера, выходами

устройства и вторыми входами второго и сумматоров по модулю два соответственно, выходы сумматоров по модулю два соединены с входами элемента ИЛИ, выход которого соединен со входом дискриминатора импульсов по длительности.

Источники информации, принятые во внимание при экспертизе

1. Патент США 3602900, кл. 340-172.5, опублик, 1971.

2. Патент Франции № 2114901, кл. G Об F 1/04, опублик. 1972.

3. Авторское свидетельство СССР 660043, кл. G 06 F 1/04, 1977 прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU881719A1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1983 |

|

SU1092744A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК СИГНАЛОВ УПРАВЛЕНИЯ И ВЗАИМОДЕЙСТВИЯ С АДАПТИВНОЙ ДИФФЕРЕНЦИАЛЬНОЙ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1993 |

|

RU2103840C1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Цифровой демодулятор сигналов с относительной фазовой модуляцией | 1981 |

|

SU985970A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

/4

/«

Авторы

Даты

1982-01-15—Публикация

1979-12-11—Подача