I

Изобретение относится к вычислительной технике и может быть использовано в качестве специализированного блока универсальной электронной вычислительной машины, а также задающей аппаратуры для воспроизведения случайных вибраций при исследовании надежности с помощью вибростендов.

Известны генераторы случайных процессов, построенные в основном по известной схеме с использованием аналоговых элементов, в которых исходный случайный процесс с равномерным спектром подается на вход гребенки полосовых фильтров, которые предусматривают регулировку уровня выходных сигналов. Задавая определенные уровни выходного сигнала на выходе каждого фильтра с последующим суммированием их на суммирующем устройстве, формируется случайный процесс с тем или иным видом спектра 1 .

Однако для этих устройств пpиcyш нестабильность элементов (L,С-элементы), которая в конечном счете сказывается на стабильности основаных характеристик генератора случайных процессов, а также сложность построения подобных устройств для генерирования инфранизкочастотных, щирокополосных случайных процессов.

Известны также генераторы случайных процессов, содержащие цифровой фильтр, который является основным блоком. Фильтр для такого устройства есть специализированное арифметическое устройство, количество которых достигает большого числа (50-100) 2.

Однако такие устройства отличаются большими аппаратными затратами. Кроме того, при получении задашгого вида спектра затруднена перестройка формы воспроизводящего спектра.

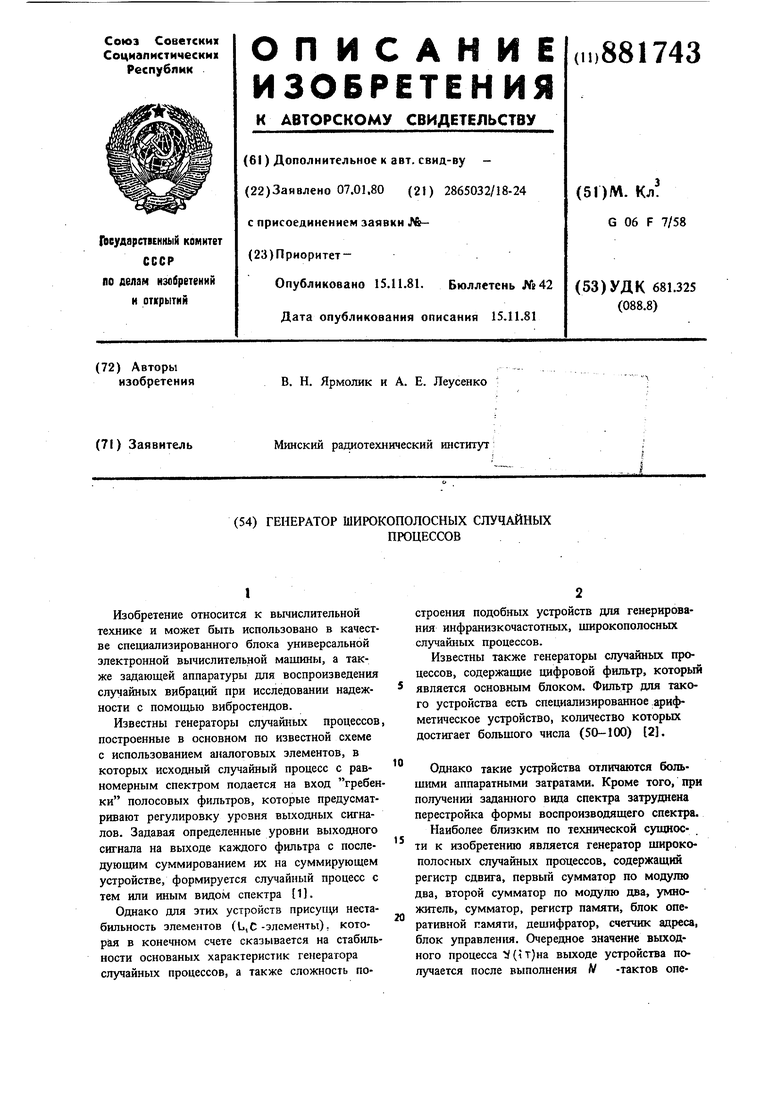

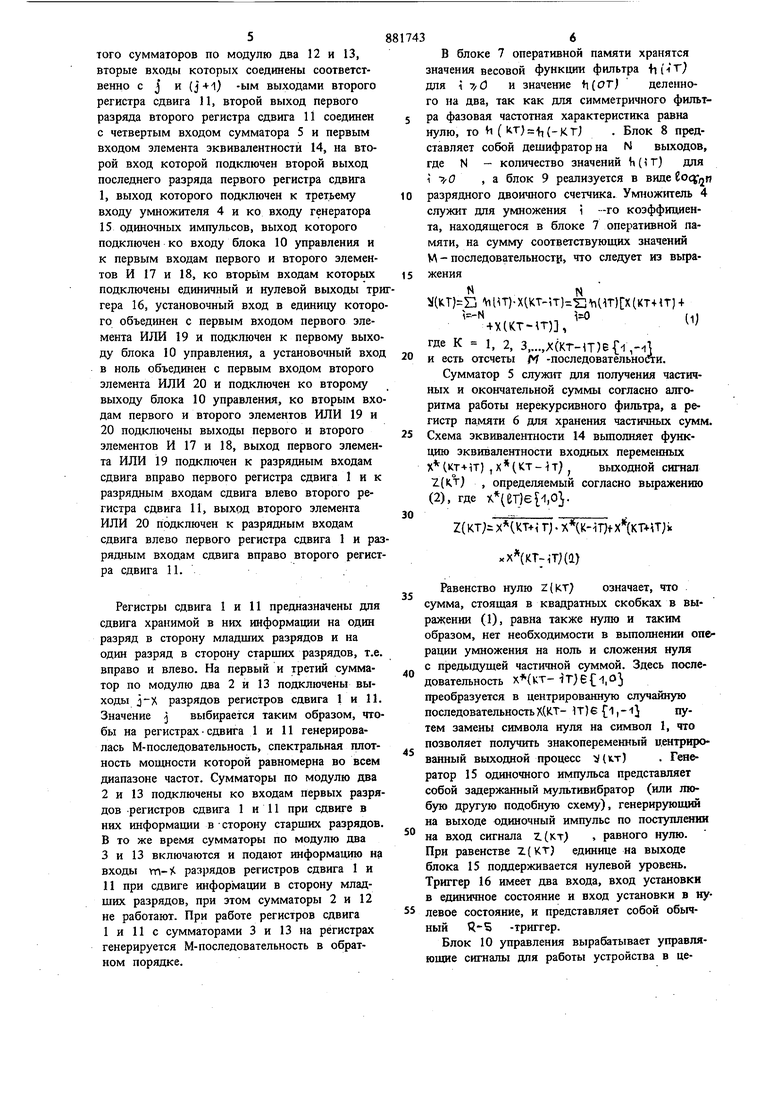

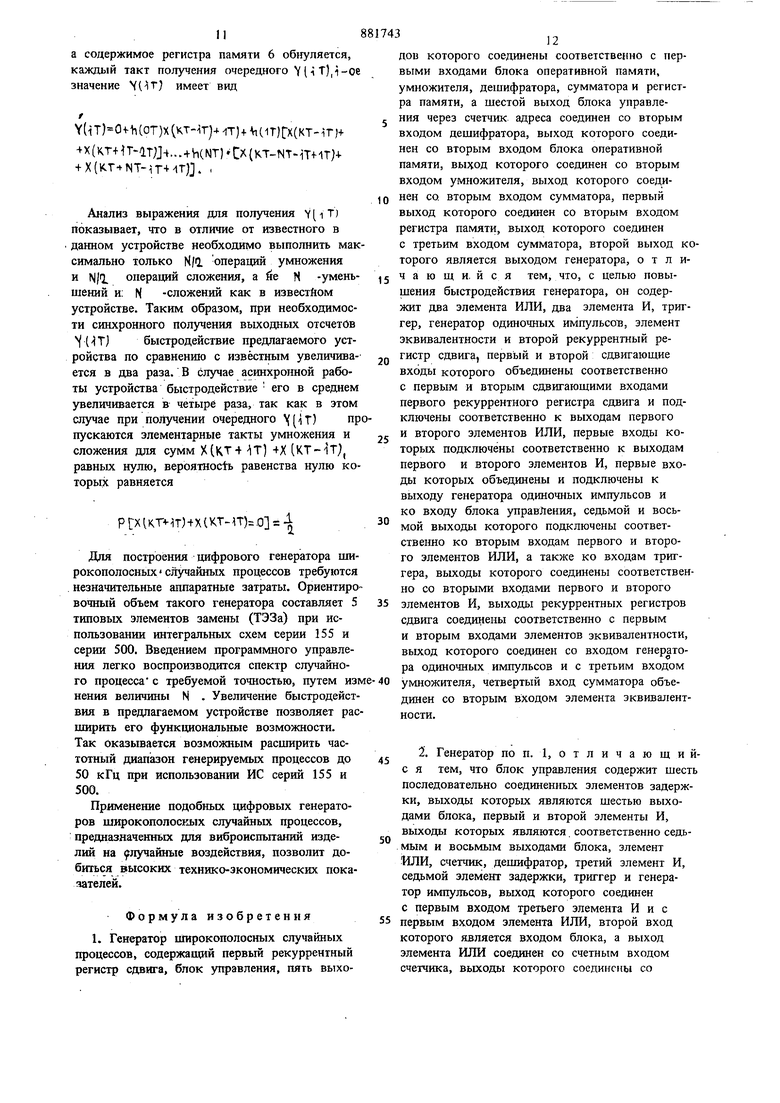

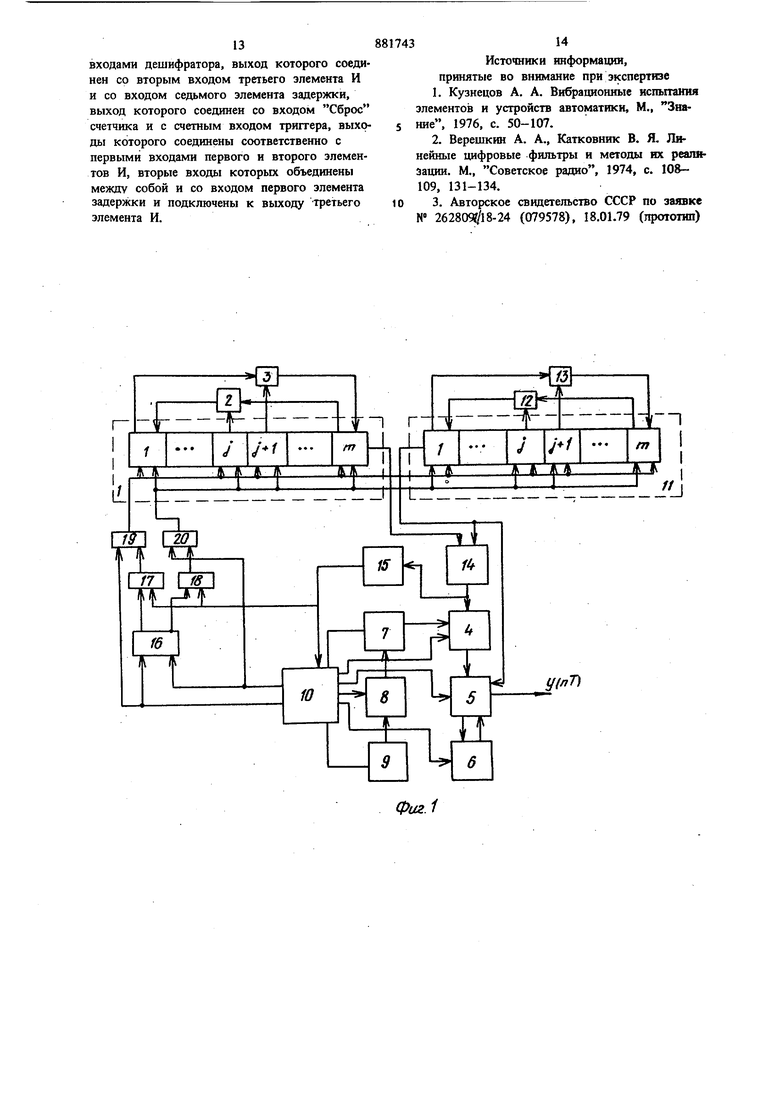

Наиболее близким по технической сущности к изобретению является генератор широкополосных случайных процессов, содержащий регистр сдвига, первый сумматор по модулю два, второй сумматор по модулю два, умножитель, сумматор, регистр памяти, блок оперативной памяти, дешифратор, счетчик адреса, блок управления. Очередное значение выходного процесса V (i т)на выходе устройства получается после выполнения Л/ -тактов one3рации умножения и сложения, где N 100500 3. Недостатком генератора широкополосных случайных процессов является низкое быстродействие, так как для получения одного выходного отсчета необходимо выполнить А/ элементарных тактов. При практической реали зации затруднительным оказывается построение устройства, позволяющего генерировать слзд1айные процессы в широком частотном диапазоне. Так, максимальная граница частотного диапазона в реальных устройствах не превышает 10 кГц. Цель изобретения - повышение быстродей ствия устройства, расширение функциональных возможностей генератора, позволяющего воспроизводить случайные процессы с более сложной спектральной характеристикой. Для достижения поставленной цели в генератор ;широкополосных, случайных процессов, содержащий первый рекуррентный регистр сдвига, блок управления, пять выходов которого соединены соответственно с первыми входами блока оперативной памяти, умно жителя, дешифратора, сумматора и регистра памяти, а шестой выход блока управления через счетчик адреса соединен со вторым входом дешифратора, выход которого соединен со вторым входом блока оперативной памяти, выход которого соединен со вторым йходы умножителя,выход которого соединен со вторым входом сумматора, первый вь1ход которого соединен со вторым входом регистра памяти, выход которого соединен с третьим входом сумматора, второй выход которого является выходом генератора, введены два элемента ИЛИ, два элемента И, триггер, гене ратор одиночных импульсов, элемент эквивалентности и второй рекуррентный регистр сдвига, первый и второй сдвигающие входы которого объединены соответственно с первы и вторым сдвигающими входами первого рекуррентного регистра сдвига и подключены соответственно к выходам первого и второго элементов ИЛИ, первые входы которых подключены соо1ветственно к выходам первого и второго элементов И, первый входы которых объединены и подключены к выходу генератора одиночных импульсов и ко входу блока управления, седьмой и восьмой вы ходы которого подключены соответственно ко вторым входам первого и второго элементов ИЛИ, а также ко входам триггера, выходы которого соединены соответственно со вторыми входами первого и второго элементов И, выходы рекуррентных регистров сдвигаСоединены соответственно с первым и вторым входами элементов эквивалентности, выход которого соединен со входом генерато ра одиночных импульсов и с третьим входом умножителя, четвертый вход сумматора объединен со вторым входом элемента эквивалентности. Кроме того, блок управления содержит шесть последовательно соединенных элементов задержки, выходы которых являются шестью выходами блока, первый и второй элементы И, выходы которых являются соответственно седьмым и восьмым выходами блока, элемент ИЛИ, счетчик, .дешифратор, третий элемент И, седьмой элемент задержки, триггер и генератор импульсов, выход которого соединен с первым выходом третьего элемента И и с первым входом элемента ИЛИ, второй вход которого является входом блока, а выход элемента ИЛИ соединен со счетным входом счетчика, выходы которого соединены со входами дешифратора, выход которого соединен со вторым входом третьего элемента И и со входом седьмого элемента задержки, выход которого соединен со входом Сброс счетчика и с счетным входом триггера, выходы которого соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых объединены между собой со входом первого элемента задержки и подключены к выходу третьего элемента И, На фиг. 1 приведена блок-схема генератора; на фиг. 2 - схема блока управления. Генератор широкополосных случайных процессов содержит первый рекуррентный регистр сдвига 1 с сумматорами по модулю два 2 и 3, умножитель 4, сумматор 5, регистр памяти 6, блок 7 оперативной памяти, дешифратор 8, счетчик адреса 9, блок 10 управления, второй регистр сдвига И с сумматорами по модулю два 12 и 13 в цепи обратной связи, элемент эквивалентности 14, генератор 15 одиночных импульсов, тоиггер 16, первый и второй элементы И 17 и 18, а также первый и второй элементы ИЛИ 19 и 20, выходы и входы первого и последнего разрядов первого регистра сдвига 1 соединены с первыми входами и выходами первого и второго сзтмматоров по модулю два 2 и 3 вторые входы которых соединены соответственно с ( -ым выходами регистра сдвига 1, кроме того, счетчик адреса 9, дешифратор 8, блок 7 оперативной памяти, умножитель 4, сумматор 5 и регистр памяти 6 соединены последовательно и ко вторым входам блоков 4-9 подключены выходы блока 10 управления, к третьему входу сумматора 5 подключен выход регистра памяти 6, первый выход сумматора является выходом генератора, а также выходы и входы первого и последнего разрядов второго регистра сдвига 11 соединены с первыми входами и выходами третьего и четвертого сумматоров по модулю два 12 и 13, вторые входы которых соединены соответственно с j и (j-«-l) -ым выходами второго регистра сдвига И, второй выход первого разряда второго регистра сдвига И соединен с четвертым входом сумматора 5 и первым входом элемента эквивалентности 14, на второй вход которой подключен второй выход последнего разряда первого регистра сдвига 1, выход которого подключен к третьему входу умножителя 4 и ко входу генератора 15 одиночных импульсов, выход которого подключен ко входу блока 10 управления и к первым входам первого и второго элементов И 17 и 18, ко вторым входам которьк подключены единичный и нулевой выходы тр гера 16, установочный вход в единицу которо го объединен с первым входом первого элемента ИЛИ 19 и подключен к первому выхо ду блока 10 управления, а установочный вход в ноль объединен с первым входом второго элемента ИЛИ 20 и подключен ко второму выходу блока 10 управления, ко вторым вхо дам первого и второго элементов ИЛИ 19 и 20 подключены выходы первого и второго элементов И 17 и 18, выход первого элемента ИЛИ 19 подключен к разрядным входам сдвига вправо первого регистра сдвига 1 и к разрядным входам сдвига влево второго регистра сдвига 11, выход второго элемента ИЛИ 20 подключен к разрядным входам сдвига влево первого регистра сдвига 1 и раз рядным входам сдвига вправо второго регист ра сдвига 11. Регистры сдвига 1 и 11 предназначены для сдвига хранимой в них информации на один разряд в сторону младших разрядов и на один разряд в сторону старших разрядов, т.е. вправо и влево. На первый и третий сумматор по модулю два 2 и 13 подключены выходы j-x разрядов регистров сдвига 1 и 11. Значение выбирается таким образом, что бы на регистрах сдвига 1 и 11 генерировалась М-последовательность, спектральная плотность мощности которой равномерна во всем диапазоне частот. Сумматоры по модулю два 2и 13 подключены ко входам первых разря дов .регистров сдвига 1 и 11 при сдвиге в них информации в сторону старших разрядов. В то же время сумматоры по модулю два 3и 13 включаются и подают информацию на входы vn-i разрядов регистров сдвига 1 и 11 при сдвиге информации в сторону младших разрядов, при этом сумматоры 2 и 12 не работают. При работе регистров сдвига 1 и 11 с сумматорами 3 и 13 на регистрах генерируется М-последовательность в обратном порядке. В блоке 7 оперативной памяти хранятся значения весовой функции фильтра fil для {7/0 и значение (ОТ) деленного на два, так как для симметричного фильтра фазовая частотная характеристика равна нулю, то 1 ()b(-Krj . Блок 8 представляет собой дешифратор на N выходов, где N - количество значений Ь (i т) для 17/0 , а блок 9 реализуется в виде Cocy/jn разрядного двоичного счетчика. Умножитель 4 служит для умножения i --го коэффициента, находящегося в блоке 7 оперативной памяти, на сумму соответствующих значений М - последовательности, что следует из вьфаженияNN )Б MliT)-X(KT-iT)(1T)X( (1) 4Х(), где К 1, 2, 3,...,X(KT-lT)e{i,-i и есть отсчеты Л7 -последовательности. Сумматор 5 служит для получения частичных и окончательной суммы согласно алгоритма работы нерекурсивного фильтра, а регистр памяти 6 для хранения частичных сумм. Схема эквивалентности 14 вьшолняет функцию эквивалентности входных перемешай X () , X (Ст - i т J выходной сигнал 7.(1чТ) , определяемый согласно выражению (2), где 1(еТ)е,ОТ,. Z(KT;::x(vcT+i г; - Акчт))) хх(кт-1ТЛ1) Равенство нулю 2(кт означает, что сумма, стоящая в квадратных скобках в выражении (1), равна также нулю и таким образом, нет необходимости в вьшолнении оп&рации умножения на ноль и сложения нуля с предыдущей частичной суммой. Здесь последовательность х(кт- IT),01, преобразуется в центрированную случайную последовательностьХ(К.т- IT) е {1,- ijпутем замены символа нуля на символ 1, что позволяет получить знакопеременный центрированный выходной процесс (кт) . Генератор 15 одиночного импульса представляет собой задержанный мультивибратор (или любую другую подобную схему), генерирующий на выходе одиночный импульс по поступлении на вход сигнала Z.(KT) , равного нулю. При равенстве Z(KT) единице на выходе блока 15 поддерживается нулевой уровень. Триггер 16 имеет два входа, вход установки в единичное состояние и вход установки в нулевое состояние, и представляет собой обычный R-S -триггер. Блок 10 управления вырабатывает управляющие сигналы для работы устройства в лом. На фиг. 2 приведена структурная блоксхема блока 10 управления, которая состоит из счетчика 21, дешифратора 22, генератора импульсов 23, триггера 24, элемента ИЛИ 25 трех элемеитов И 26-28 и семи элементов задерж ки 29-35. На счетчик 21 записывается код, равиый по сигналу поступающему с выхода элемента задержки 31. По поступлению импульсов с выходов генератора 25 и блока 15 содержимое счетчика 21 уменьшается до нуля. При ненулевом содержимом счетчика дешифратор 22 вырабатывает сигнал разрешения на второй вход элемента И 27, на первый вход которого поступают импульсы с выхода генератора импульсов 23. Триггер 24 рабо тает в счетном режиме и разрешает прохождение импульсов через первый или второй элементы И 25 и 26 блока 10 управления,, с выходов которых импульсные потоки посту пают на входы блоков 19 и 20. Появление нулевого кода на счетчик инициирует генерирование сигнала на выходе дешифратора, который запрещает прохождение импульсов через элемент И 27 и, проходя через элемент задержки 31, поступает на счетный вход триггера и на установочные входы счетчика в состояние кода. На выходах шести элементов задержки появляются сигналы, поступающие на вход блоков 4-9. На фиг. 2 цифры 4-9, 16, 19, 20 обозначают номер блока, с которым связан соответствзгющий узел блока 10 управления. Функционирование устройства происходит следующим образом. Для получения случайного процесса с заданным видом спектральной плотности мощности определяется весовая функция (дискрет ная) нерекурсивного цифрового фильтра. Дискретнь1е отсчеты весовой функции h(iT) где 17/0 , записываются в блок 7 оперативной памяти, причем значение ti(OT) записьшается уменьшенным в два раза, так как при выражение (1) принимает сле дующий вид (.ОТ) ) . Начальные коды, записываемые на первый и второй регист ры сдвига 1 и il, являются жестко зависымыми, причем если на один регистр можно записать любой код, кроме нулевого, то на второй необходимо записать код, соответству щий первому таким образом, что последовательность символов Двух кодов составляет участок длиной в 2 m - 1 символов из ис ходной М-последовательности, порождаемой полиномом 4(1) . 1 . Причем содержимое m -го разряда первого регистра сдвига 1 и содержимое 1-го разряда второго регистра сдвига 11 одинаковы и представляют собой один и тот же символ исходной М-последовател ности. На счетчике 9 адреса устанавливается адрес нулевого коэффициента. В первоначальный момент в цепь обратной связи первого регистра сдвига 1 включается сумматор по модулю два 2 и в цепь обратной связи второго регистра сдвига 11 сумматор по модулю два 13. По сигналам, поступающим из блока 10 управления на управляющие входы блоков 7-9 из оперативной памяти выбирается половинное значение нулевого коэффициента Н(оТ} значение которого умножается на cyMtyiy значений старшего разряда первого регистра сдвига 1 и младшего разряда второго регистра сдвига 11. Результат произведения на умножителе 4 равен l4oT))(tKT-oT)+x(KT+OTj l h(oT)|x(KT40T)|. Далее первое частичное произведение суммируется на сумматоре 5 с нулевым кодом, хранящимся на регистре памяти 6, при этом знак произведения определяется знаком, сим вола, хранящимся в первом разряде второго регистра. Если Х КГ+ОТ) 0 TO {KT-fOT - Iи соответственно знак первого ; частичного произведения Н(ОТ; (Т+огЛ отрицательный. В случае, когда Х(КТ40Т} то Х(кТ--ОТ) 1и знак произведения положительный. По управляющим сигналам блока 10 управления первичная частичная сумма O-t-h (ОТ). X(KT--OTJ записывается на регистр памяти 6. Далее из блока 10 управления поступает управляющий сигнал, который сдвигает информацию, хранящуюся в первом регистре сдвига 1 в сторону старших разрядов и во втором регистре сдвига 11 в сторону младщих разрядов, при этом работают сумматоры по модулю два 2 и 13. Управляющий сигнал на первый и второй регистры сдвига 1 и 11 поступает с перввго выхода блока 10 через элемент ИЛИ 19. После осуществления операции сдвига в старшем разряде первого регистра сдвига 1 хранится значение Х(КТ -1T), , а в первом разряде второго регистра сдвига 11 - значение X ( К Т + -t Т). Для значений X tKT-jT) и Х (КТ4-)Т) , а также значений Х(КТ-лТ) и (KT4iT) на 1-м такте возможны четьфе случая. 1. X () ОиХ(К.Т4( исоответственно путем замены О на -1 ХСкт-1Т)ги X (КТ 4 -IT) -. Значение 2 (цт) в этом случае равняется единице согласно выражению (2) на выходе элемента эквивалентности 14, Так как Z(KT):1, то на выходе блока 15 поддерживается нулевой уровень, а в устройстве умножения 4 осуществляется умножение Vl ИТ) на |-г) , так как |X(KT-1TJ4 +(КТ-|-1Т | 2/.Знак минус учитьгеается при выполнении операции суммирования в блоке . 5 при получении частичной суммы, при этом если Х( т) знак будет минус и если X (ttT+-lf)«i1 , то знак плюс. Далее с выхода блока 5 частичная сумма О4-hCOT)-Х(KT40T)f Vi(1T))((KT-ir)4X ((СТ-ИТ) записывается на регистр памяти 6. 2.Х(КТ--1Т) 0 и X(KT-f(r) исоответственно х(КТ--1Т)-1 И Х(.Т+ -ITJsl. Равенство нулю на выходе 15 говорит о равенстве нулю второго слагаемого в выражении Vi (-IT) ГХ С КТ -lT)tX(KT+-)T)J. Поэтому в блоках 4-6 никакие арифметические действия не производятся. Равенство нулю Z k т инициирует генерирование одиночного импульса на выходе блока 15, который через элемент И 17 и элемент ИЛИ 19 посту пает по цепи сдвига первого и второго регис ра сдвига 1 и 11, после чего в последнем и первом разрядах регистров сдвига 1 и 11 образуются значения Х (КТ-2Т) и X (КТ+2Т) соответственно. Сигнал с выхода блока 15 поступает на вход блока 10, с третьего выхода которого управляющий сигнал увеличивает со держимое счетчика адреса на единицу. Прохождение одиночного импульса через элемент 17 и 19 объясняется тем, что предыдущими импульсами сдвига триггер 16 устанавливается в единичное состояние и таким образом разрешающий потенциал образуется на единичном выходе 16 и соответственно на втором входе элемента И 17. 3.х,(К.Т--1Г; Г и X()0 , соответственно х(кт-11 1 и Х(кг+ . Равенство нулю 2(КТ на выходе схемы зквивалентности 14 говорит о равенстве нулю суммы X(KT-IT/ X(, Поэтому в этом случае 3 подобно случаю 2 действия- повторятся. 4.х(КТ-1Г) 1 иX() ) соответственно X 1КТ- и Х(КТ4-It rf. Значение г. (K.TJ в этом случае равняется единице согласно выражению (2). Поэтому все операции в блоках 4-6 повторяются. Единственным отличием является равенство знака суммы X 1КТ-ITJ- Xt КТ+1Т) плюсу После выполнения второго такта работы устройства в целом на регистре памяти 6 хранится частичная сумма )x(KT40T HiT)x(KT-1THX(KT+lT)lj причем третье слагаемое подобно первому может оказаться равным нулю. После поступления очередного импульса сдвига с блока 10 или одиночного импульса с блока 15 на старшем и младшем разрядах первого и второго регистра сдвига 1 и 22 хранятся значения X (КГ- IT)ИХ(КТ + 1Г; соответственно. Повторяя подобную процедуру К раз на сумматоре 5 получаем выражение0-vVlCOThX KT+OT))xlKT-1T}+X(kT4lT)t)(aT)x xtXll T-1T)fX()4...-fh(NT)rX(KT-NT 4X(),. что является первым отсчетом выходного широкополосного случайного процесса Y ( IT; . После получения значения V (-fr; регастр памяти 6 обнуляется, после чего осуществлябтся N+-1 сдвиг в сторону старших разрядов в первом регистре 1 и в сторону младших разрядов во втором регистре 11. При осуществлении ()- го нерабочего сдвига работа арифметических блоков 4 и 5 и генератора одиночного импульса 15 блокируется. Далее стрзтстура реверсивных регистров сдвига 1 и 11 изменяется таким образом, что в цепь обратной связи регистра сдвига 1 включается сумматор по модулю два 3 и в цепь обратной связи регистра сдвига 1 включается сумматор 2 по модулю два 3, и в цепь обратной связи регистра сдвига 11 сумматор по модулю два 12. В данном случае в регистре сдвига 1 осуществляются сдвиги в сторону младших разрядов, а в регистре 11 - в сторону старших разрядов. При каждом сдвиге устройство работает аналогично как при сдвигах информации в регистрах 1 и 11 в сторону старших и сторону младших разрядов, соответственно повторив подобную процедуру Ц раз на сумматоре получаем выражение0 Vllqr)-X(KT-|(r)-Hl(fT)-rX(KT-(LT)+X(irr40r)j4 1l(ат)Х ГХ(1СГ-ЭТ)+Х (KT4lT)j4ti(3T)h(КТ-4Т|4. 4 X )+... + ti( NTlfX (КТ-NT-1Т)+Х(КГ- NT-IT), что является вторым отсчетом выходного широкополосного случайного процесса NIUT), После получения четного значения QTj стрзтстура обратных связей в регистрах сдвига 1 и II и направление сдвигов в них из; меняется подобно как при получении {-1Т). Далее производится не рабочий сдвиг в сторону старших разрядов в первом регистре 1 ив сторону младших разрядов во втором регистре 11. Причем N + -1 нерабочий сдвиг осуществляется перед получением каждого очередного значения Y (-i TJ . Подобно осуществлению нерабочего сдвига перед получением очередного значения V («Т) содержимое счетчика 9 адреса не обнуляется, 11 а содержимое регистра памяти 6 обнуляется, каждый такт получения очередного V (л Т),i-oe значение V(it; имеет вид Y(iT)(oT)x(KT-ir)) + (iTirx(KT-ir)+ 4X(KT+ T-/lT;ji...4.V,(NT)CX{KT-NT4Tf1T)4+ X(KT4-NT-ir+tT)J. , Анализ выражения для получения Y Т) показывает, что в отличие от известного в данном устройстве необходимо выполнить мак симально только N/Q. операций умножения и N/12, операций сложения, а йе N -уменьшений и: N -сложений как в известйом устройстве. Таким образом, при необходимости синхронного получения выходных отсчетов f (/it) быстродействие предлагаемого устройства по сравнению с известным увеличивается в два раза. В случае асинхронной работы устройства быстродействие его в среднем увеличивается в четыре раза, так как в этом случае при получении очередного X(iT) пр пускаются элементарные такты умножения и сложения для сумм Х(КТ4 4Х (КТ-1Т}| равных нулю, вероятнос1ъ равенства нулю которых равняется Р ГХIКТ+- ГН X ( ) .0 -i Для построения цифрового генератора широкополосных случайных процессов требуются незначительные аппаратные затраты. Ориентиро вочный объем такого генератора составляет 5 типовых элементов замены (ТЭЗа) при использовании интегральных схем серии 155 и серии 500. Введением программного управления легко воспроизводится спектр случайноГО процессаС требуемой точностью, путем изм нения величины N . Увеличение быстродействия в предлагаемом устройстве позволяет рас ширить его функциональные возможности. Так оказывается возможным расширить частотный диапазон генерируемых процессов до 50 кГц при использовании ИС серий 155 и 500. Применение подобных цифровых генераторов широкополосных случайных процессов, предназначенных для виброиспьпаний изделий на 9 1учайные воздействия, позволит добиться эысоких технико-экономических показателей. Формула изобретения 1. Генератор широкополосных случайных процессов, содержащий первый рекуррентный регистр сдвига, блок зправления, пять выходов которого соединены соответственно с первыми входами блока оперативной памяти, умножителя, дешифратора, сумматора и регистра памяти, а шестой выход блока управления через счетчик адреса соединен со вторым входом дешифратора, выход которого соединен со вторым входом блока оперативной памяти, выход которого соединен со вторым входом умножителя, выход которого соединен со вторым входом сумматора, первый выход которого соединен со вторым входом регистра памяти, выход которого соединен с третьим входом сумматора, второй выход которого является выходом генератора, о т л ич а ю щ и, и с я тем, что, с целью повышения быстродействия генератора, он содержит два элемента ИЛИ, два элемента И, триггер, генератор одиночных импульсов, элемент эквивалентности и второй рекуррентный регистр сдвига, первый и второй сдвигающие входы которого объединены соответственно с первым и вторым сдвигаюшими входами первого рекуррентного регистра сдвига и подключены соответственно к выходам первого и второго элементов ИЛИ, первые входы которых подключены соответственно к выходам первого и второго элементов И, первые входы которых объединены и подключены к выходу генератора одиночных импульсов и ко входу блока управления, седьмой и восьмой выходы которого подключены соответственно ко вторым входам первого и второго элементов ИЛИ, а также ко входам триггера, выходы которого соединены соответственно со вторыми входами первого и второго элементов И, выходы рекуррентных регистров сдвига соединены соответственно с первым и вторым входами элементов эквивалентности, выход которого соединен со входом генератора одиночных импульсов и с третьим входом умножителя, четвертый вход сумматора объединен со вторым входом элемента эквивалентности. 2. Генератор по п. 1, о т л и ч а ю ш и йс я тем, что блок управления содержит шесть последовательно соединенных элементов задержки, выходы которых являются шестью выходами блока, первый и второй элементы И, выходы которых являются соответственно седьмым и восьмым выходами блока, элемент ИЛИ, счетчик, дешифратор, третий элемент И, седьмой элемент задержки, триггер и генератор импульсов, выход которого соединен с первым входом третьего элемента И и с первым входом элемента ИЛИ, второй вход которого является входом блока, а выход элемента ИЛИ соединен со счетным входом счетчика, выходы которого соединены со

13

входами дешифратора, выход которого соединен со вторым входом третьего элемента И и со входом седьмого элемента задержки, выход которого соединен со входом Сброс счетчика и с счетным входом триггера, выходы которого соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых объединены между собой и со входом первого элемента задержки и подключены к выходу третьего элемента И.

8174314

Источники информации, принятые во внимание при экспертизе

1.Кузнецов А. А. Вибрационные испьшшия элементов и устройств автоматики, М., Зна5 ние, 1976, с. 50-107.

2.Верешкин А. А., Катковиик В. Я. Линейные цифровые фильтры и методы их реализации. М., Советское радио, 1974, с. 10ft109, 131-134.

10 3. Авторское свидетельство СССР по заявке № 262809 /18-24 (079578), 18.01.79 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор широкополосных случайных процессов | 1978 |

|

SU771652A1 |

| Система передачи и приема информации рекуррентными последовательностями | 1985 |

|

SU1338101A1 |

| Генератор случайного потока чисел | 1982 |

|

SU1053106A1 |

| Генератор случайного процесса | 1983 |

|

SU1111159A1 |

| Цифровой генератор синусоидальных сигналов | 1984 |

|

SU1215162A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для определения законов распределения вероятностей | 1978 |

|

SU922765A1 |

| Устройство для вычисления оценок математического ожидания и дисперсии | 1983 |

|

SU1280392A1 |

| Устройство для распознавания образов | 1987 |

|

SU1531115A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

Фиг.1

Г- 3f -t 2-т 33 -1 3 55-I :,Д б

Фиг2

Авторы

Даты

1981-11-15—Публикация

1980-01-07—Подача