регистр сдвига, устройства умножения, сумматор, блок управления 3. В этом устройстве входным сигналом является двоичный белый шум, который поступает на первый разряд регистра сдвига цифрового нерекурсивного фильтра. По приходу импульсов сдвига информация, хранящаяся в разрядах регистра сдвига, сдвигается на разряд, при этом содержимое последнего разряда пропадает, а в первый разряд поступает очередное значение двоичной случайной цифры

О

1 , причем Р(О) 0,5

или

и Р(1) . Количество разрядов регистра сдвига определяется классом спектральных характеристик, воспроизводимых цифровым генератором случайных процессов. Так, например, для воспроизведения полосовых случайных процессов реальное значение разрядности равняется 10-50. В случа воспроизведения широкополосных случайных процессов количество -разрядов регистра сдвига и соответственно устройств умножения в большинстве случаев определяется шириной частотного диапазона и крутизной резонансных всплесков задаваемой частотной характеристики.

Существенным недостатком цифровог генератора широкополосных случайных процессов является большие аппаратурные затраты, так как разрядность регистра сдвига в большинстве случаев равняется 100-1000.При заданном числе разрядов точность ограничена.

Целью изоЬретения является повышение точности воспроизведения спектральной мощности при заданном числе разрядов,

Для достижения поставленной цели в генератор широкополосных случайных процессов, содержащий регистр сдвига разрядное входы которого соединены соответственно с первым и вторым выхода блока управления, третий и четвертый выходы которого соеданены соответственно с первыми входами умножителя и сумматора, первый выход которого является выходом генератора а второй вход сумматора соединен с выходом умножителя, второй вход которого соединен с выходом последнего разряда регистра сдвига,введены и второй сумматоры по модулю два,счетчик адреса,блок оперативной памяти, дешифратор и -регистр памяти, первый вход и выход которого соединены соответственно со вторым выходом и третьим входим сумматора, а второй вход регистра памяти соединен с выходом Запись блока управления, первый выхрд Опрос которого соединен со входом счетчика адреса, выход которого соединен с первым входом дешифратора, второй вход которого соединен со вторым выходом Опрос блока управления.

третий выход Опрос которого соединен с первым входом блока оперативной , второй вход которого соединен с выходом дешифратора, а выход блока оперативной памяти соединен с третьим входом умножителя, выходы и входы первого и последнего разрядов регистра сдвига соединены соответствейно с первыми яходами и выходами первого и второго сумматоров по модулю два, вторые входы которых соединены соответственно с 3-ым и (J + 1) выходами регистра сдвига (j 1 -m).

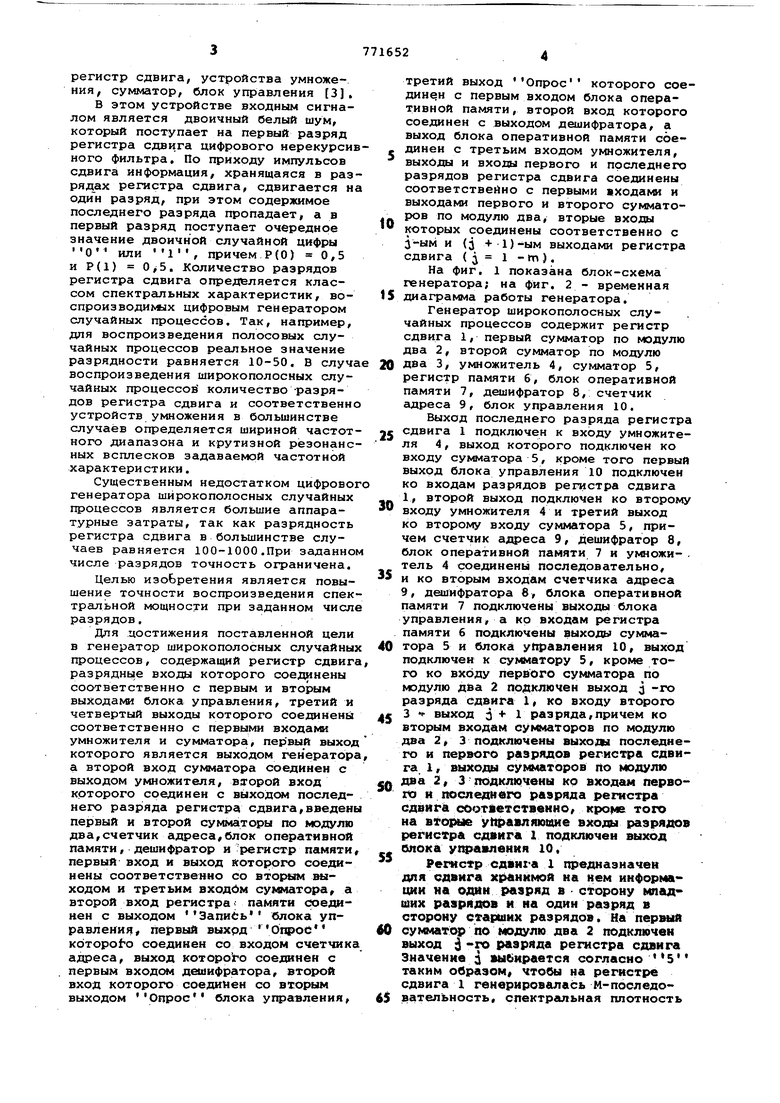

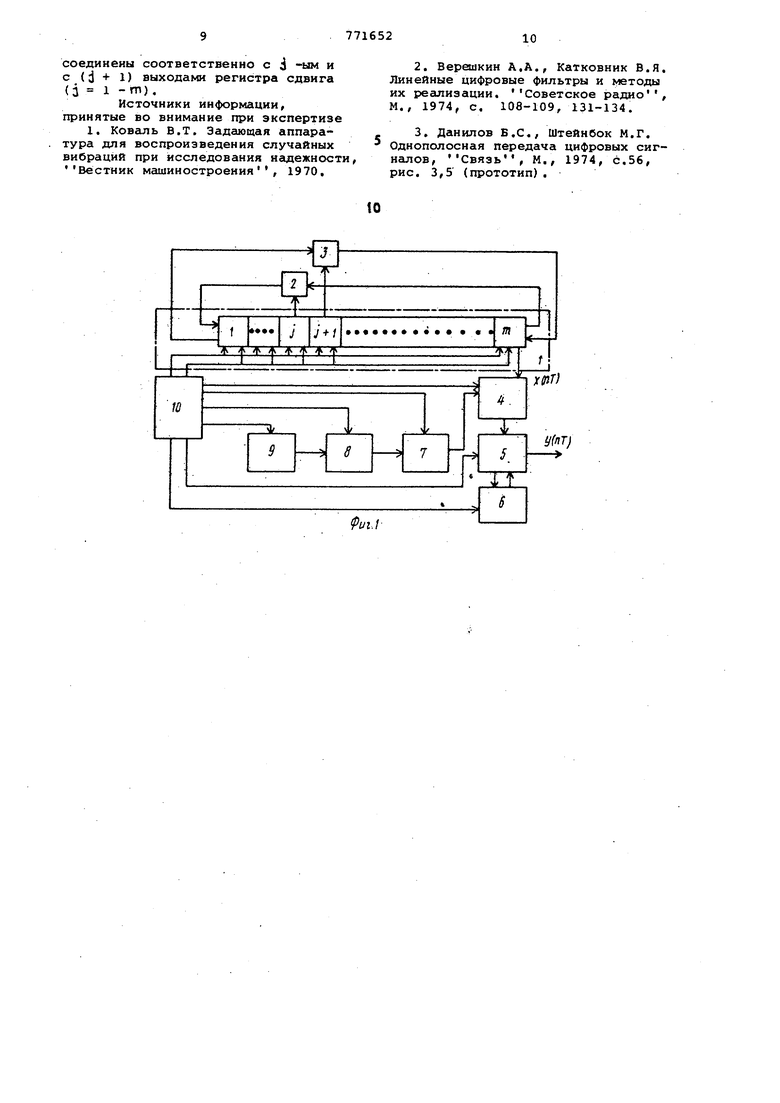

На фиг. 1 показана блок-схема генератора; на фиг, 2 - временная диаграмма работы генератора.

Генератор широкополосных случайных процессов содержит регистр сдвига 1, первый сумматор по модулю два 2, второй сумматор по модулю два 3, умножитель 4, сумматор 5, регистр памяти 6, блок оперативной памяти 7, дешифратор 8, счетчик адреса 9, блок управления 10.

Выход последнего разряда регистр сдвига 1 подключен к входу умножителя 4, выход которого подключен ко входу сумматора 5, кроме того первый выход блока управления 10 подключен ко входам разрядов регистра сдвига 1, второй выход подключен ко втором входу умножителя 4 и третий выход ко второму входу сумматора 5, причем счетчик адреса 9, дешифратор 8, блок оперативной памяти 7 и умножитель 4 соединены последовательно, и ко вторым входам счетчика адреса 9, дешифратора 6, блока оперативной памяти 7 подключены выходы блока управления, а ко входам регистра памяти 6 подключены выходы сумматора 5 и блока управления 10, выход подключен к сумматору 5, кроме того ко входу первого сумматора по модулю два 2 подключен выход j -го разряда сдвига 1, ко входу второго 3 Г выход 3 1 раз ряда, причем ко вторым входам сумматоров по модулю два 2, Э подключены выхоли последнего и первого разрядов регистра сдвига 1, выходы сумматоров по модулю два 2, 3 подключены ко входам первого и последнего разряда регистра сдвйг а соответственно, кро|4е того на вторые уНрааляю&ше входы разрядю регистра сдвига 1 подключен выход опока ущ авления 10,

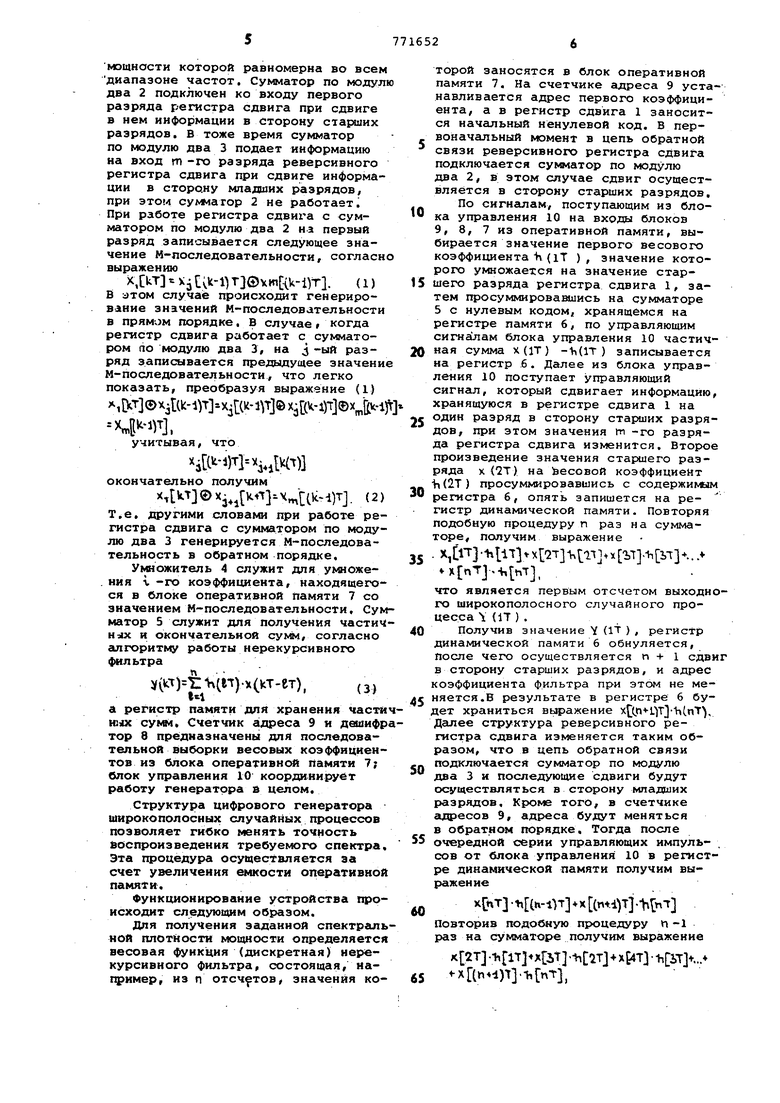

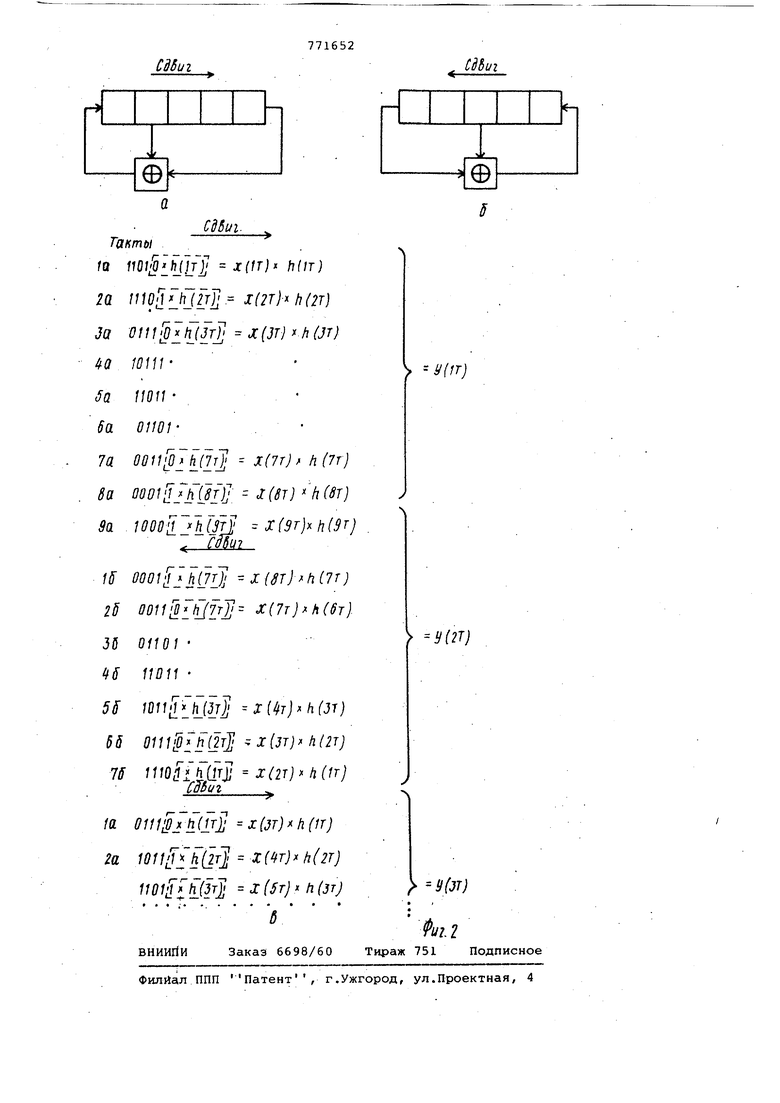

Ретстр сдвнга 1 предназначен для сдвига хранимой на нем информации на один разряд в сторону мпадшнх разрядов и на один разряд в сторону ста|ших разрядов. На первый сумматор по модулю два 2 подключен выход 5 1 разряда регистра сдвига Значение выбирается согласно 5 таким образом чтобы на регистре сдвига 1 генерировалась М-последователЬность, спектргшьная плотность мощности которой равномерна во всем диапазоне частот. Сумматор по модул два 2 подключен ко входу первого разряда регистра сдвига при сдвиге в нем информации в сторону старших разрядов. В тоже время сумматор по модулю два 3 подает информацию на вход m -го разряда реверсивного регистра сдвига при сдвиге информации в сторону младших разрядов, при этом cy iarop 2 не работает. При работе регистра сдвига с сумматором по модулю два 2 н э первый разряд записывается следующее значение М-последовательности, согласн выражению X,CkT г Ц1С-1) T}©vm {k-i)T. (i) в атом случае происходит генерирование значений М-последовательности в прямом порядке. В случае i когда регистр сдвига работает с сумматором tio модулю два 3, на j -ый разряд записывается предыдущее значени М-последовательности, что легко показать, преобразуя выражение (1) A,(lC-i)T.X,j(K-l fI®X-(Vl)T ®X ijJc-l М-). учитывая, что х(М)т1-у,Ди(1) окончательно получим x,k.,.|;Mf}-4 Ck-i)Tj. (2) т.е. другими словами при работе регистра сдвига с сумматором по модулю два 3 генерируется М-последовательность в обратном порядке. Умножитель 4 служит для умноже. ния г -го коэффициента, находящегося в блоке оперативной памяти 7 со значением М-последовательности. Сум матор 5 служит для получения частич нлх. я окончательной сумм, согласно алгоритму работы нерекурсивного фильтра y(a)i:H(ei)-x(kT-eT), (з t«i а регистр памяти для хранения частй Hijx сукм. Счетчик адреса 9 и дешифр тор 8 предназначены для последовательной выборки весовых коэффициентов из блока оперативн( памяти 7; елок управления 10 коордннируёт работу генератора а целом. Структура цифрового генератора широкополосных случайных процессов позволяет менять точность воспроизведения требуемого спектра Эта процедура осуществляется за счет увеличения емкости оперативно памяти. Функционирование устройства про исходит следующим образом. Для получения заданной спектрал ной плотности мощности определяетс весовая функция (дискретная) нерекурсивного фильтра, состоящая, например, из л отсчетов, значения ко торой заносятся в блок оперативной памяти 7. На счетчике адреса 9 устанавливается адрес первого коэффициента, а в регистр сдвига 1 заносится начальный ненулевой код. В первоначальный момент в цепь обратной связи реверсивного регистра сдвига подключается cy в Iaтop по модулю два 2, в этом случае сдвиг осуществляется в сторону старших разрядов. По сигналам, поступающим нз блока управления 10 на входы блоков 9, 8, 7 из оперативной памяти, выбирается значение первого весового коэффициента К (iT ), значение которого умножается на значение старшего разряда регистра сдвига 1, затем просуммировавшись на сумматоре 5 с нулевым кодом, хранящемся на регистре памяти 6, по управляющим сигналам блока управления 10 частичная сумма х(1Т) -(1Т ) записывается на регистр 6. Далее нз блока управлеиня 10 поступает управляющий сигнал, который сдвигает информацию, хранящуюся в регистре сдвига 1 на один разряд в сторону старших разрядов, при этом значения w -го разряда регистра сдвига изменится. Второе произведение значения старшего разряда X{2Т) на Ьесовой коэффициент Н(2Т) просуммировавшись с содержиМЕОМ регистра б, опять запишется на регистр дина в1ческой памяти. Повторяя подобную процедуру п раз на сумматоре, получим выражение - Х,1Т}-К 1Т х 2Т 1,П. . ),, что является первым отсчетом выходного широкополосного случайного процесса (IT ) . Получив значение V (1 ) / регистр динамической памяти 6 обнуляется, после чего осуществляется п + i сдвиг в сторону старших разрядов, и адрес коэффициента фильтра при этом не меняется.В результате в регистре 6 будет храниться выражение (.пТу Далее структура реверсивного регистра сдвига изкюняется таким образом, что в цепь обратной связи подключается сумматор по модулю два 3 и последующие сдвиги будут осуществляться в сторону младших разрядов. Кроме того, в счетчике адресов 9, адреса будут меняться в обратном порядке. Тогда после очередной серии управляющих импуль- , сов от блока управления 10 в регистре динамической памяти получим выражение - (h-in X Cnti)T . повторив подобную процедуру п-1 раз на сумматоре получим выражение h lT xi:it -hC2Tj + .,. )7.,

что является вторым отсчетом выходного шиpoкoпoлocfнoгo случайного процесса Y(2T),

После получения четного значения выходного процесса в обратную связь регистра сдвига 1 подключается сумматор 2 и осуществляется сдвиг в сторону старших разрядов, при этом содержимое счетчика адреса не меняется. В результате на регистр динамической памяти заносится значение первой частичной суимл, равной X ЬТ . Аналогично,повторяя подобную процедуру, но изменяя адрес в счетчике 9 получим

Ytb-t --htli - Ht4T .{2T x|;5TJ-htiT ).

Таким образом на выходе цифрового генератора широкополосных случайных гфоцессов будут получаться.выходные отсчеты,

Более подробно, для конкретного случая ре шизации его структуры при п 5 и п 8, работа генератора иллюстрируется фиг. 2, На фиг.2а и 26 приведена структура реверсивного регистра сдвига 1 для сдвигов в сторону старших и сторону младших разрядов, а на фиг. 2в - временная диаграмма получения выходных отсчетов случайного процесса V(kT).

Таким образом, для построения цифрового генератора широкополосных случайных процессов на реализацию регистра сдвига необходимо использовать т (20-40) триггеров, так как период М-последовательности определяется величиной U 2. Поэтому наиболее приемлемо значение 30. В то же время для реализации регистра сдвига в прототипе необходимо использовать количество триггеров, равное числу точек отсчета п требуе эй S (i)) , Т.е. другими словами 171 п (500-1000) для частиного диапазона 1 Гц-5 кГц. Очевидно что в предлагаемом устройстве реализация регистра сдвига значительно упрощается по сравнению с прототипо Кроме того в прототипе присутствует п устройств умножения, а в предлагаемом устройстве одно, что значительно упрсяляет структуру устройства в целом. Дополнительные же устройства, введенные в цифровой генератор, по своим аппаратурным затратам незначительны.

Для повышения точности воспроизведения спектральной плотности мощности нeoбxoди 40 Незначительно иэкюнить счётчик адреса, дешифратор и оперативную память для того, чтос можно было хранить и. в дальнейшем использовать в цифровом генераторе весовые коэффициент фильтра ЪЦТ}, количество которых превышает п {500-1000). Необходимо отметить, что раэрядность регистра сдвига и

количество устройств умножения при этом не изменяется.

Преимущество предлагаемого цифрового генератора широкополосных случайных процессов заключается в следующем ,

Простота структуры: все узлы генратора реализуются на обычных элементах вычислительной техники по известным типовым схемам. Ориентировочный объем такого генератора составляет четыре типовых элемента замены (ТЭЗа) при использовании интегральных схем серии 155 и серии 500 введя программное управление, легко воспроизводить спектр случайнго процесса с требуемой точностью, путем изменения величины п ,

Применение подобных цифровых генераторов широкополосных случайны процессов, предназначенных для виброиспытаний изделий на случайные воздействия, позволит добиться высоких техникоэкономических показателей .

Формула изобретения

Генератор широкополосных случайн процессов, содержащий регистр сдвига, разрядные входы которого соединены соответственно с первым и вторым выходами блока управления, третий и четвертый выходы которого соединены соответственно с первыми входами умножителя и сумматора, первый выход которого является выходом генератора, а второй вход сумматора соединен с выходом умножителя, второй вход которого соединен с выходом последнего разряда регистра сдвига,: о т л и ч а ющ и и с я тем, что, с целью повышения точности генератора, он содержи первый и второй сумматоры по модулю два, счетчик адреса, блок оперативной памяти, дешифратор и регистр памяти , первый вход и выход которого соединены соответственно со вторым выходом и третьим входом сумматора, а второй вход регистра памяти соединен с выходом Запись блока управления, первый выход которого соединен со входом счетчика адреса, выход которого соединен с первым входом дешифратора, второй вход которого соединен со вторым выходом Опрос блока управления, третий выход Опрос которого соединен с первым входом блока оперативной памяти, второй вход которого соединен с выходом дешифратора, а выход блока оперативной памяти соединен с третьим входомумножителя, выходы и входы первого и последнего разрядов регистра сдвига соединены соответственно с первыми входами и выходам первого и второго сумматоров по модулю два, вторые входы которых

соединены соответственно с j -ым и с (d + 1) выходами регистра сдвига d i -rrt) ,

Источники информации, принятые во вииманне при экспертизе

1. Коваль В.Т. Задающая аппаратура для воспроизведения случайных вибраций при исследования нгшежност

Вестник машиностроения

1970.

2.Верешкин А,А., Катковник В.Я. Линейные цифровые фильтры и методы их реализации. Советское радио , М., 1974, с. 108-109, 131-134.

3.Данилов B.C., Штейнбок М.Г. Однополосная передача цифровых сигналов, Связь, М., 1974, с.56, рис. 3,5 (прототип).

CdSui

CSbui

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор широкополосных случайных процессов | 1980 |

|

SU881743A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Устройство для реализации быстрого преобразования Хартли | 1987 |

|

SU1444815A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Цифровой формирователь спектра | 1984 |

|

SU1171804A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

Авторы

Даты

1980-10-15—Публикация

1978-06-02—Подача