Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях.

Цель изобретения - расширение класса решаемых задач за счет возможности вычисления сложной функции Г-

X x «cos ln(X)- -j sin ln(X) .

На фиг, 1 представлена функцио- нальная схема устройства; на фиг.2 - схема блока управления.

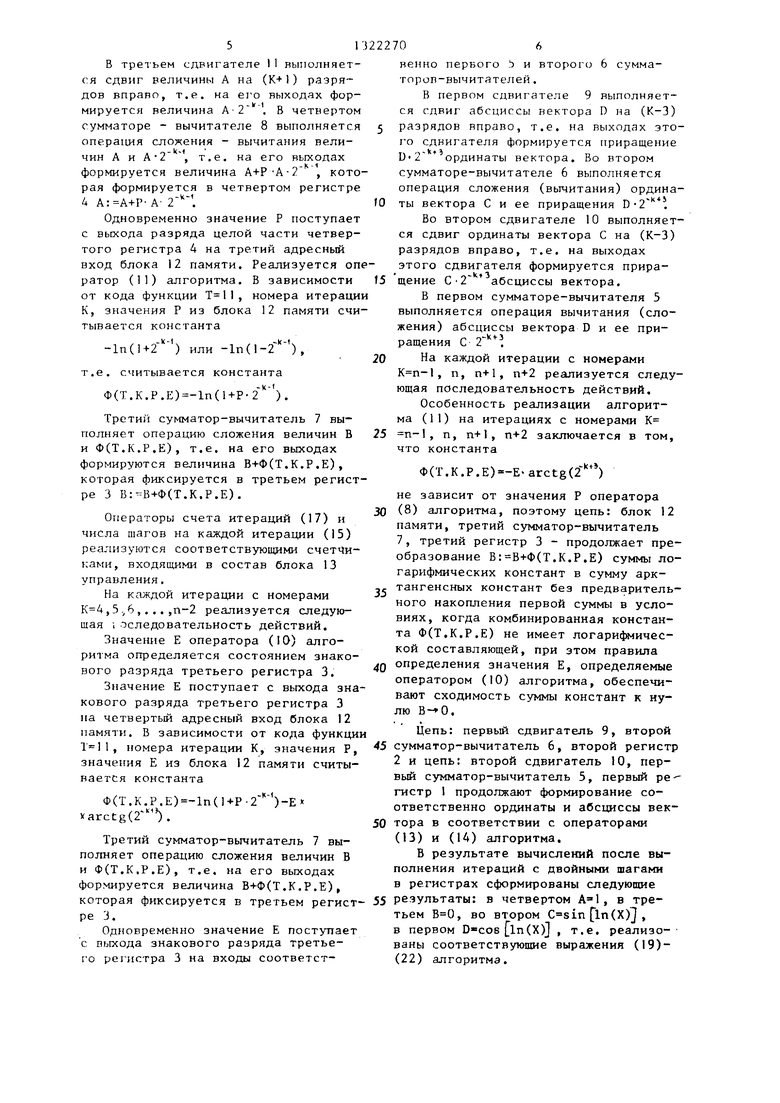

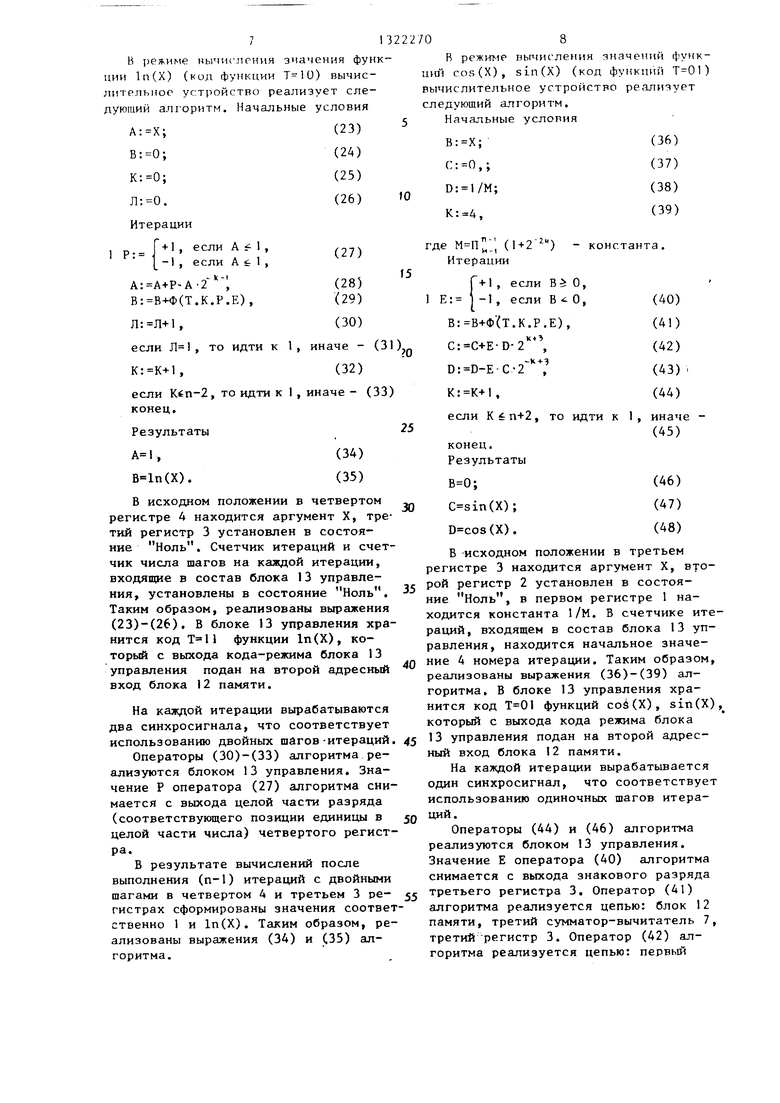

Устройство содержит первый 1, второй 2, третий 3 и четвертый 4 регистры, первый 5, второй 6, третий 7 и четвертый 8 сумматоры-вычитате- ли, первый 9, второй 10 и третий И сдвигатели, блок 12 памяти, блок 13 управления.

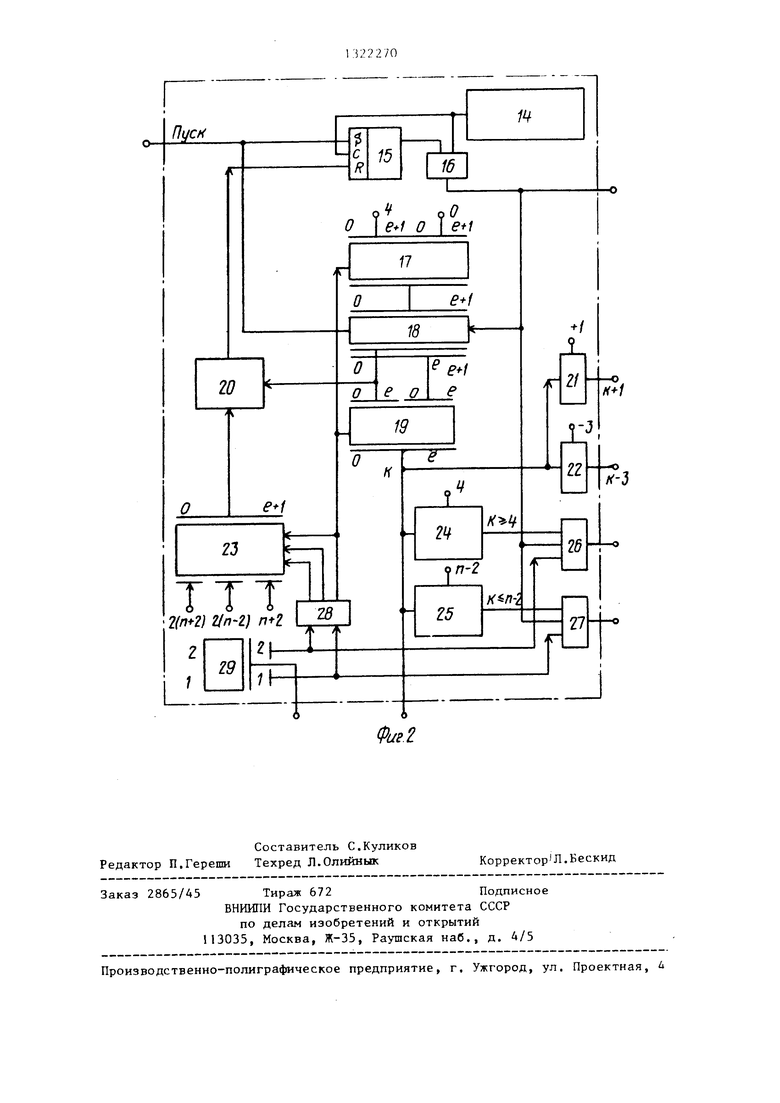

Блок управления содержит генера- тор 1А тактовых импульсов, триггер 15, первый элемент И 16, первый коммутатор 17, счетчик 18, второй коммутатор 19, первую схему 20 сравнения, сумматор 21, вычитатель 22, третий коммутатор 23, вторую 24 и третью 25 схемы сравнения, второй 26 и третий 27 элементы, дешифратор 28, i регистр 29.

Вычислительное устройство работае следующим образом.

Вычислительное устройство может работать в трех режимах: вычисления значения функции X , где 0,5 X I; вычисления значения функции 1п(Х), где 0,5 i: X вычисления значений функций cos (X), sin(X), где -IT/A Xs .

Этим режимам соответствуют следу- ющие коды Т функций: ,1 1 для функции , для функции 1п(Х); , для функции cos (X) , sin(X).

В дАльнейгаем приняты следующие обозначения:

А - переменная алгоритма для преобразования аргумента в единицу при вычислении значений функций X или 1п(Х) ;

В - переменная алгоритма для преобразования суммы логарифмических констант в сумму арктангенсных констант без предварительного накоплени первой при вычислении значения функции Х, для формирования значения функции 1тг(Х) при вычислении этой функции, для преобразования аргумент (угла вектора) в ноль при вычислении значений функций cos(X), sin(X);

С, D - переменные алгоритма для обозначения соответственно ординаты и абсциссы вектора при вычислении значений функций или cos(X), sin(X);

, +ll - оператор направлени итерационного процесса преобразования аргумента в единицу X - I при вычислении значений функции Х или 1п(Х);

Е -1 , +И - оператор направления поворота вектора при вычислении значений функцй Х или cos(X), sin(X);

,1,..,,n-2 - переменная алгоритма - номер выполняемой итерации;

(п-1) - количество выполняемых итераций, количество разрядов в дробной части числа;

п - количество значащих разрядов в представлении числа, включая единичный разряд в целой части числа;

(п+1) - разрядность устройства, разрядность представления числа, вкчая знаковый разряд;

,1 - переменная алгоритма - нмер шага на каждой итерации.

В блоке памяти хранятся констант

При вычислении значения функции Х (код функции ) используются для ,1,2,3,

Ф(Т.К.Р.Е)-1п(1+Р 2 ); для ,5,6,..,п-2;

Ф(Т.К.Р.Е)-1п(1+Р 2 )-Е

arctg( для , п, п-«-1, п+2;

Ф(Т.К.Р.Е)-Е arctg().

При вычислении значения функции 1п(Х) (код функции ) дпя ,1 2,...,п-2 используются следующие константы

Ф(Т.К.Р.Е)-1п(И-Р-2 ).

При вычислении значений функций cos(X), sin(X) (код функции ) для ,5,6,.,.,п+2 используются следующие константы

Ф(Т.К.Р.Е)-Е arctg(2).

При вычислении значений функций X и 1п(Х) используются двойные шаги итераций, а при вычислении значений функций cos(X), sin(X) - одиночные шаги итераций.

В -режиме вычисления значения фунции Х (код функции ) вычисли31

тельное устройство реализует следующий алг орнтм. Начальные условия

(1)

В:-0; (2)

(3)

Д: 1/М;(4)

(5)

,(6)

п-1 -2н V, где (1+2 ) - константа.

Итерации 1 Если , то идти к 2, иначе-(7)

, Г + 1 , если А 1 , L-1, если А 1,

А: А+Р А-2 Е

если ВЬ О, если В «i О,

(8) (9) (10) (И)

(Т.К.Р.Е) Если , то идти к 3, иначе (12)

C: C-t-E-D-2 (13)

D: D-E C-2 (14)

3 ,(15)

Если , то идти к1, иначе - (16)

,(17)

Если К п- -2, то идти к 1, иначе - конец.(18)

Результаты

(19)

(20)

(ln(X) ;(21)

(X) ,(22)

где значения D и С - соответственно .действительная и мнимая части значения функции

(X)+j (X) В исходном положении в че твертом регистре 4 находится аргумент X, в первом регистре I - константа 1/М, второй 2 и третий 3 регистры установлены в состояние ноль, Счетчик итераций и счетчик числа шагов на каждой итерации, входящие в состав бло ка 13 управления, установлены в состояние Ноль.

Таким образом, реализованы выражения (1)-(6). В блоке 13 управления хранится код 1 функции Х , который с выходом кода режима блока 13 управления подан на второй адресный вход блока 12 памяти.

3222704

Блок 13 управления вырабатывает распределенную во времени последовательность сигролов на своих выходах.

На первом тактовом выходе - по- 5 следовательность синхросигналов, подаваемых на синхронизирующие входы первого 1 и второго 2 регистров на итерациях с номерами 4, 5, 6,..., п+2 и разрешаюпщх прием информации 0 в эти регистры.

На выходе величины сдвига - последовательность кодов - указателей сдвига 1,2,3,..,,п-1, подаваемых на одноименные входы первого 9 и второ- J5 го 10 сдвигателей на итерациях с номерами соответственно 4, 5,6,..,п+2.

На втором тактовом выходе последовательность синхросигналов, подаваемых на синхронизирующий вход третье- 20 го регистра 3 и на стробирующий вход блока 12 памяти на итерациях с номерами 0,1,2, . . . ,п+2 и разрешающих прием информации в третий регистр 3 и считьшание констант из блока 12 памя25 тиНа выходе номера итерации - последовательность номеров выполняемых итераций О,1,2,...,п+2, подаваемых на первый адресный вход блока 12 памяти и обеспечивающих выбор константы, соответствующей номеру выполня- емой итерации.

На выходе кода режима постоянно присутствует код вычисляемой функции; подаваемый на второй адресный вход блока 12 памяти.

На выходе модифицированной величины сдвига - последовательность кодов - указателей сдвига 1,2,3,..., п-1, подаваемых на вход величины сдвига третьего сдвигателя 1 1 на

итерациях с номерами соответственно 0,1,2,...,п-2.

На третьем тактовом выходе - последовательность синхросигналов, подаваемых на синхронизирующий вход четвертого регистра 4 на итерациях с номерами О,1,2,...,п-1 и разрешающих прием информации в этот регистр.

На каждой итерации вырабатывают- ся два синхросигнала, что соответствует использованию двойных шагов итераций.

На каждой итерации с номерами 0,1,2,3 реализуется следующая после- 55 довательность действий.

Значение Р оператора (8) алгоритма определяется состоянием разряда целой части четвертого регистра 4.

30

3J

45

50

В третьем сдвигателе I 1 выполняется сдвиг величины А на (K- 1 ) разрядов вправо, т.е. на его выходах фор, -k-l п

мируется величина А-/ .В четвертом сумматоре - вычитателе 8 выполняется операция сложения - вычитания величин А и А 2 , т.е. на его выходах

- к -

формируется величина А+Р А-2 , которая формируется в четвертом регистре 4 А- .

Одновременно значение Р поступает с выхода разряда целой части четвертого регистра 4 на третий адресный вход блока 12 памяти. Реализуется оператор (11) алгоритма. В зависимости f5 щение С2 абсциссы вектора, от кода функции , номера итерации В первом сумматоре-вычитателя 5 К, значения Р из блока 12 памяти счиВо втором сдвигателе 10 выполня ся сдвиг ординаты вектора С на (Кразрядов вправо, т.е. на выходах этого сдвигателя формируется прира

выполняется операция вычитания (сл жения) абсциссы вектора D и ее при ращения С 2.

тывается константа

„-Х-1п(1+2

) или т.е. считывается константа Ф(Т.К.Р.Е)-1п(1+Р 2 ).

Третий сумматор-вычитатель 7 выполняет операцию сложения величин В и Ф(Т.К.Р.Е), т.е. на его выходах формируются величина В+Ф(Т.К.Р,Е), которая фиксируется в третьем регистре 3 В:-В+Ф(Т.К.Р.Е).

Операторы счета итераций (17) и числа шагов на каждой итерации (15) реа. 1изуются соответствующими счетЧи- :aми, входящими в состав блока 13 управления.

На каждой итерации с номерами ,5.,6п-2 реализуется следующая 1 оследовательность действий.

Значение Е оператора (10) алгоритма определяется состоянием знакового разряда третьего регистра 3.

Значение Е поступает с выхода знакового разряда третьего регистра 3 на четвертый адресный вход блока 12 памяти. В зависимости от кода функции

На каждой итерации с номерами , п, п+1, n-t-2 реализуется следующая последовательность действий.

Особенность реализации алгоритма (11) на итерациях с номерами К 25 п-1 , п, п+1, заключается в том, что константа

Ф(Т.К.Р.Е)-Е-агс1§(2)

не зависит от значения Р оператора 30 (8) алгоритма, поэтому цепь: блок 12 памяти, третий сумматор-вычитатель 7, третий регистр 3 - продолжает преобразование (Т.К.Р.Е) суммы логарифмических констант в сумму арк- ,, тангенсных констант без предварительного накопления первой суммы в условиях, когда комбинированная константа Ф(Т,К.Р.Е) не имеет логарифмической составляющей, при этом правила Q определения значения Е, определяемые оператором (10) алгоритма, обеспечивают сходимость суммы констант к нулю .

Цепь: первый сдвигатель 9, второй

, номера итерации К, значения Р, сумматор-вычитатель 6, второй регистр

2 и цепь: второй сдвигатель 10, первый сумматор-вычитатель 5, первый ре-- гистр 1 продолжают формирование соответственно ординаты и абсциссы век- 50 тора в соответствии с операторами (13) и (14) сшгоритма.

В результате вычислений после выполнения итераций с двойными шагами в регистрах сформированы следующие

которая фиксируется в третьем регист- 55 результаты: в четвертом А , в тре- ре 3.тьем , во втором ln(X)J ,

Одновременно значение Е поступает в первом ln(X)J , т.е. реализо- с пыхода знакового разряда третье- ваны соответствующие выражения (19)- го регистра 3 на входы соответст- (22) алгоритма.

значения Е из блока 12 памяти считывается константа

Ф(Т.К.Р.Е)-1п( ) -Е « varctg().

Третий сумматор-вычитатель 7 выполняет операцию сложения величин В и Ф(Т.К.Р.Е), т.е. на его выходах формируется величина В+Ф(Т.К.Р.Е),

щение С2 абсциссы вектора, В первом сумматоре-вычитателя 5

неино первого Ь и второгс; 6 сумма- торов-вычитателей.

В первом сдвигателе 9 выполняется сдвиг абсциссы вектора D на (К-3) разрядов вправо, т.е. на выходах этого сдвигателя формируется гтриращение D 2 ординаты вектора. Во втором сумматоре-вычитателе 6 выполняется операция сложения (вычитания) ординаты вектора С и ее приращения D 2 .

Во втором сдвигателе 10 выполняется сдвиг ординаты вектора С на (К3) разрядов вправо, т.е. на выходах этого сдвигателя формируется прираi kti

щение С2 абсциссы вектора, В первом сумматоре-вычитателя 5

выполняется операция вычитания (сложения) абсциссы вектора D и ее приращения С 2.

На каждой итерации с номерами , п, п+1, n-t-2 реализуется следующая последовательность действий.

Особенность реализации алгоритма (11) на итерациях с номерами К п-1 , п, п+1, заключается в том, что константа

Ф(Т.К.Р.Е)-Е-агс1§(2)

не зависит от значения Р оператора (8) алгоритма, поэтому цепь: блок 12 памяти, третий сумматор-вычитатель 7, третий регистр 3 - продолжает преобразование (Т.К.Р.Е) суммы логарифмических констант в сумму арк- тангенсных констант без предварительного накопления первой суммы в условиях, когда комбинированная константа Ф(Т,К.Р.Е) не имеет логарифмической составляющей, при этом правила определения значения Е, определяемые оператором (10) алгоритма, обеспечивают сходимость суммы констант к нулю .

Цепь: первый сдвигатель 9, второй

713222

В режиме вычисления значения функции 1п(Х) (код функции ) вычислительное устройства реализует следующий алгоритм. Начальные условия

(23)

(24)

(25) (26)

Г-1-1 , если А 1 , ,„,.

11й1 - /

L-1, если А & 1,

(28) (29)

(30)

к1, иначе - (31) (32)

если Ktn-2, то идти к I , иначе - (33) конец.

(34) (35)

В исходном положении в четвертом регистре 4 находится аргумент X, третий регистр 3 установлен в состояние Ноль. Счетчик итераций и счетчик числа шагов на каждой итерации, входящие в состав блока 13 управления, установлены в состояние Ноль. Таким образом, реализованы выражения (23)-(26). В блоке 13 управления хранится код функции 1п(Х), который с выхода кода-режима блока 13 управления подан на второй адресный вход блока 12 памяти.

На каждой итерации вырабатываются два синхросигнала, что соответствует использованию двойных шагов-итераций,

Операторы (ЗО)-(ЗЗ) алгоритма реализуются блоком 13 управления. Значение Р оператора (27) алгоритма снимается с выхода целой части разряда (соответствующего позиции единицы в целой части числа) четвертого регистра,

В результате вычислений после выполнения (п-1) итераций с двойными шагами в четвертом 4 и третьем 3 ре- гистрах сформированы значения соответственно 1 и 1п(Х), Таким образом, реализованы выражения (34) и (35) алгоритма.

/О8

В режиме вычисления значений функ- Ц1Ш cos(X), sin(X) (код функций ) вычислительное устройство реализует следующий алгоритм.

Начальные условия

С: 0,; ,

(36) (37) (38) (39)

где , (1+2 ) - константа. Итерации

Г-И , если Bi О, 1 Е: 1-1 , если В О,

(Т,К,Р.Е),

C: C+E-D-2 D: D-E-C 2 K: K-t-l ,

(40) (41) (42) (43) (44)

если К4П+2, то идти к 1, иначе (45) конец.

Результаты

(46)

(X);

(X),

(47) (48)

0

5

0

5

В -исходном положении в третьем регистре 3 находится аргумент X, второй регистр 2 установлен в состояние Ноль, в первом регистре 1 находится коистанта 1/М, В счетчике итераций, входящем в состав блока 13 управления, находится начальное значение 4 номера итерации. Таким образом, реализованы выражения (36)-(39) алгоритма, В блоке 13 управления хранится код функций coS(X), sin(X), который с выхода кода режима блока 13 управления подан на второй адресный вход блока 12 памяти.

На каждой итерации вырабатывается один синхросигнал, что соответствует использованию одиночных шагов итераций.

Операторы (44) и (46) алгоритма реализуются блоком 13 управления. Значение Е оператора (40) алгоритма снимается с выхода знакового разряда третьего регистра 3, Оператор (41) алгоритма реализуется цепью: блок 12 памяти, третий сумматор-вычитатель 7, третий регистр 3, Оператор (42) алгоритма реализуется цепью: первый

913

сдвигатель 7, второй сумматор-вычнта- тель 6, второй регистр 2, Оператор (A3) алгоритма реализуется цепью: второй сдвигатель 10, первый сумма- тор-вычитатель 5, первый регистр 1.

В результате вычислений после выполнения (п-1) итераций с одиночными шагами в третьем 3, втором 2, первом I регистрах сформированы значения соответственно О, sin(X), cos(X). Таким образом, реализованы выражения (46)-(48) алгоритма.

Блок управления функционирует следующим образом.

До начала работы блока управления в регистр 29 записывается код Т вычисляемой функции. По сигналу Пуск в счетчик 18 через первый коммутатор 17 заносится начальное значение 6 для функций 1п(Х), либо 4 для функций cos(X), sin(X).

По сигналу Пуск триггер 15 устанавливается в состояние Лог. 1 и разрешает прохождение синхроимпульсов с выхода генератора 14 через первый элемент И 16 на второй тактовый выход блока управления, на счетный вход счетчика 18 и на вход второго 26 и третьего 27 элементов И.

На выходах регистра 29, т.е. на выходе кода режима блока управления постоянно присутствует код Т вычисляемой функции.

При вычислении значения функции X или 1п(Х) используются двойные шаги итераций, соответственно номер шага на каждой итерации Л определяется состоянием младшего, т.е. (е+1)-го разряда счетчика 18, Второй коммутатор I9 обеспечивает формирование номера К выполняемой итерации в режимах вычисления значений функций Х и 1п(Х) - двойные иаги итераций, и в режиме вычисления значений функций cos(X), sin(X) - одиночные шаги ите- раций.

Третий коммутатор 23, управляемый дешифратором 28, обеспечивает .выдачу общего числа шагов итераций 2 (п+2), либо 2 (п-2), либо при вычисле- НИИ значений функций соответственно X-f, либо 1п(Х), либо cos(X), sin(X) на первую схему 20 сравнения, которая сравнивает это число с текущим номером шага от начала вычислений, форми- руемым счетчиком 18. При достижении заданного числа шагов итераций схема 20 сравнения устанавливает триггер 15 в состояние Лог. О, при этом

010

трип ер 15 блокирует передачу синхроимпульсов через первый элемент И 16. Вычисления закончены.

Номер К вьтолняемой итерации с выходов второго коммутатора 19 поступает на выход номера итерации блока управления, в сумматор 21 и в вычи- татель 22, где складывается с константами соответственно +1 и -3.

Вторая и третья схемы 24 и 25 сравнения разрешают выдачу синхросигналов через соответствующие элементы И 26 и 27 на первый и третий тактовые выходы блока управления на итерациях с номерами К 4 и К е п-2 соответственно.

Формула изобретения

вычислительное устройство, содержащее три регистра, три сумматора-вы- читателя, два сдвигателя, блок памяти и блок управления, причем информационные выходы первого, второго и третьего регистров соединены с первыми информационными входами соответствен-, но первого, второго и третьего сум- маторов-вычи.слителей, выходы которых соединены с информационными входами соответственно первого, второго и третьего регистров, информационные выходы первого и второго регистров соединены с информационными входами соответственно первого и второго сдвигателей, выходы которых соединены с вторыми информационными входами соответственно второго и первого сум- маторов-вычитателей, выход блока памяти соединен с вторым информационным входом третьего сумматора-вычитателя, выход знакового разряда третьего регистра соединен с управляющими входами первого и второго сумматоров-вы- читателей, первый тактовый выход блока управления соединен с синхронизирующими входами первого и второго регистров, выход величины сдвига блока управления соединен с одноименными входами первого и второго сдвигателей, второй тактовый выход блока управления соединен с синхронизирующим входом третьего регистра и стробирую- щим входом блока памяти, выход номера итерации блока управления соединен с первым адресным входом блока памяти, отличающееся тем, что, с целью расширения класса , решаемых задач за счет возможности вычисления cos ln(x) (x), в

него внелсиы четвертый регистр, четвертый пумматор-вычитатель, третий сдвигатель, а блок управления содержит генератор тактовых импульсов, счетчик, три коммутатора, три схемы сравнения, сумматор, вычитатель, дешифратор, тригтер, регистр и три элемента И, причем вход запуска устройства соединен с одноименным входом блока управления, выход кода режима блока управления соединен с вторым адресным входом блока памяти, выход модифицированной величины сдвига блока управления соединен с входом величины сдвига третьего сдвигателя, ин- форма1и1оннь й вход которого соединен с информационным выходом четвертого регистра, информационный вход которого соединен с выходом четвертого сумматора-вычитателя, первый и второй информационные входы которого содинены с выходами четвертого регистра и третьего сдвигателя соответственно, управляющий вход четвертого сумматора-вычитателя соединен с выходом разряда целой части четвертого регистра и с третьим адресным входом блока памяти, четвертый адресный вхо которого соединен с выходом знаково

го разряда третьего регистра, синхро-зо го коммутатора, информационные входы

яизирующий вход четвертого регистра соединен с третьим тактовым выходом блока управления, причем вход запуска блока управления соединен с входом установки триггера и с входом записи счетчика, выход триггера соединен с первым входом первого элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, выход первого злемента И соединен с вторым тактовым выходом блока управления, со счетным входом счетчика и с первыми входами второго и третьего элементов И, информационный

вход счетчика соединен с выходом пер- слагаемого сумматора и вход вычитаевого коммутатора,, первый и второй информационные-входы которого соединены с первым и вторым входами задамого вычитателя соедииены соответственно с третьим и четвертым входами задания констант блока управления.

fO

52227012

ння констант блока упраилгния соответственно, управляющий вход первого коммутатора соединен г первым выходом дешифратора и с у подавляющим входом второго коммутатора, выход разрядов счетчика соединен с первь м входом первой схемы сравнения и с первым информационным входом второго коммутатора, второй информационньй вход которого соединен с выходом старших разрядов счетчика, вьгеод второго коммутатора соединен с выходом номера итерации блока управления и с входом первого слагаемого сумматора, с входом уменьшаемого вычитателя, с первыми входами второй и третьей схем сравнения, вторые входы которых соединены с входами граничных значений итерации блока управления, выходы признаков больше и меньше соответственно второй и третьей схемы сравнения соединены с вторыми входами соответственно второго и третьего элементов И, третьи входы которых соединены с выходами разрядов регистра, выход регистра соединен с выходом кода режима блока управления и с входом дешифратора, выходы которого соединены с управляющими входами третье20

25

5

0

которого соединены с соответствующими входами значений останова вычислений блока управления, выход третьего коммутатора соединен с вторым входом первой схемы сравнения, выход признака больше которой соединен с входом сброса триггера, выходы второго и третьего элементов И соединены соответственно с первым и третьим тактовыми выходами блока управления, выходы вычитателя и сумматора соединены соответственно с выходами величииы сдвига, и модифицированной величины сдвига блока управления, вход второго

мого вычитателя соедииены соответственно с третьим и четвертым входами задания констант блока управления.

о

О О е+1

о т

18

о

/ i,

2/

19

9-J

23

ТУТ

ооо I 7Q

) г/п-2) I .

f /1

h

L

к

А

гг

26

.

L

- 27

яи

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления эллиптических функций | 1987 |

|

SU1474641A2 |

| Устройство для вычисления функций | 1986 |

|

SU1374219A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1987 |

|

SU1497615A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1370653A1 |

| Цифровой преобразователь координат | 1981 |

|

SU1076903A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для вычисления обратного гиперболического тангенса | 1987 |

|

SU1456952A1 |

| Вычислительное устройство для поворота вектора | 1987 |

|

SU1520511A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Цифровое устройство для вычисления синусно-косинусных функций | 1980 |

|

SU926651A1 |

Изобретение относится к Bbi Oic- лительной технике и может быть использовано автоноьшо в качестве специализированного вычислителя или в качестве функционального расширителя в составе больших ЭВМ. Целью изобретения является расширение класса решаемых задач за счет возможности вычисления сложной функции X Х- cos(lnX)+jsin(ln(X)) и остальных ее компонент cosX, sinX, InX. Устройство содержит регистры 1-4, сум- маторы-вьгчитатели 5-8, сдвигатели 9-И, блок 12 памяти, блок 13 управления. Код режима задается в блоке управления, в котором в зависимости от этого хода происходят настройка на количество итерации и выборка сот ответствующих констант из блока памяти. Сдвигатели, сумматоры-вычита- тели и регистры реализуют итерационные алгоритмы поворота вектора. 2 ил. (Л

Составитель С.Куликов Редактор П.Гереши Техред Л.Олийнык

Заказ 2865/45 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Корректор Л.Бескид

| Устройство для вычисления элементарных функций | 1977 |

|

SU703823A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Volaer I.E | |||

| The Cordic trigonometric computing technique - IRE Trans | |||

| Comput | |||

| Автоматический сцепной прибор американского типа | 1925 |

|

SU1959A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Катодная трубка Брауна | 1922 |

|

SU330A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-19—Подача