Изобретение относится к вычислительной технике и может быть использовано в цифроаналоговых вычислитель ных и моделирующих системах. Известны цифровые микропроцессоры состоящие из цифровых, коммутирующих запоминающих и арифметикологических блоков и позволяющие за счет микропрограммирования формировать широк набор логических и вычислительных функций 1 . Основным недостатком цифровых мик ропроцессоров за счет последовательного принципа функционирования является малое быстродействие при вычислении сложных функций, например от многих переменных. Наиболее близким по технической сущности и достигаемому результату к изобретению является цифроаналого вое устройство, содержащее управляющий регистр, набор вычислительных и функциональных блоков, коммутатор входов, коммутатор выходов и коммутатор соединений блоков . Однако такому устройству присущ большой объем оборудования. Цель, изобретения - сокращение оборудования. . Поставленная цель достигается тем, ;что в цифроаналоговый микропроцессор,, содержащий функциональный преобразователь и блок вычислений вектора, дополнительно введены суммирующий усилитель и блок формирования уровня напряжения, причем первый вход микропроцессора соединен с первыми входами блока вычислений вектора и суммирующего усилителя, первый и второй выходы блока вычислений вектора являются соответственно первым и вторым выходами микропроцессорау тржтий ВЫХОД которого соединен с выходом сумг мирующего усилителя, со вторыми входами функционального преобразователя и блока вычислений вектора и с входом блока формирования уровня напряжения первый выход блока вычислений Belcxoра соединен со вторым входом суммирующего усилителя, третий вход которого соединен с выходом функционального преобразователя и четвертым выходом микропроцессора, второй вход которого соединен с управляющими входами суммирующего усилителя и функционального преобразователя и блока вычислений вектора, третий вход которого соединен с выходом блока формирования уровня напряжения.

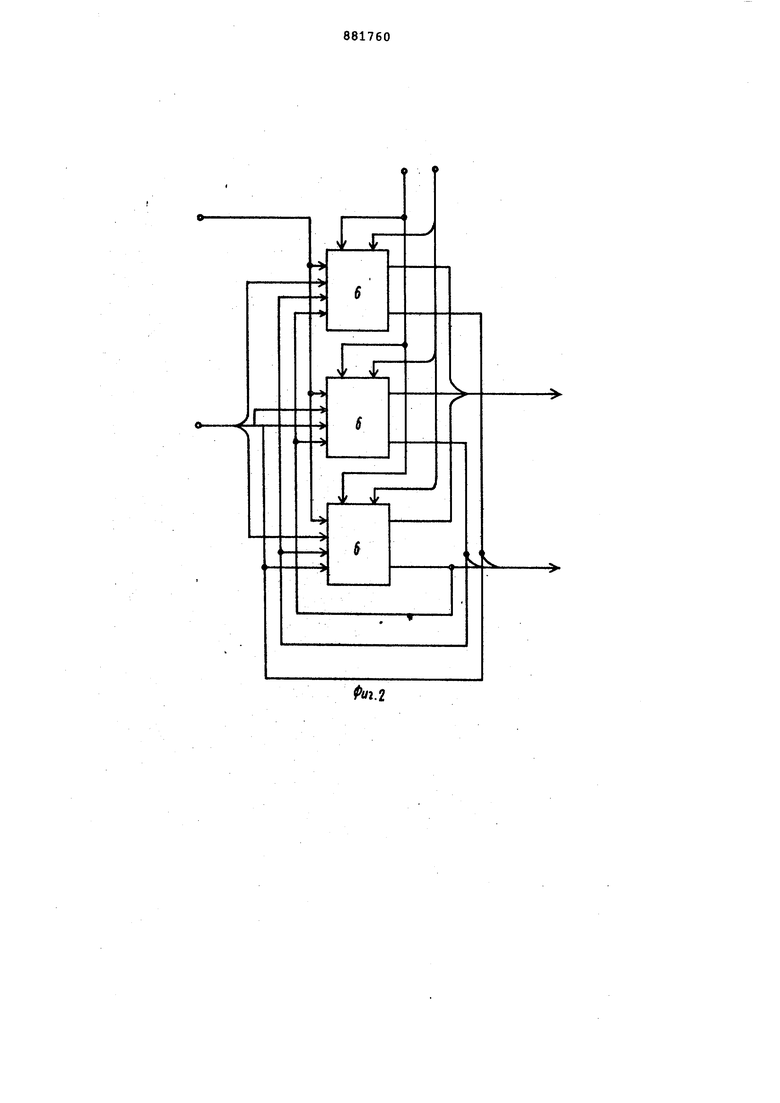

Кроме того, блок вычислений вектора содержит три решающих узла, причем первый и в.торой входы каждого решающего узла соединены с первым и вторым входами блока cooтвeтcтвeннo третий вход каждого решающего узла соединен с третьим входом блока/, четвертый вход каждого решающего узла соединен с управляющим входом блока, первые выходы решающих узлов соединены с первым выходом блока, пятые входы первого и третьего решающих узлов соединены со вторым выходом второго решающего узла, пятый вход второго и шестой вход третьего решающих узлов соединены с выходом первого решающего узла, шестые входы первого и второго решающих узлов соединены с выходом третьего рещающего узла, вторые выходы решающих узлов соединены со вторым выходом блока. Каждый решающий узел содержит три сумматора, умножитель, три коммутатора , причем первые входы первого и второго сумматоров соединены с третьим входом узла, вторые входы первого и второго сумматоров соединены с выходом умножителя, первый вход умножителя соединен с первым входом узла, второй вход умножителя соединен с выходом третьего сумматора, первый, второй и третий входы третьего сумматора соединены с выходами первого и третьего коммутаторов соответственно, первый, второй входы первого и третьего коммутаторов соединены со вторым и .четвертым входами узла соответственно, первый, второй входы второго коммутатора соединены с выходом второго сумматора, третьи входы коммутаторов соединены с пятым входом узла, четвертые входы коммутаторов соединены с шестым входом узла.

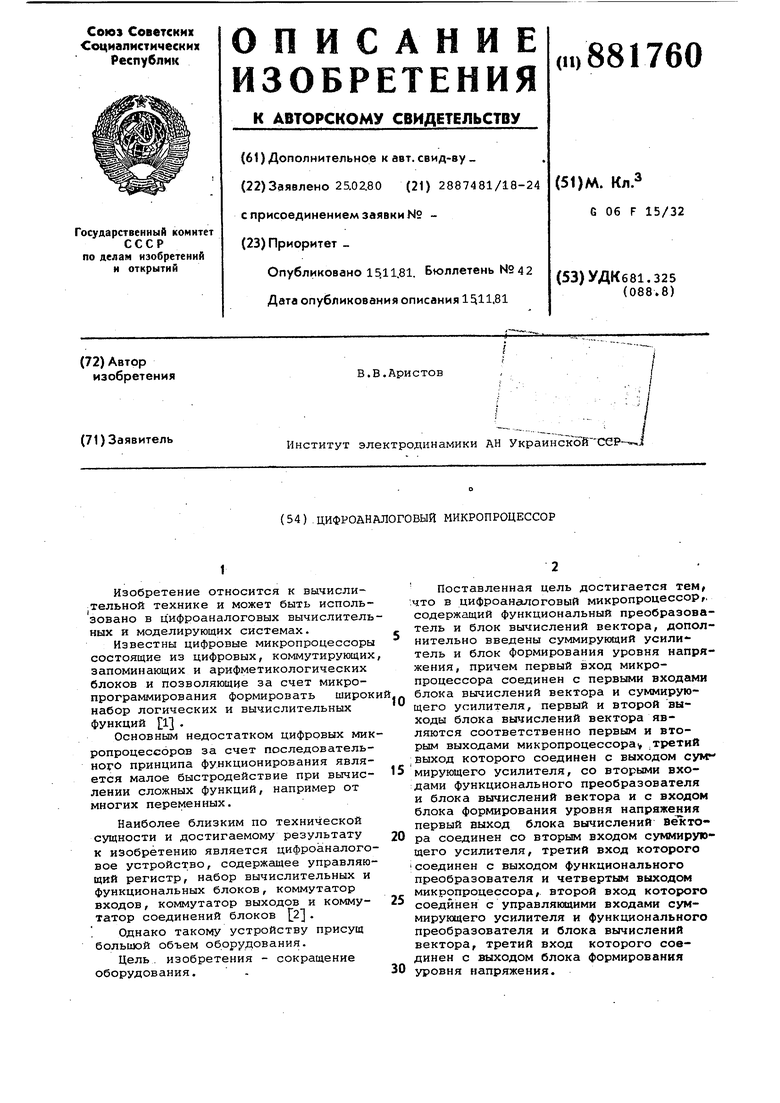

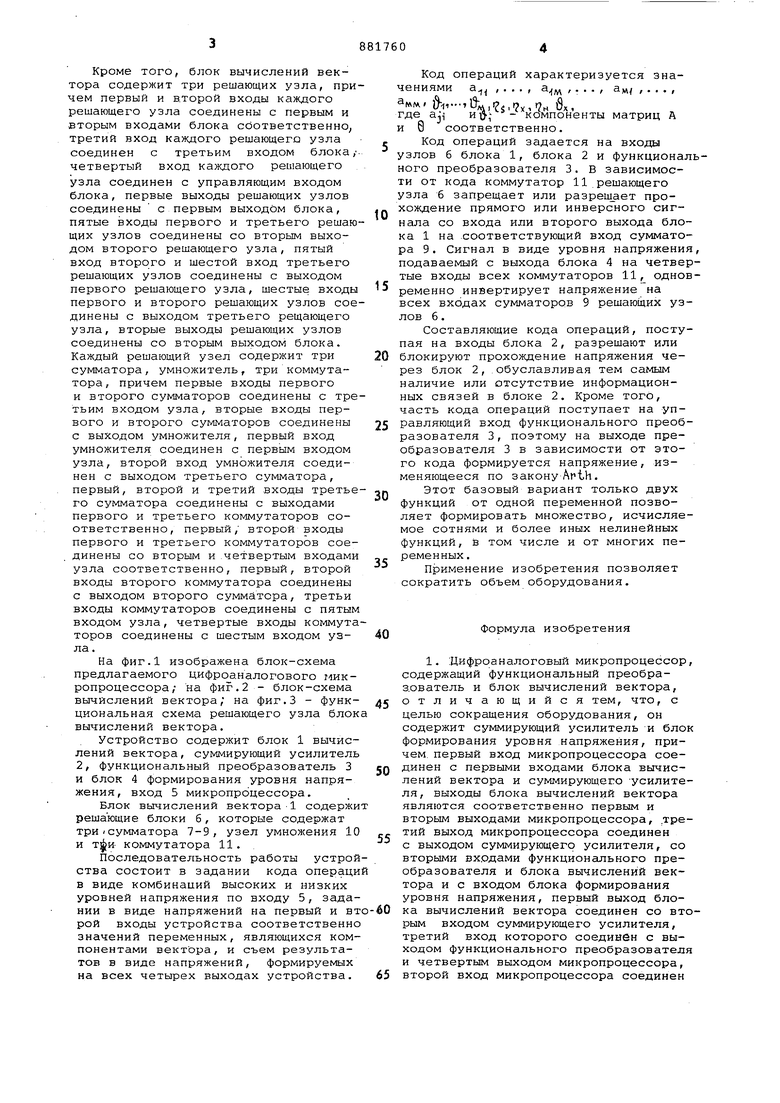

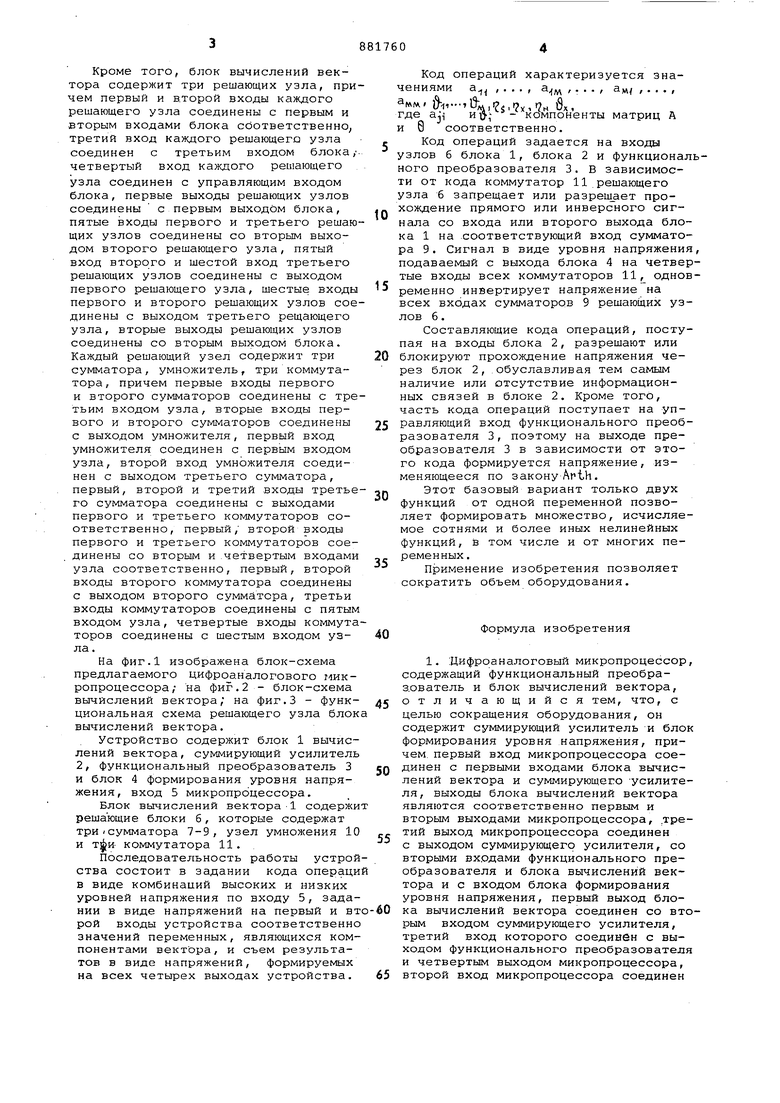

На фиг.1 изображена блок-схема предлагаемого цифроаналогового микропроцессора; на фиг. 2 - блок-схема вычислений вектора; на фиг.З - функциональная схема решающего узла блок вычислений вектора.

Устройство содержит блок 1 вычислений вектора, суммирующий усилитель 2, функциональный преобразователь 3 и блок 4 формирования уровня напряжения, вход 5 микропроцессора.

Блок вычислений вектора содержи решающие блоки б, которые содержат триСумматора 7-9, узел умножения 10 и тфи- коммутатора 11. ,

Последовательность работы устройства состоит в задании кода операци в виде комбинаций высоких и низких уровней напряжения по входу 5, задании в виде напряжений на первый и вт рой входы устройства соответственно значений переменных, являющихся компонентами вектора, и съем результатов в виде напряжений, формируемых на всех четырех выходах устройства.

Код операций характеризуется значениями

Эм/

Ш

енимми а , . . . ,

)-I l3M,S,x, l9, де aji ит}; - компо

поненты матриц А

где

и 9 соответственно. с Код операций задается на входы

узлов 6 блока 1, блока 2 и функционального преобразователя 3. В зависимости от кода коммутатор 11 решающего узла 6 запрещает или разреш ает прохождение прямого или инверсного сигнала со входа или второго выхода блока 1 на соответствующий вход сумматора 9. Сигнал в виде уровня напряжения, подаваемый с выхода блока 4 на четвертые входы всех коммутаторов 11, одновременно инвертирует напряжение на

всех входах сумматоров 9 решающих узлов 6.

Составляющие кода операций, поступая на входы блока 2, разрешают или

0 блокируют прохождение напряжения через блок 2,.обуславливая тем самым наличие или отсутствие информационных связей в блоке 2. Кроме того, часть кода операций поступает на управляющий вход функционального преобразователя 3, поэтому на выходе преобразователя 3 в зависимости от этого кода формируется напряжение, изменяющееся по закону Afth.

Этот базовый вариант только двух функций от одной переменной позволяет формировать множество, исчисляемое сотнями и более иных нелинейных функций, в том числе и от многих переменных .

Применение изобретения позволяет сократить объем оборудования.

Формула изобретения

1. :Цифроаналоговый микропроцессор, содержащий функциональный преобрааователь и блок вычислений вектора,

отличающийся тем, что, с целью сокращения оборудования, он содержит суммирующий усилитель и блок формирования уровня напряжения, причем первый вход микропроцессора соединен с первыми входами блока вычислений вектора и суммирующего -усилителя, выходы блока вычислений вектора являются соответственно первым и вторым выходами микропроцессора, третий выход микропроцессора соединен с выходом суммирующего усилителя, со вторыми входами функционального преобразователя и блока вычислений вектора и с входом блока формирования уровня напряжения, первый выход блока вычислений вектора соединен со вторым входом суммирующего усилителя, третий вход которого соединен с выходом функционального преобразователя и четвертым выходом микропроцессора,

второй вход микропроцессора соединен

с управляющими входами суммирующего усилителя и функционального преобразователя и блока вычислений вектора, третий вход которого соединен с выходом блока формирования уровня напряжения.

2.Микропроцессор по п.1, от лич.ающийся тем, что блок вычислений векторов содержит три решающих узла, причем первый и второй входы каждого решающего узла соединены

с первым и вторым входами блока соответственно, третий вход каждого решающего узла соединен с третьим входом блока, четвертый вход каждого решающего узла соединен с управляющим входом блока, первые выходы решающих узлов соединены с первым выходом блока, пятые входы первого и третьего решающих узлов соединены со вторым выходом второго решающего узла, пятый вход второго и шестой вход третьего решающих узлов соединены с выходом первого решающего узла, шестые входы первого и второго решающих, узлов соединены с выходом третьего решающего узла, вторые входы решающих узлов соединены со вторым выходом блока.

3.Микропроцессор по п.1, о т л ичающийся тем, что каждый решающий узел содержит три сумматора умножитель и три коммутатора, причем первые входы первого и второго сумматоров соединены с третьим входом узла, вторые входы первого и второго сумматоров соединены с выходом умножителя, первый вход умножителя соединён с первым входом узла, второй вход умножителя сЪединен с выходом третьего сумматора, первый, второй и третий входы третьего сумматора сое0динены с выходами первого и третье,го коммутаторов соответственно, первый, второй входы первого и третьего коммутаторов соединены со вторялм и четвертым входами узла соответствен5но, первый, второй входы второго коммутатора соединены с выходом второго сумматора, третьи вхяды коммутаторов соединены с пятым входом узла, четвертые входы коммутаторов

0 соединены с шестым входом узла.

Источники информации, принятые во внимание при экспертизе

1.Микроэлектроника и полупроводниковые приборы. Сб., вып.4, М., Советское радио, 1979, с. 11.

5

2.Смолов В.Б., Фамичев B.C. Аналого-цифровые и цифро-аналоговые нелинейные вычислительные устройства. Л., энергия, 1974, с.74-75, рис.3-10а (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования дифференциальных уравнений | 1989 |

|

SU1727130A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1985 |

|

SU1316027A1 |

| Вентильный электропривод | 1987 |

|

SU1635243A1 |

| СИСТЕМА УПРАВЛЕНИЯ МАШИНОЙ ДВОЙНОГО ПИТАНИЯ | 1995 |

|

RU2106055C1 |

| Устройство для отображения дугОКРужНОСТЕй и эллипСОВ HA эКРАНЕэлЕКТРОННО-лучЕВОй ТРубКи | 1978 |

|

SU807264A1 |

| Устройство для измерения параметров трехфазной сети | 1985 |

|

SU1307396A1 |

| Устройство для формирования вектора на экране электронно-лучевой трубки | 1982 |

|

SU1016816A2 |

| Устройство измерения вебер-амперных характеристик электротехнических устройств | 2016 |

|

RU2627559C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

Авторы

Даты

1981-11-15—Публикация

1980-02-25—Подача