Изобретение относится к вычислительной технике, а именно, к вычисл тельным устройствам последовательног типа, оперирующими с аналоговой и цифровой формами представления инфор мации. Изобретениеможет быть исполь зовано в системах -автоматического управления разнообразных рбъектов. Известно устройство, которое держит набор входных и выходных ключей (-.мультиплексоров ), цифровое программное устройство,управляющее мультиплексорами , арифметическое устройст во, представленное набором анашогхэвых и н те гр аторов, и ан ало го вые з апрми нающи элементы для хранения результатов промежуточных вычислений и выходных величин 1 . Недостаток известного устройства заключается в низком быстродействии и невысокой точности вычисления. Наиболее близким по технической сущности к изобретению является рекурсивное вычислительное устройство, в котором входной мультиплексор через кодоуправляемую матрицу, выполняющую роль умножающего цифро-анёшогового преобразователя, соединен с операционным усилителем, имеющим эле мент (резистор) обратной связи, входящий в сюстав этой кодоуправляемой матрицы, выход операционного усилителя через выходной мультиплексор соединен со входами запоминающих элементов. Выходы запоминающих элементов соединены со входами исполнительных элементов и со входами входного мультиплексора. Часть входного мультиплексора соединена с датчиками сигналов в аналоговс форме, а кодовые входам кодоуправляемой матрицы подключены к датчикам сигналов в цифровой форме или (для констант) к прогреилиетому устройству. Работой всего вычислительного устройства управляет цифровое программное устройство, подключенное к управлякицим входам входного и выходного мультиплексоров и запоминающих элементов 2. Однако низкая точность устройства определяется включением запоминающих элементов последовательно с операционным усилителем, т.е. разомкнутым характером построения схеил устройства. Низкое быстродействие определя:ется пассивным зарядом конденсатора запоминающего элемента через внутреннее сопротивление выходного .мультиплексора от генератора напряжения,каким является операционный усилитель, включенный на выходе кодоуправляемой матрицы.

Цель изобретения - повьииение точности и быстродействия.

Цель достигается тем, что рекурсивное вычислительное устройство, содержацее первый мультиплексор, первая группа входов которого является группой аналоговых входов устройства выход первого мультиплексора соейннен с первым аналоговым входом умножающего цифро-аналогового преобразователя, цифровые входы которого через второй мультиплексор связаны с группой цифровых входов устройства, выход умножающего цифро-аналогового преобразователя соединен с входом операционного усилителя,выход которого через третий мультиплексор связан с входами аналоговых запоминающих элементов, выходы которых являющиеся выходами устройства, соединены с второй группой входов первого мультиплексора, управляющие входы мультиплексоров и аналоговых запоминающих элементов соединены с выходами блока синхронизации, содержащий четвертый мультиплексор, к со ответствующим входам которого подключены выходы аналоговых запоминающих ячеек и выход операционного усилителя, управляющий вход четвертого мультиплексора соединен с выходом блока синхронизации, а выход - с вторым аналоговым входом умножающего цифро-аналогового преобразователя.

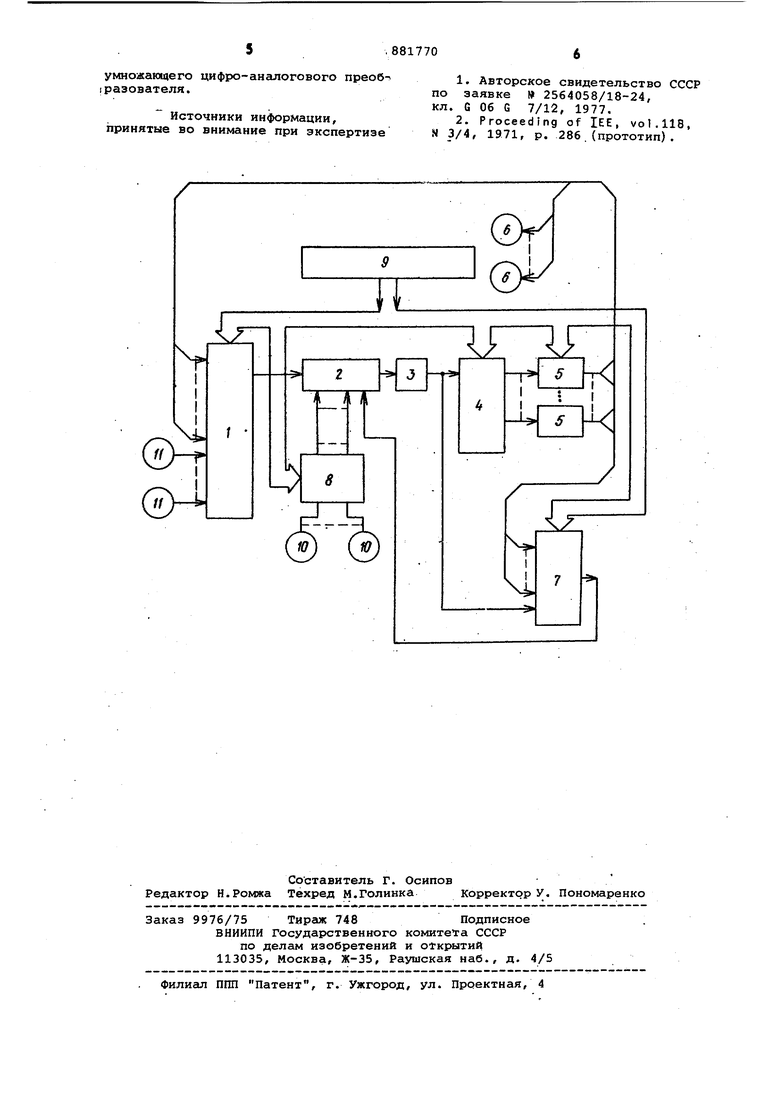

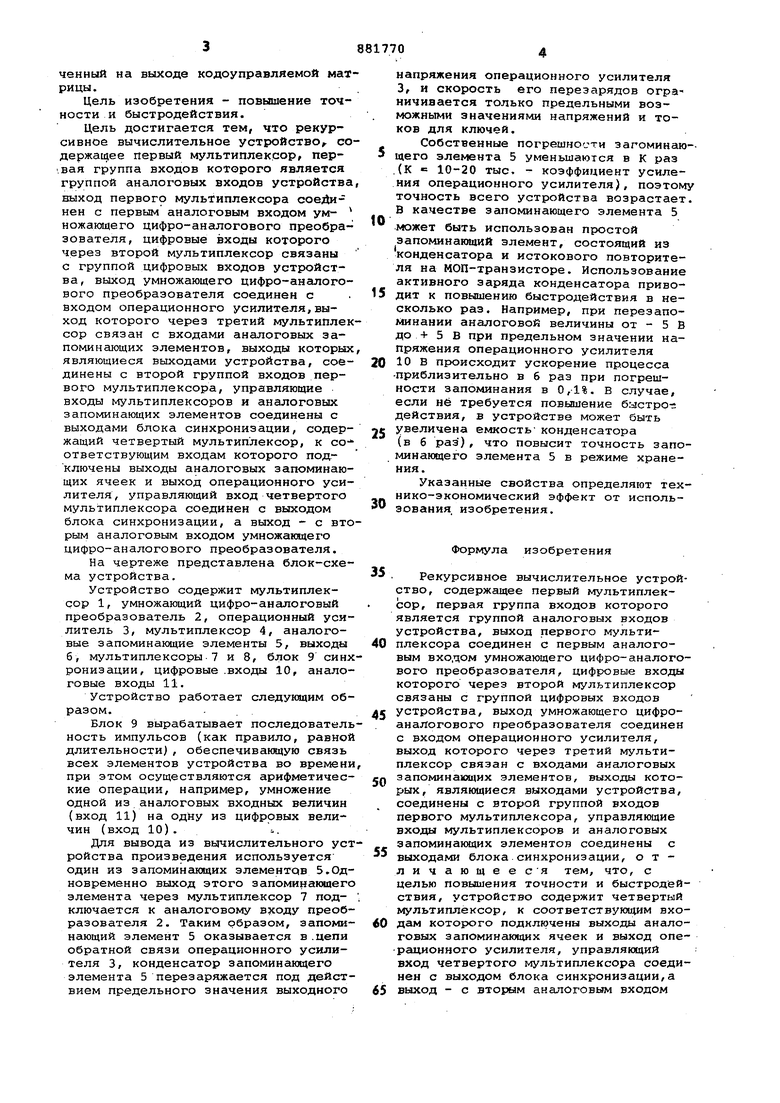

На чертеже представлена блок-схема устройства.

Устройство содержит мультиплексор 1, умножающий цифро-аналоговый преобразователь 2, операционный усилитель 3, мультиплексор 4, аналоговые запоминающие элементы 5, выходы 6, мультиплексоры.7 и 8, блок 9 синхронизации, цифровые .входы 10, аналоговые входы 11.

Устройство работает следукяцим образом.. .

Блок 9 вырабатывает последовательность импульсов (как правило, равной длительности), обеспечивающую связь всех элементов устройства во времени при этом осуществляются арифметические операции, например, умножение одной из аналоговых входных величин (вход 11) на одну из цифровых величин (вход 10).

Для вывода из вычислительного устройства произведения используется один из запомингиощих элементов 5..Одновременно выход этого запоминающего элемента через мультиплексор 7 подключается к аналоговому входу преобразователя 2. Таким образом, запоминающий элемент 5 оказывается в.цепи обратной связи операционного усилителя 3, конденсатор запоминающего элемента 5 перезаряжается под действием предельного значения выходного

напряжения операционного усилителя 3, и скорость его перезарядов ограничивается только предельными возможными значениями напряжений и токов для ключей.

Собственные погрешности запоминаю щего элемента 5 уменьшаются в К раз .(К 10-20 тыс. - коэффициент усиления операционного усилителя), поэтом точность всего устройства возрастает В качестве запоминающего элемента 5

может быть использован простой запоминающий элемент, состоящий из конденсатора и истокового повторителя на МОП-транзисторе. Использование активного заряда конденсатора приводит к повышению быстродействия в несколько раз. Например, при перезапоминании аналоговой величины от - 5 В до + 5 В при предельном значении напряжения операционного усилителя 10 В происходит ускорение процесса приблизительно в 6 раз при погрешности запоминания в 0,1%. В случае, если не требуется повышение быстродействия, в устройстве может быть увеличена емкость конденсатора (в б раз) , что повысит точность запоминающего элемента 5 в режиме хранения.

Указанные свойства определяют технико-экономический эффект от использования, изобретения.

Формула изобретения

Рекурсивное вычислительное устройство, содержащее первый мультиплексор, первая группа входов которого является группой аналоговых входов устройства, выход первого мультиплексора соединен с первым аналоговым входом умножающего цифро-аналогового преобразователя, цифровые входы которого через второй мультиплексор связаны с группой цифровых входов

5 устройства, выход умножающего цифроаналогового преобразователя соединен с входом операционного усилителя, выход которого через третий мультиплексор связан с входами аналоговых эапоминакяиих элементов, выходы которых, являющиеся выходами устройства, соединены с второй группой входов первого мультиплексора, управляющие входы мультиплексоров и аналоговых запоминающих элементов соединены с выходами блока синхронизации, о т личающееся тем, что, с целью повышения точности и быстродействия, устройство содержит четвертый мультиплексор, к соответствующим входам которого подключены выходы аналоговых запоминающих ячеек и выход операционного усилителя, управляющий вход четвертого мультиплексора соединен с выходом блока синхронизации,а

5 выход - с вторым аналоговым входом

умножающего цифрю-аналогового преоб(разователя.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР по заявке w 2564058/18-24,

кл. G Об G 7/12, 1977.

2.Proceeding of lEE, vol.118, S 3/4, 1971, p. 286.(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВАЯ МНОГОПРОЦЕССОРНАЯ СИСТЕМА | 2006 |

|

RU2333533C1 |

| Цифроаналоговый измеритель средней частоты | 1991 |

|

SU1775678A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Устройство для определения модуля @ -мерного вектора | 1987 |

|

SU1481806A1 |

| Блок кодоуправляемого сопротивления | 1989 |

|

SU1599872A1 |

| Умножающий цифро-аналоговый преобразователь | 1985 |

|

SU1312738A1 |

| Цифроаналоговая вычислительная система | 1987 |

|

SU1483468A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ИЗМЕНЕНИЯ СОПРОТИВЛЕНИЯ РЕЗИСТИВНЫХ ДАТЧИКОВ В ЭЛЕКТРИЧЕСКИЙ СИГНАЛ | 2010 |

|

RU2499237C2 |

| Устройство для контроля напряжения электропитания | 1991 |

|

SU1784982A1 |

If

II

Авторы

Даты

1981-11-15—Публикация

1980-01-03—Подача