(5) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПЕЙСМЕКЕРНОГО НЕЙРОНА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования зрительной аккомодации | 1980 |

|

SU955119A1 |

| Устройство для моделирования пейсмекерного нейрона | 1981 |

|

SU982028A2 |

| Устройство для моделирования нейрона | 1980 |

|

SU955118A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОНА | 1991 |

|

RU2024059C1 |

| Устройство для моделирования нейронных ансамблей | 1982 |

|

SU1064285A1 |

| Устройство контроля пробивного напряжения МДП-структур | 1980 |

|

SU958986A1 |

| Устройство для моделирования ритмов гормональной регуляции | 1980 |

|

SU934508A1 |

| Устройство для моделирования условно-рефлекторных связей | 1980 |

|

SU957236A1 |

| Амплитудно-фазовый анализатор гармоник периодических напряжений | 1985 |

|

SU1303950A2 |

| Дифференцирующее устройство | 1983 |

|

SU1120361A1 |

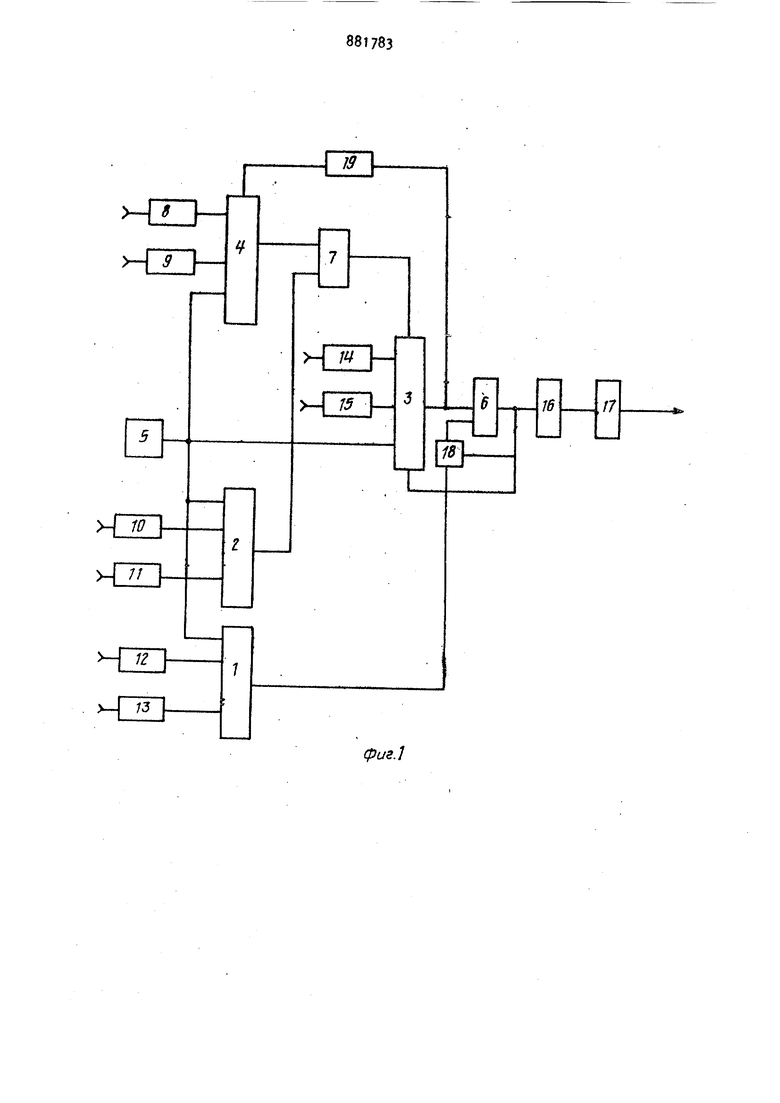

Изобретение относится к аналоговому моделированию и предназначено для использования в самоорганизующихся и самообучающихся системах, а также для кодирования информации в система х разпознавания образов Известно устройство для моделирования нейронной сети пространственного распознавания образов, содержащее параллельно соединенные блоки распознавания, каждый из которых состоит из трех групп нейронных элементов, В устройстве каждый блок распознавания определяет направление движения образа и информация об образе поступает на параллельные выходы устройства. На данном устройстве можно моделировать распознавание любого типа движения образа и при этом входная индивидуаль ность сигналов, характеризующаяся перемещением образа, сопровождается образованием на выходах устройства. выходного разнообразия, которое всегда соответствует по своей индивидуальности входному разнообразию D3« Недостатком известногр устройства является отсутствие собственных-механизмов ритмообразования и дискретизации последовательностей на выходах. Наиболее близким к предлагаемому является устройство для моделирования нейрона, содержащее преобразователи частоты в напряжение, сумматор, блок сравнения, преобразователь напряжения в частоту и блок формирования выходных импульсов 2.. Однако устройство не позволяет моделировать ритмоводящие механизмы центральной нервной системы. Цель изобретения - расширение функциональных возможностей за счет учета ритмоводяр их механизмов центральной нервной системы. Поставленная цель достигается тем, что в устройство, содержащее,первый и второй преобразователи частоты в напряжение, выходы которых соединены соответственно с первым и вторым входом перзого сумматора, первый блок сравнения, выход которого через преобразователь напряжения в частоту соединен с входом блока формирования выходных импульсов, дополнительно введены первый и второй управляемые интеграторы, источник напряжения, элемент задержки, второй сумматор, второй блок сравнения, ключ и преобразователи частоты в напряжение, причем выход источника напряжения подключен к первым входам первого и второго управляемых интеграторов, первому входу второго сумматора и третьему входу первого сумматора, выходы третьего и четвертого преобразователей частоты в напряжение соединены соответственно с вторым и третьим входами второго сумматора, выход которого подключен к первому входу второго блока сравнения, выход которого соединен со вторым входом первого управляемого интегратора, выход которого через элемент за держки подключен ко второму входу вто рого управляемого интегратора, выход которого соединен со вторым входом второго блока сравнения, выходы пятого и шестого преобразователей частоты в напряжение соединены соответственно с третьим и четвертым входами второго управляемого интегратора, выходы седь мого и восьмого преобразователей частоты в напряжение подключены соответственно к третьему и четвертому входам первого управляемого интегратора,выход которого соединен с первым входом первого блока сравнения, выход которого подключен к управляющему входу ключа и пятому входу первого управляемого интегратора, выход первого сумматора соединен с информационным входом ключа 5. выход которого Подключен ко второму входу первого блока сравнения. Кроме того,первый управляемый интегратор содержит три масштабирующих резистора, разделительный конденсатор, четыре ключа, два операционных усилителя, в цепь обратной связи каждого из которых включен интегрирующий конденсатор, причем первые выходы первого, второго и третьего масштабирующих резисторов являются соответственно первым, третьим и четвертым входами первого управляемого интегратора вторые выходы первого, второго и третьего масштабирующих резисторов соединены с информационным входом пер вого ключа, выход которого подключен к входу первого операционного усилителя, выход которого соединен с информационным входом второго ключа, выход которого через разделительный конденсатор подключен к входу второго операционного усилителя, выход которого является выходом первого управляемого интегратора, третий и четвертый ключи включены в обратную связь соответственно первого и второго операционного усилителя, управляющие входы первого, третьего и четвертого ключей объединены и являются вторым входом первого управляемого интегратора, управляющий вход второго ключа является пятым входом первого управляемого ключа; второй управляемый интегратор содержит три масштабирующих резистора, операционный усилитель, ключ и инвертор, причем первые выходы первого, второго и третьего масштабирующих )эезисторов являются соответственно первым, третьим и четвертым входами второго управляемого интегратора,вторые выходы первого, второго и третьеГо масштабирующих резисторов объединены и через операционный усилитель соединены с входом инвертора, выход которого является выходом второго управляемого интегратора, ключ включен в обратную связь интегратора, управляющий вход ключа является вторым входом второго управляемого интегратора. На фиг. 1 представлена схема предлагаемого устройства5 на фиг. 2 - схема первого интегратора; на фиг. 3 схема второго интегратора. Устройство содержит сумматоры 1 и 2,перый интегратор 3, второй интегратор Ц, источник 5 напряжения, блоки сравнения 6 и 7, преобразователи 8-15. частоты в напряжение, преобразователь 16 напряжения в частоту, блок формирования выходных импульсов 17, ключ. 18 и элемент задержки 19 Первый интегратор содержит масштабирующие резисторы 20,. ключи 21-2, операционные усилители 25 и 26, конденсаторы 27-29. Второй интегратор содержит масштабирующие резисторы 30, ключ 31, операционный усилитель 32, инвертор 33, интегрирующий конденсатор Устройство работает следующим об- , разом По своей функциональной сущности устройство представляет собой модель пейсмекерного нейрона, т,е, нейрона, 58 обладающего ритмоводящим механизмом эндогенного происхождения. Этот механизм является в достаточной мере универсальным и встречается в нейронах живых организмов, расположенных на различных уровнях эволюции. Деятельность пейсмекерного нейрона не ограничивается только участием в фор мировании ритмической спайковой активности клетки, но также участвует в организации пластических свойств центральной нервной системы в целом. По своим видам пейсмекерные нейро ны составляют класс ритмоводящих ней ронов, в том числе истинных пейсмеке ных нейронов, активность которых обу ловлена только эндогенным механизмом генерации пейсмекерных потенциалов, ,и пейсмекерно-синаптических нейронов в которых спайковая активность на выходе обусловлена как эндогенными механизмами генерации пейсмекерных потенциалов, так и экзогенными синап тимескими воздействиями о Предлагаемое устройство может рабо тать как в режиме истинного пейсмекер ного нейрона, так и в режиме пейсмеке но-синаптического нейрона В режиме истинно пейсмекерного нейрона, т.е, в режиме образования фоновой импульсной последовательности, устройство работает следукяцим образом, С выхода источника 5 постоянного напряжения последнее поступает на первые входы первого и второго управля емого интегратора и первые входы сум маторов 1 и 2,, С выхода первого сумматора 1 напряжение поступает через ключ 18, нормальное положение которого открытое, -на второй вход блока сравнения 6, определяя соответствующее пороговое напряжение. С выхода второго сумматора 2 напряжение посту пает на второй вход второго блока сравнения 7 с заданием соответствующего порога, В режиме образования фоновой импульсной последовательности сигналы на входы преобразователей 8-13 частоты в напряжение не поступают ия,-,; они могут поступать с неизменным соотношением частот, если фоновая последовательность в тех или иных целя модифицируется, например, при кодиро вании топографии устройства в сети, В первом интеграторе 3 при поступ лении на его первый вход напряжения с выхода источника 5 напряжение интегрируется по времени 4 t. и. - напряжение на входе интегратора;а - постоянная; и г напряжение на выходе операционного усилг-ггеля 25. В момент, когда напряжение на выходе интегратора 3 достигает порогового, на втором входе блока сравнения 6 напряжение с выхода блока сравнения размыкает ключ 23 и на выходе операционного усилителя 26 сохраняется напряжение, равное напряжению на выходе интегратора 3 в момент размыкания ключа 23. Одновременно с этим размыкается ключ 18 и напряжение с выхода сумматора 1 не поступает на вход блока сравнения 6 и не оказывает влияния все то время, пока на выходе интегратора 3 существует напряжение. Это предусмотрено для тех случаев, если напряжение на выходе сумматора 1 все время возрастает, так как в противном случае изменение соответствующего порогового напряжения приводит к искажению прямоугольной формы пейгмекерного потенциала. С момента появления напряжения на выходе интегратора 3 последнее подается на третий вход второго интегратора и размыкает ключ 31.С этого момента в интеграторе t начинается интегрирование входного напряжения по времени t . . о где и /1 - напряжеь,;е на первом входе второго интегратора; постоянная; и а напряжение на выходе второго интегратора. При достижении U 2 Ц оро1 Р ® ние с выхода блока сравнения 7 поступает на третий вход интегоатора 3, т.е, на управляющие входы ключей 21, 22 и , Ключи 22 и 2k переходят в закрытое состояние, в результате чего на входе операционного усилителя устанавливается нулевое напряжение, а ключи 22 и 2k переходят в открытое состояние, в результате чего происходит быстрая разрядка конденсаторов 27 и 29 и срыв работы второго интегратора. При установлении на выходе второго интегратооа нуля все ключи устройства переходят в начальное нормальное состояние: ключ 31 второго интегратора замыкается, что лриводит к срыву работы последнего, ключи 23 и 18 переходят в открытое состояние и на втором входе блока .6 сравнения появляется пороговое напряжение с выхода первого сумматора 1. В результате срыва работы второго интегратора напряжение на входы ключей 21, 22 и 24 перестает поступать и восстанавливается первона чальное состояние устройства Во время существования пейсмекерного потенциала, т„е напряжения на вы ходе интегратора 3, равного пороговр му напряжению на втором входе блока сравнения 6 к моменту размыкания клю чей 18 и 23, напряжение поступает на вход-преобразователя 16 напряжения ев частоту и управляет его частотой Затем импульсы с частотой, пропорцио нальной напрян ению управления, посту пают на вход блока 17 Формирователя выходных импульсов„ Так как пейсмекерный потенциал дискретный и имеет прямоугольную форму, то на выходе устройства появляются дискретные пач ки импульсов, продолжительность каждой пачки при этом равна продолжител ности пейсмекерного потенциала, а ча тота следования импульсов в пачке пропорциональна его напряжению. В мо мент прекращения генерации пейсмекер ного потенциала на выходе устройства прекращается генерация импульсов, которые вновь появляются при возникн вении нового пейсмекерного потенциала. Устройство предназначено для мод.е лирования самоорганизующихся систем и систем распознавания образов. Формула изобретения 1« Устройство для моделирования пейсмекерного нейрона, содержащее первый и второй преобразователи частоты в напряжение, выходы которых соединены соответственно с пер1вым и вторым входом первого сумматора, первый блок сравнения, выход которого через преобразователь напряжения в частоту соединен с входом блока форми рования выхбдных импульсов, отличающееся тем, что, с целью расширения функциональных возможностей за счет учета ритмоводящих механизмов центральной нервной системы. в него дополнительно введены первый и второй управляемые интеграторы, источник напряжения, элемент задержки, второй сумматор, второй блок сравнения, ключ и преобразователи частоты в напряжение, причем выход источника напряжения подключен к первым входам первого и второго управляемых интеграторов, первому входу второго сумматора и третьему входу первого сумматора, выходы третьего и четвертого преобразователей частоты в напряжение соединены соответственно с вторым и третьим входами второго сумматора, выход которого подключен к первому входу второго блока сравнения,выход которого соединен со вторым входом первого управляемого интегратора, выход которого через элемент задержки подключен ко второму входу второго управляемого интегратора, выход которого соединен со вторым входом блока сравнения, выходы пятого и шестого преобразователей частоты в напряжение соединены соответственно с третьим и четвертым входами второго управляемого интегратора, выходы седьмого и восьмого преобразователей частоты в напряжение подключены соответственно к третьему и четвертому входам первого управляемого интегратора, выход которого соединен с первым входом первого блока сравнения, выход которого подключен к управляющему входу ключа и пятому входу первого управляемого интегратора, выход первого сумматора соединен с информационным входом ключа, выход которого подключен ко второму входу первого блока сравнения. 2„ Устройство по п„1, отличающееся тем, что первый управляемый интегратор содержит три масштабирующих резистора, разделительный конденсатор, четыре ключа, два операционных усилителя, в цепь обратной связи каждого из которых включен интегрирующий конденсатор, причем первые выходы первого, второго и третьего масштабирующих резисторов являются соответственно первым, третьим и четвертым входами первого управляемого интегратора, вторые выходы первого, второго и третьего масштабирующих резисторов соединены с информационным входом первого ключа, выход которого подключен к входу перв аго операционного усилителя, выход которого соединен с информационным

входом второго ключа, выход которого через разделительный конденсатор подключен к входу второго операционного усилителя, выход которого является выходом первого управляемого интегратора, третий и четвертый ключи включены в обратную связь соответственно первого и второго операционного усилителя, управляющие входы первого, третьего и четвертого ключей объединены и являются вторым входом первого управляемого интегратора, управляющий вход второго ключа является пятым входом первого управляемого ключа.

3, Устройство по п.1, о т л и ч а ю щ е е с я тем, что второй управляемый интегратор содержит три масштабирующих резистора, операционный усилитель, ключ и инвертор, причем первые выходы первого, второго и третьего масштабирующих резисторов являются

соответственно первым, третьим и четвертым входами второго управляемого интегратора, вторые выходы пepвoгo второго и третьего масштабирующих резисторов объединен и через операционный усилитель соединены с входом инвертора, выходкоторого является выходом второго управляемого инвертора, ключ включен в обратную связь интегратора, управляющий вход ключа является вторым входом второго управляемого интегратора.

Источники информации, принятые во внимание при экспертизе

№ 6А7698, кл. G 06 G 7/60, 1979 (про.тотип).

-{I

-

фиг.

i

(риг.З

Авторы

Даты

1981-11-15—Публикация

1980-01-18—Подача