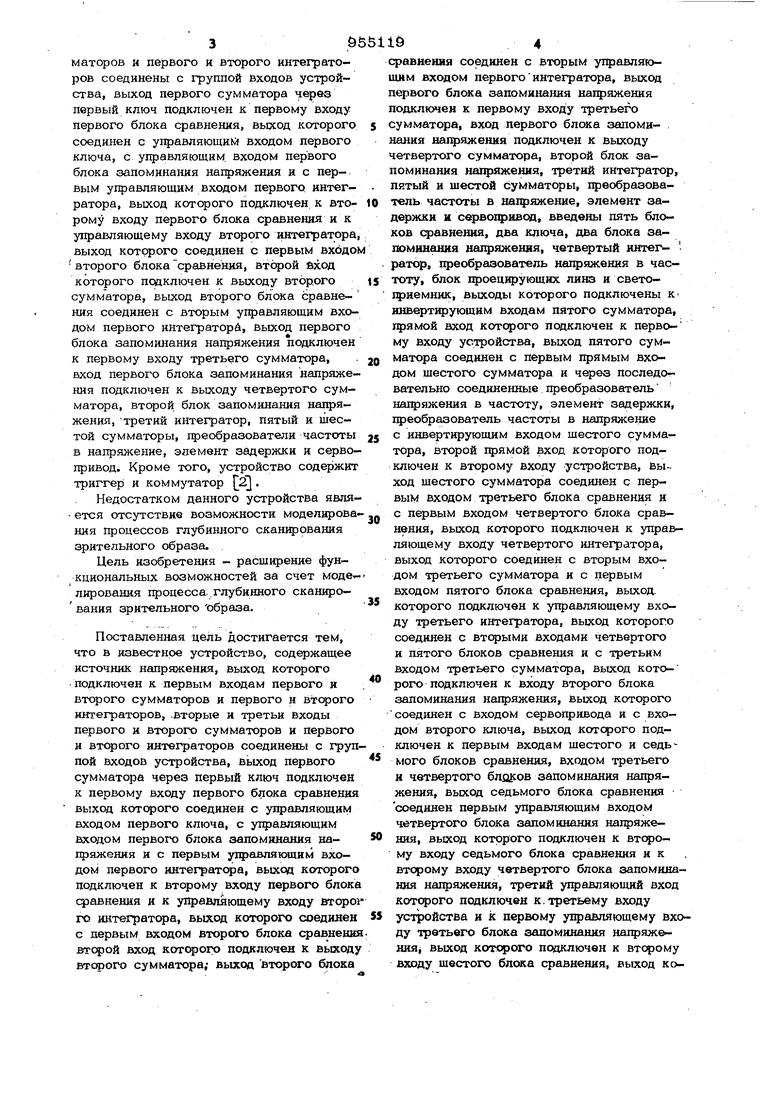

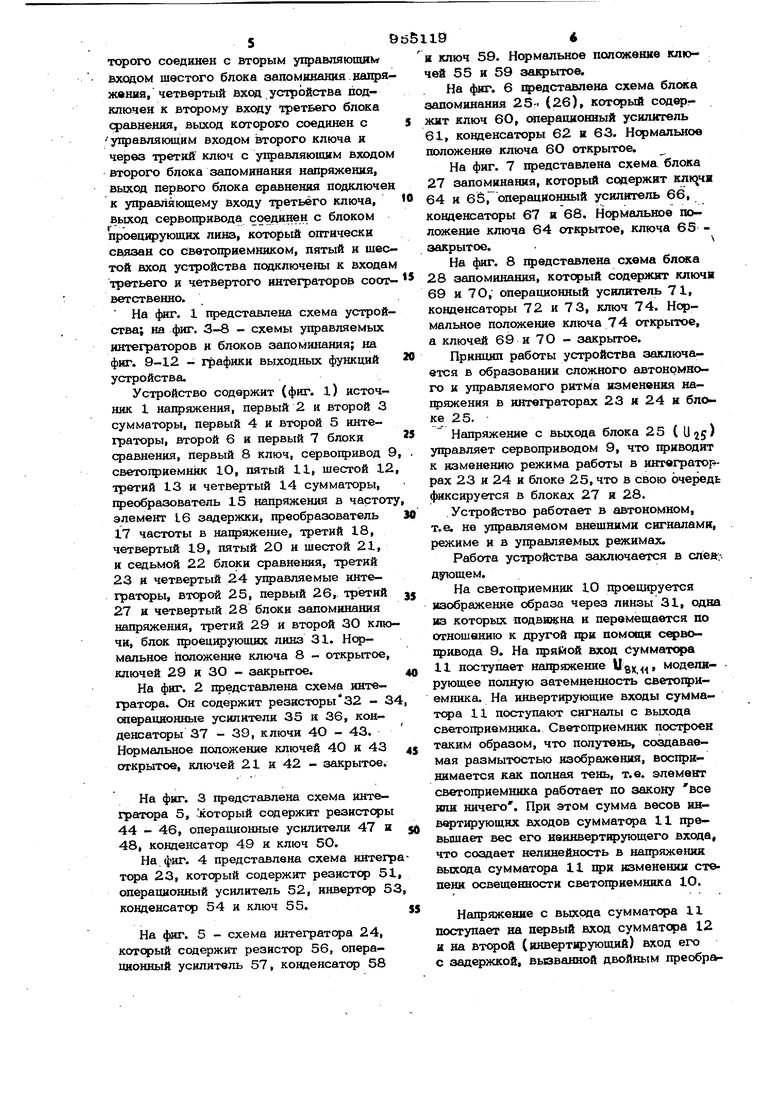

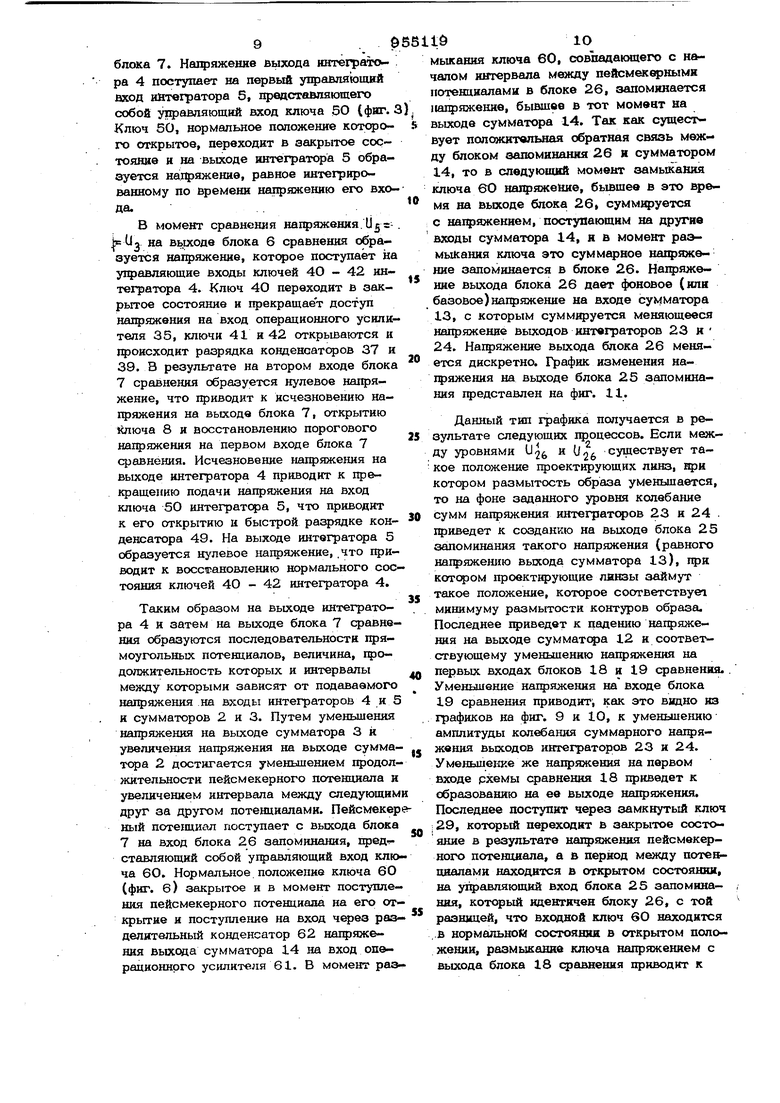

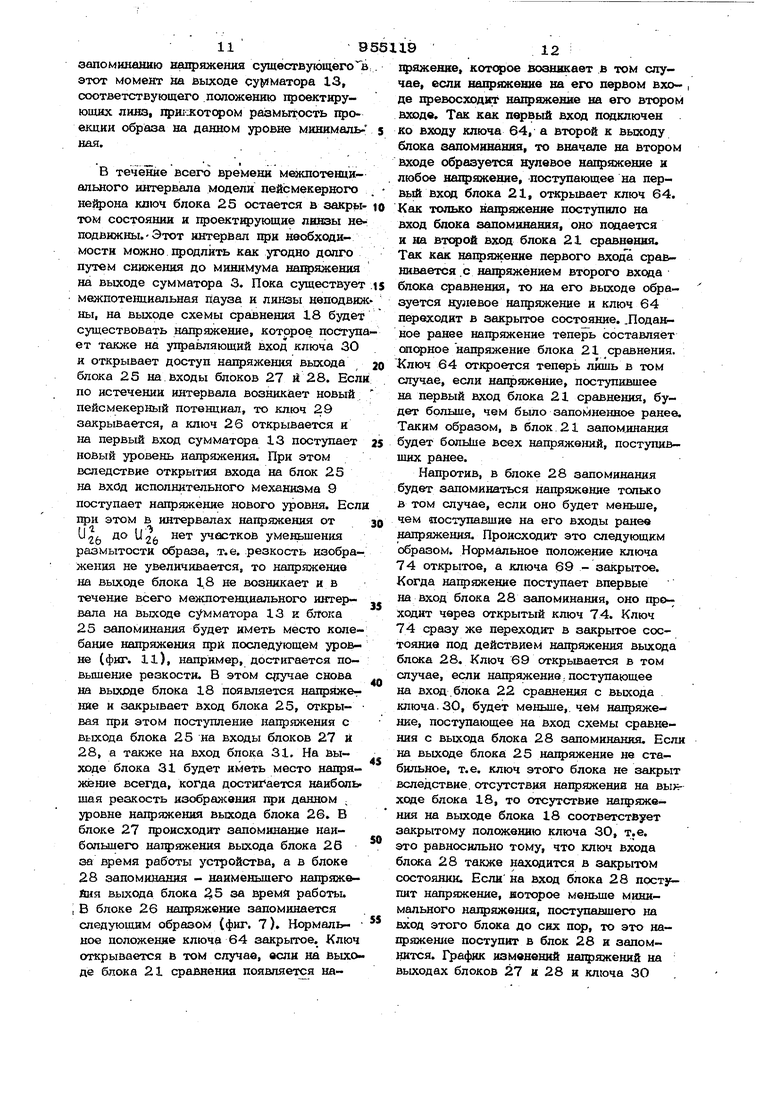

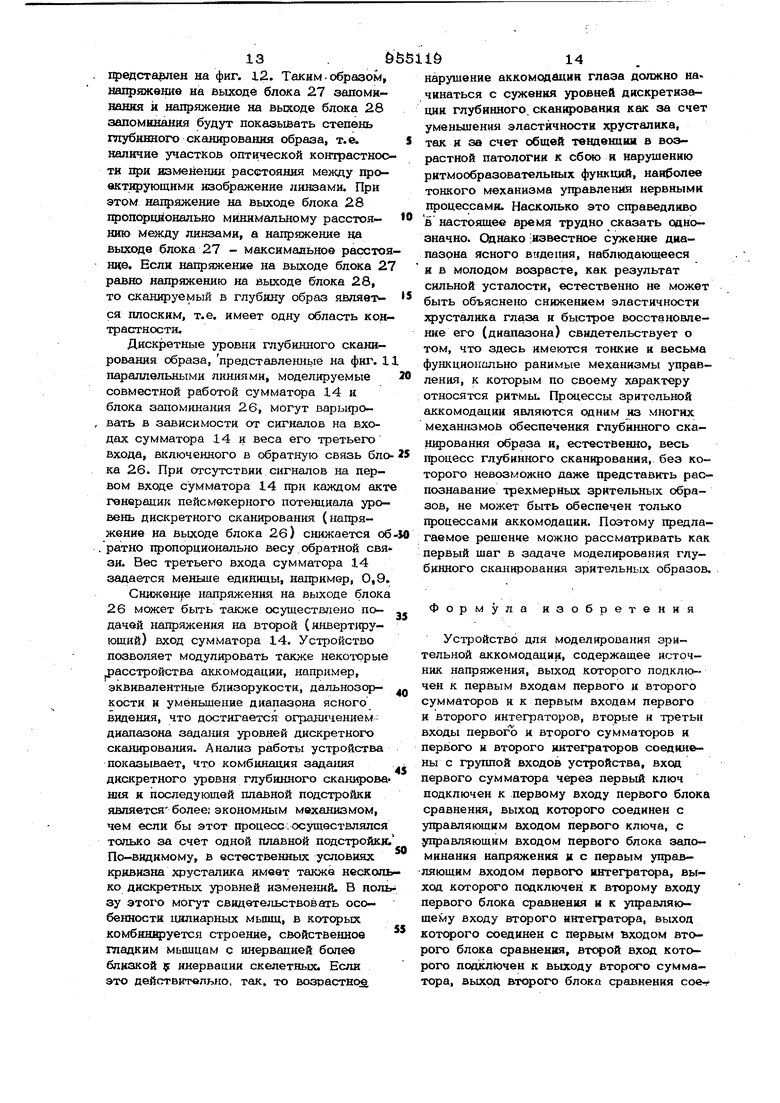

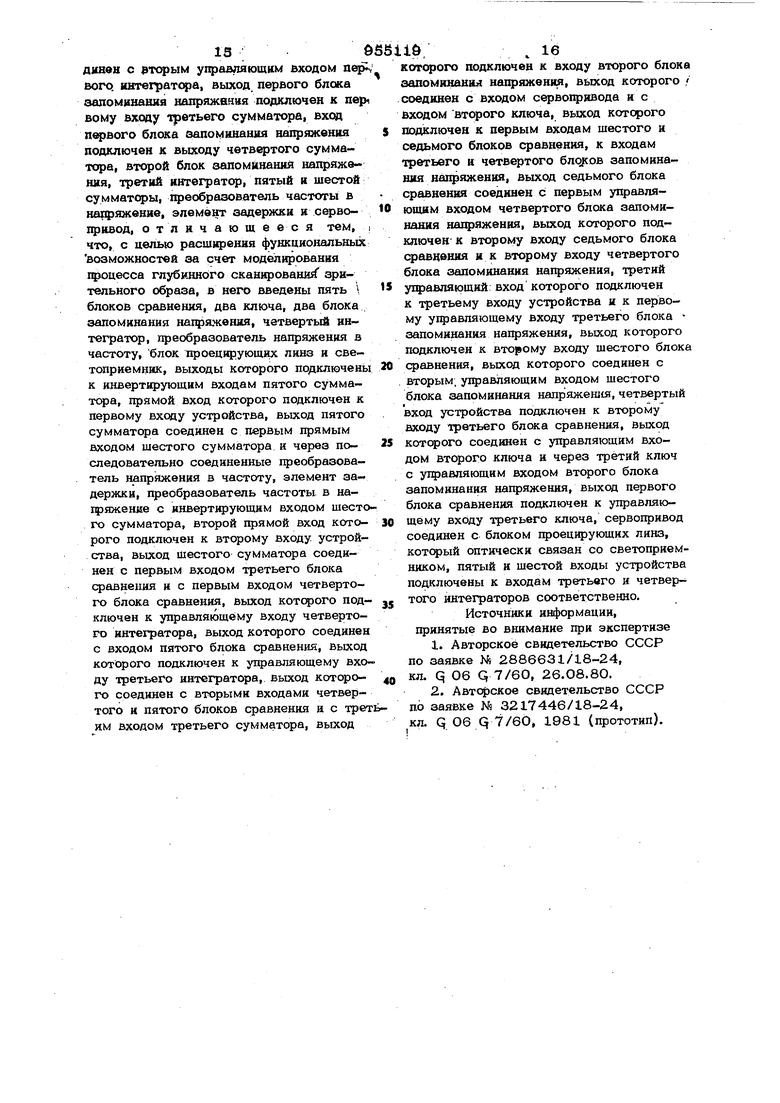

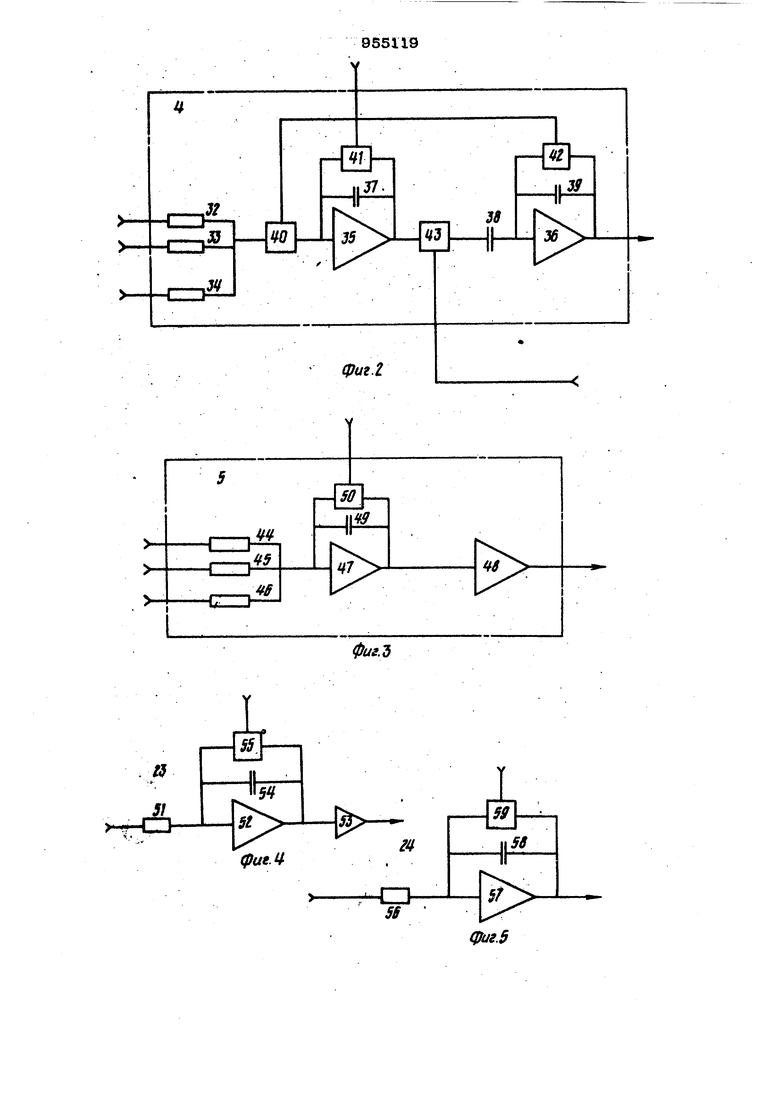

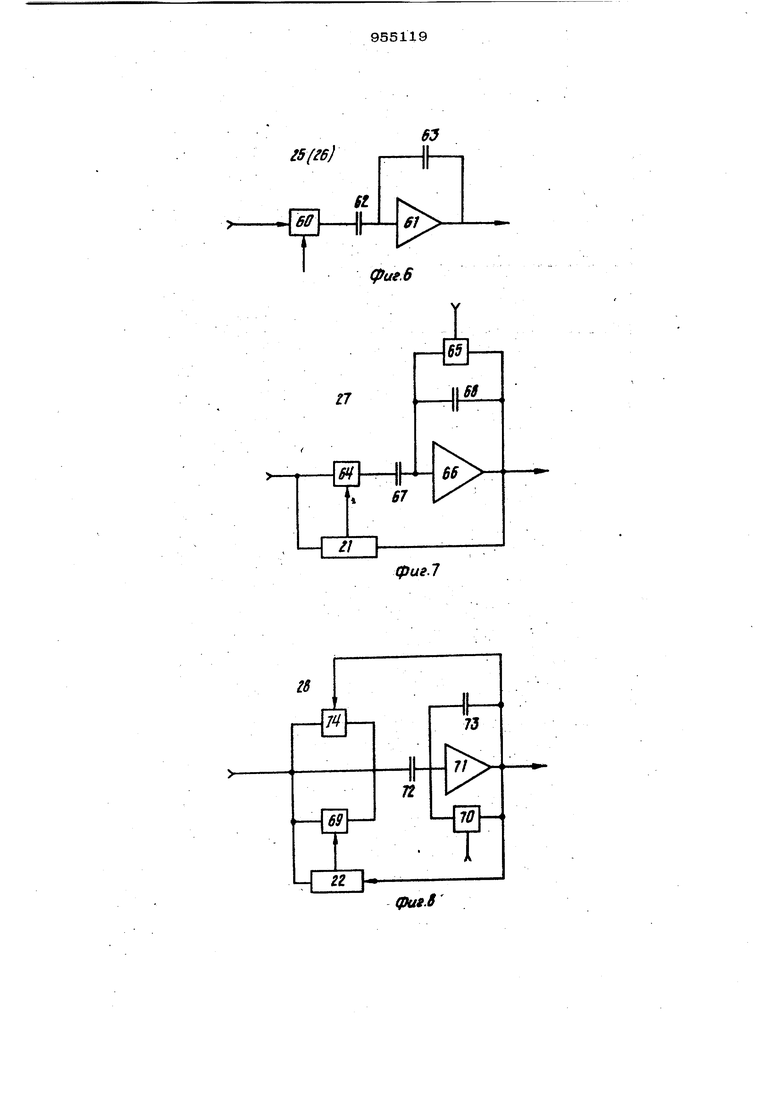

Изобретение относится к бионике и : связано с моделированием глазодинамических процессов, установкой четкости изображения. Устройство предназначено дляизучения аккомодации газа в процессе распознавания трехмерных образов и может быть использовано в системах распознавания зрительных образов в кагчестве подсистемы, дающей первичную информацию о пространственной глубине и объемности зрительного образа. Известное устройство для моделирования прослеживающих движений глаза, содержащее светоприемник, блоки моделирования центрального и периферийного no лей зрения, блок моделирования активно. стй глазодвигательного центра. В извест ном устройстве учитываются все виды глазодвигательных реакций, связанных с первичным обнаружением образа и уста новкой его проекции на область цекграль i ного поля зрения, в котором образ ска- шфуется в зависимости от оптической его информативности fll . Однако известное устройство не днфференшфует двухмерные и трехмерные образы и не дает информацию о пространственной глубине образа. Кроме того, отсутствие регуляции резкости проекции образа на светоприемник приводит к искажению оптического изображения на светоприемнике, что затрудняет дальнейшую обработку информации об образе в процессе собственного распознавания. Кроме того, как показывают последние исследования в моделировании функций нервной системы в обработке сенсорной информации, существенную роль на всех уровнях ее обработки играют ритмозадающие механизмьи Наиболее близким и предлагаемому является устройство для моделирования управления двигательными функциями, источник нагфяжешся, выход которого подключен к первым «входам первого и второго сумматоров и к первым входам первогч) и второго интеграторов, вторые и третьи входы первого и третьего сумматоров и первого и второго интеграторов соединены с группой входов устройства, выход первого сумматора через первый ключ подключен к первому входу первого блока сравненкя, выход которого соединен с управляющим входом первого ключа, с управляющим, входом первого блока запоминания нагфяжения и с первым управляющим входом первого интегратора, выход которого подключен, к второму входу первого блока сравнения и к управляющему входу второго интегратора выход которого соединен с первым входо второго блока сравнения, второй бход которого подключен к выходу второго сумматора, выход второго блока сравне- НИИ соединен с вторым управляющим входом первого интеграторе, выход первого блока запоминания напряжения подключен к первому входу третьего сумматора, вход первого блока запоминания напряжения подключен к выходу четвертого сумматора, второй, блок запоминания напряжения, третий интегратор, пятый и шестой сумматоры, преобразователи частоты в напряжение, элемент задержки и сервопривод. Кроме того, устройство содержит триггер и коммутатор 2j. Недостатком данного устройства является отсутствие возможности моделнрова нкя процессов глубинного сканирования зрительного образа. Цель изобретения - расширение функциональных возможностей за счет моде лировання процесса..глубинного сканиро- вания зрительного образа. Поставленная цель достигается тем, что в известное устройство, содержащее источник напряжения, выход которого подключен к первым входам первого и второго сумматоров и первого и Втсрого интеграторов, .вторые и третьи входы первого и второго сумматоров и первого и интеграторов соединены с груп пой входов устройства, вьосод первого сумматора через первый ключ подключен к первому входу первого блока сравнения выход которого соединен с управляющим входом первого ключа, с ухфавляющим входом первого блока запоминания нащэяжения и с первым управляющам входом первого интегратсфа, выход которого подключен к второму входу первого блока сравнения и к управляющему входу второе го интегратора, выход которого соединен с первым входом второго блока сравнения второй вход которого подключея к выходу второго сумматора; выход второго блока & 64 равнения соединен с вторым управляюим входом первогоинтегратора, выход ервого блока запоминания напряженки одключен к первому входу третьего умматора, вход первого блока запоминания напряжения подключен к выходу етвертого сумматора, второй блок запоминания напряжения, третий интегратор, пятый и шестой сумматоры, преобразователь частоты в нащзяжение, элемент задержки и сервохфивод, введены пять блоков qpaBHem, два ключа, два блока запоминания напряжения, четвертый интег ратор, преобразователь напряжения в частоту, блок проецирующих линз и светофиемник, выходы которого подключены К инвертирующим входам пятого сумматора, 1ФЯМОЙ вход которого подключен к первому входу устройства, выход пятого сумматора соединен с первым прямым входом щестого сумматора и через последовательно соединенные преобразователь напряжения в частоту, элемент задержки, преобразователь частоты в напряжение с инвертирующим входом шестого сумматора, второй 1ФЯМОЙ вход которого подключен к второму входу устройства, выход шестого сумматора соединен с первым входом третьего блока сравнения и с первым входом четвертого блока сравнения, выход которого подключен к управляющему входу четвертого интегратора, выход которого соединен с вторым входом третьего сумматора и с первым входом пятого блока сравнения, выход, которого подключен к управляющему входу третьего иетегратора, выход которого соединен с втфыми входами четвертого и пятого блоков сравнения и с третьим Входом третьего сумматора, выход которого подключен к входу BTqporo блока запоминания напряжения, выход которого соединен с входом сервопривода и с входом второго ключа, выход которого подключен к nepBbiM Входам шестого и седьмого блоков сравнения, входом третьего и четвертого бла|сов запоминания напряжения, выход седьмого блока сравнения соединен первым управляющим входом четвертого блока запоминания нащзяжения, выход которого подключен к второму входу седьмого блока сравнения и к второму входу четвертого блока запоминания напряжения, третий управляющий вход которого подключен к. третьему входу устройства и к первому управляющему входу третьего блока запоминания нагфяж&нияj выход которого подключен к второму входу шестого блока сравнения, выход которого соединен с вторым управляюпш1м входом шестого блока аапомшшния напря жения, четвертый вход устройства подключен к второму входу третьего блока сравнения, выход которого соединен с утфавляющнм входом второго ключа и через третий ключ с управляющим входо BTOpotx) блока запоминания напряжения, выход первого блока сравнения подключе к управляющему входу третьего ключа, выход сервопривода соединен с блоком проешфующих линз, который оптически связан со светоприемником, пятый и щес той вход устройства подключены к входа третьего и четвертого интеграторов соот ветствешю. На фиг. 1 представлена схема устрой ства; на фиг. 3-8 - схемы управляемых интеграторов и блоков запоминания; на фиг. 9-12 - графики выходных функций устройства. Устройство содержит (фиг. l) источник 1 напряжения, первый 2 и второй 3 сумматоры, первый 4 и второй 5 интеграторы, второй 6 и первый 7 блоки сравнения, первый 8 ключ, сервогфивод свето1фиемннк 10, пятый 11, шестой 12 третий 13 и четвертый 14 сумматоры, щзеобразователь 15 напряжения в частот элемеиг L6 задержки, преобразователь 17 частоты в напряжение, третий 18, четвертый 19, пятый 20 и шестой 21, и седьмой 22 блоки сравнения, третий 23 и четвертый 24 управляемые интеграторы, второй 25, первый 26, третий 27 и четвертый 28 блоки запоминания напряжения, третий 29 и второй ЗО клю чи, блок 1фоецирую1цих линз 31. iiapмальное положение ключа 8 - открытое, ключей 29 и ЗО - закрытое. На фиг. 2 представлена схема интегратора. Он содержит резисторы32 - 3 сэтерационные усилители 35 и 36, конденсаторы 37 - 39, ключи 4О - 43. Нормальное положение ключей 40 и 43 открытое, ключей 21 и 42 - закрытое. На фиг. 3 представлена схема интегратора 5, хоторый содержит резисторы 44 - 46, операционные усилители 47 и 48, конденсатор 49 и ключ 50. На фиг. 4 представлена схема интегр тора 23, который содержит резистор 51 операционный усилитель 52, инвepтqp 5 конденсатор 54 и ключ 55. На фиг. 5 - схема интегратора 24, который содержит резистор 56, операционный усилитель 57, конденсатор 58 19А я. ключ 59. Нормальное положение ключей 55 и 59 закрытое. На фиг. 6 Ефедставлена схема блока запоминания 25- (26), который содержит ключ 60, оп ационный усилитель 61, конденсаторы 62 и 63. Нормальное положение ключа 6О открытое. На фиг. 7 представлена схема блока 27запоминания, который содержит 64 и 65, операционный усилитель 66, конденсаторы 67 и 68. Нормальное положение ключа 64 открытое, ключа 65 закрытое. На фиг. 8 представлена схема блока 28запоминания, который содержит ключи 69 и 70, операционный усилитель 71, конденсаторы 72 и 73, ключ 74. Нормальное положение ключа 74 открытое, а ключей 69 и 70 - закрытое. Принцип работы устройства заключается в образовании сложного автономного и управляемого ритма изменения нафяжения в интеграторах 23 и 24 и блоке 25, Напряжение с выхода блока 25 ( UjJ управляет сервоприводом 9, что гфиводит к изменению режима работы в шггвгратор рах 23 и 24 и блоке 25, что в свою очередь фиксируется в блоках 27 и 28. Устройство работает в автономном, т.е. не управляемом внешними сигналами, режиме и в управляемых режимах. Работа устройства заключается в слеа.-. дующем. На светотфиемник 10 проецируется изображение образа через линзы 31, одна из которых подвижна и перемещается по отношению к другой 1ФИ помощи с вопривода 9. На цряйой вход Сумматора 11 поступает нащ)яжение Ugx ii моделирующее полную затемненность светог риемника. На инвертирующие входы сумматора 11 поступают сигналы с выхода светоприемника. Светоприемник построен таким образом, что полутень, создаваемая размытостью изображения, воспринимается как полная тень, т.е. элемент светоприемника работает по закону все или ничего . При этом сумма весов инвертирующих входов сумматора 11 превышает вес его нвинверт1фующего входа, что создает нелинейность в напряжении выхода сумматора 11 иря изменении степени освещенности светоприемника 1О. Напряжение с выхода сумматора 11 поступает на первый вход сумматора 12 и на второй (инверт1фующий) вход его с задержкой, вызванной двойным преобразованнем в греобразователе 15 и блоке сравнения 18, и задержкой импульсов в элементе задержки 17. В сумматоре 12 гфонсходит алгебраическое сложение

JBxii U,,(t+At)-U,,lt).

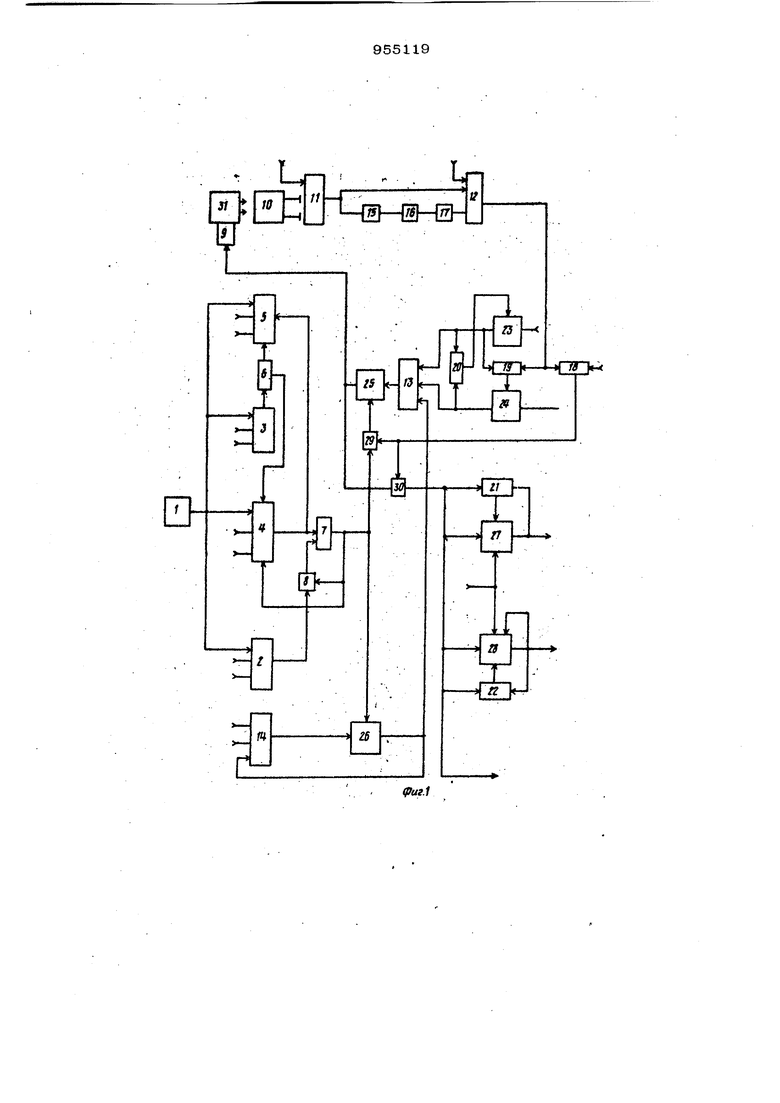

Уменьшение напряжения на выходе сумматора 11 будет соответствовать меньшему затемнению светоприемника, что, учитывая его особенность работы по типу релейной связи его светочувствительных элементов, соответствует уменьшению степени размытости изображения. НапряГ жение выхода сумматора. 12 определяет опорное напряжение на входе блока 1Э сравнения и тот максимальный уровень , напряжения, которое может быть создано на выходе интегратора 23. «

На вход интегратора 23 поступает напряжение, которое интегрируется в интеграторе 23 по времени.

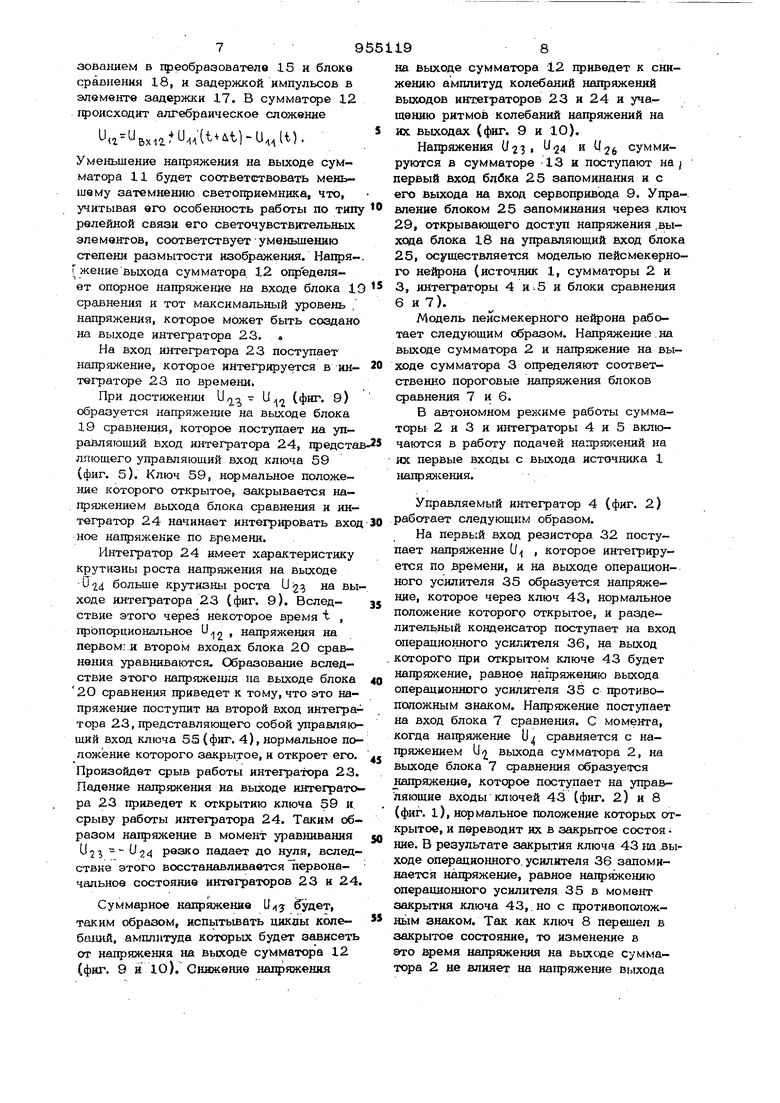

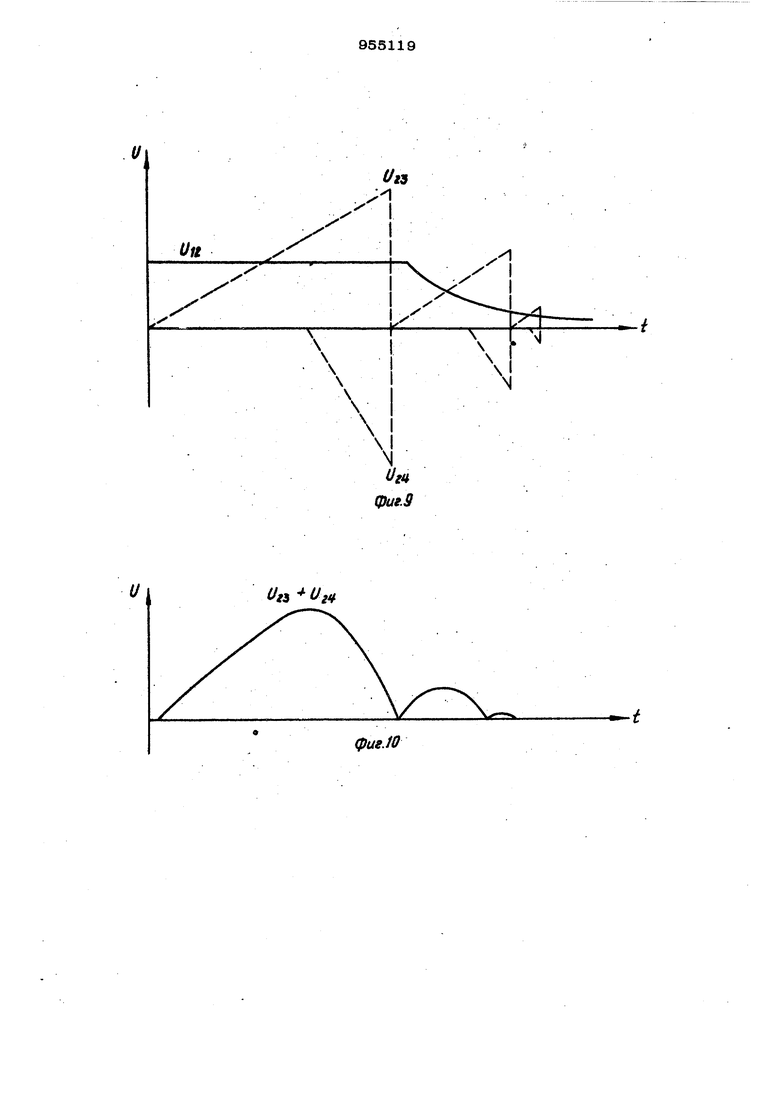

При достижении U {фиг. 9 образуется напряжение на выходе блока 19 сравнения, которое поступает на управляющий вход интегратора 24, представ ляющего управляющий вход ключа 59 (фиг. 5). Ключ 59, нормальное положение которого открытое, закрывается на- хряжением выхода блока сравнения и интегратор 24 начинает интегрировать вход кое напряженке по времени.

Интегратор 24 имеет характеристику крутизны роста напряжения на выходе больше крутизны роста 112: на выходе интегратора 23 (фиг. 9). Вследствие этого через некоторое время t , пропорциональное 12 напряжения на первом: и втором входах блока 20 сравнения уравниваются. Образование вследствие этого напряжения на выходе блока 2О сравнения приведет к тому, что это напряжение поступит на второй вход интегратора 23, представляющего собой управляющий вход ключа 5S (фиг. 4), нормальное положение которого закрытое, и откроет его. Произойдет срыв работы интегратора 23. Падение напряжения на выходе интегратора 23 приведет к открытию ключа 59 и срыву работы интегратора 24. Таким образом напряжение в момент уравнивания и .4 pesKo падает до нуля, вследствие этого восстанавливается первоначальное состояние интеграторов 23 и 24

Суммарное напряжение будет, таким образом, испытывать цккаы колебшшй, амплитуда которьис будет зависеть от напряжения на выходе сумматора 12 (фиг. 9 нЮ). Снижение нахфяжсния

на выходе сумматора 12 приведет к снижению амплитуд колебаний напряжений выходов интеграторов 23 я 24 я учащению ритмов колебаний напряжений на юс выходах (фиг. 9 и 10).

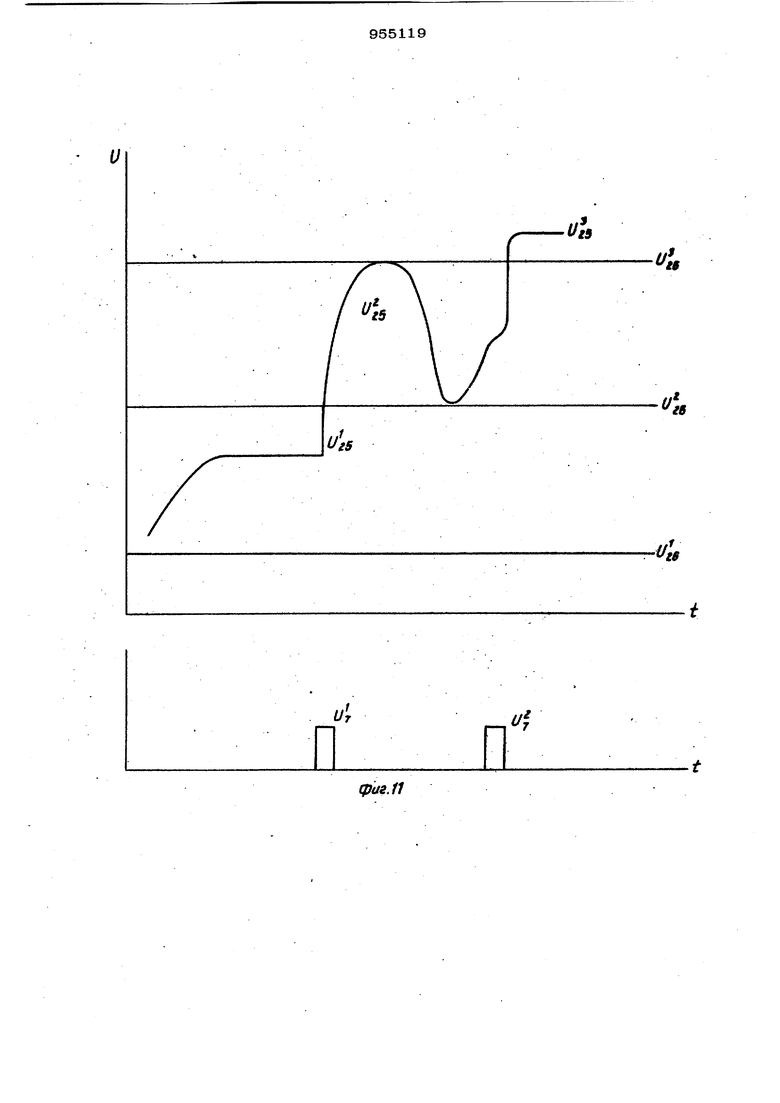

Нащзяжения (/231 и Uj суммируются в сумматоре 13 и поступают на первый вход бдбка 2 5 запоминания и с его выхода на вход сервопривода 9. Управление блоком 25 запоминания через клю 29, открывающего доступ напряжения ,выхсща блока 18 на управляющий вход блок 25, осуществляется моделью пейсмекерного нейрона (источник I, сумматоры 2 и 3, интеграторы 4 и-5 и блоки сравнения 6 и 7).

Модель пейсмекерного нейрона работает следующим образом. Напряжение . на выходе сумматора 2 и напряжение на выходе сумматора 3 определяют соответственно пороговые напряжения блоков сравнения 7 и 6.

В автономном режиме работы сумматоры 2 и 3 и интеграторы 4 и 5 включаются в работу подачей напрялсений на их первые входы, с выхода источника 1 напряясения.

Управляемый интегратор 4 (фиг. 2) работает следующим образом.

На первый вход резистора 32 поступает напряжение (J , которое интегрируется по .времени, и на выходе операционного усилителя 35 образуется напряжение, которое через ключ 43, нормальное положение которого открытое, и разделительный конденсатор поступает на вход операционного усилителя 36, на выход . которого при открытом ключе 43 будет напряжение, равное нагфяжению выхода операционного усилителя 35 с противоположным знаком. Напряжение поступает йа вход блока 7 сравнения. С момента, когда напряжение U сравняется с нащзяжением U выхода сумматора 2, на выходе блока 7 сравнения образуется напряжение, которое поступает на управляющие входы ключей 43 (фиг. 2) и 8 (фиг. 1), нормальное положение которых открытое, и переводит их в закрытое состоя ние. В результате закрытия ключа 43 на .выходе операцио1шого. усилителя 36 запоминаетс а напряжеияе, равное нагфжкению операционного усилителя 35 в момент закрытия ключа 43,. но с противопопожньш знаком. Так как ключ 8 перешел в закрытое состояние, то изменение в это время напряжения на выходе сумматора 2 не влияет на напряжение выхода блока 7. Нащзяженне выхода шггегратора 4 поступает на первый управляющий вход интегратора 5, представляющего собой управляющий вход ключа 50 (фиг. 3 Ключ 50, нормальное положение которого открытое, переходит в закрытое состояние и на выходе интегратора 5 образуется на15 яжение, равное интегрированному по времени напряжению его входа.. В момент сравнения нагфяжения. Удгi« 2 на вьисоде блока 6 сравнения образуется напряжение, которое поступает на управляющие входы ключей 40 - 42 интегратора 4. Ключ 40 переходит в закрытое состояние и прекращает доступ напряжения на вход операционного усилителя 35, ключи 41 и 42 открываются и щзоисходит раарядка конденсаторов 37 и 39. В результате на втором входе блока 7 сравнения образуется нулевое напряжение, что приводит к исчезновению нагфяжения на выходе блока 7, открытию йлюча 8 и восстановлению порогового напряжения на первом входе блока 7 сравнения. Исчезновение напряжения на выходе интегратора 4 приводит к прекращению подачи напряжения на вход ключа 50 интегратора 5, что приводит к его открытию и быстрой разрядке конденсатора 49. На выходе интегратора 5 образуется нулевое напряжение, .что приводит к восстановлению нормального состояния ключей 40 - 42 интегратора 4. Таким образом на выходе интегратора 4 и затем на выходе блока 7 сравнения образуются последовательности 1фямоугольных потенциалов, величина, щэодолжительность которых и интервалы между которыми зависят от подаваемого наг зяжения на входы интеграторов 4 и 5 и сумматоров 2 и 3. Путем уменьшения напряжения на выходе сумматора 3 и увеличения напряжения на выходе сумматора 2 достигается уменьщением продолжительности пейсмекерного потенциала и увеличением интервала между следующим друг за другом потенциалами. Пейсмекер ный поте1щиал поступает с выхода блока 7 на вход блока 26 запоминания, пред- ставляющий собой ущзавляющий вход 60. Нормальное положение ключа 60 (фиг. б) закрытое и в момент поступления пейсмекерного потенциала на его открытие и поступление на вход через разделительный конденсатор 62 нагфяжения выхода сумматора 14 на вход операционного усилителя 61. В момент раз- мьжашш ключа 60, совпадающего с началом интервала между пейсмек нымн потенциалами в блоке 26, запоминается напряжение, бывшее в тот момент на выходе сумматора 14. Так как существует положнтвлышя обратная связь между блоком запоминания 26 и сумматором 14, то в следующий момент замыкания ключа 6О натфяжеШсе, бывщее в это время на выходе блока 26, сумм1фуется с на14)яжением, поступающим на другие входы сумматора 14, и в момент размыкания ключа это суммарное напряжение запоминается в блоке 26. Напряжение выхода блока 26 дает фоновое (или базовое)нащ)яжение на входе сумматора 13, с которым суммируется меняющееся напряжение выходов интеграторов 23 и 24. Нащзяжение выхода блока 26 меняется дискретна График изменения на1ряжения на выходе блока 25 запоминания хфедставлен на фиг. 11. Данный тип графика получается в результате следующих процессов. Если между уровнями о2 6 существует такое положение проектирующих линз, ври котором размытость образа уменьщается, то на фоне заданного уровня колебание сумм напряжения интеграторов 23 и 24 . Щ)иведет к созданию на выходе блока 25 запоминания такого напряжения (равного напряжению выхода сумматора 13), при KOTqpoM проект1фующие линзы займут такое положение, которое соогветствуе минимуму размытости контуров образа. Последнее гфиведет к падению напряжения на выходе сумматора 12 и соответствующему уменьшению напряжения на первых входах блоков 18 и 19 сравнения. . Уменьшение нахфяжения на входе блока 19 сравнения приводит, как это ввдно на графиков на фиг. 9 и 10, к уменьшению амплитуды колебания суммарного нахфяжения выходов интеграторов 23 и 24. Уменьшение же напряжения на первом входе рхемы сравнения 18 приведет к образованию на ее выходе напряжени51. Последнее поступит через замкнутый ключ 29, который переходит в закрытое состояние в результате на яження пейсмекерного потенциала, а в период между потевцналами находится в открытом состоянии, на управляющий вход блока 25 запоминания, который идеш-кчен блоку 26, с той разницей, что входной ключ 60 находится в нормальной состоянии в открытом положении, размыкание ключа напряжением с выхода блока 18 сравнения приводит к 11В запоминанию напряжения сущвстгвующего Ь этот момент на выходе суЬйматора 13, соответствующего положению проектирующих линз, i HJJKOTOpoM размытость проекции образа на данном уровне минимальная. В течение всего времени межпотенцкального интервала модели пейсмекерного нейрона ключ блока 25 остается в закры том состоянии и проект1фую1цие лннзы не подвижны. Этот интервал 1фи необходимости можно продлить как угодно долго путем снижения до минимума на1д яжешш на выходе сумматора 3. Пока существует межпотенциальная пдуза и линзы неподвиж ны, на выходе схемы сравнения 18 будет существовать напряжение, которое поступ ет также на управляющий вход ключа 30 и открывает доступ напряжения выхода , блока 25 на входы блоков 27 и 28. Есл по истечении интервала возникает новый, пейсмекерный потенциал, то ключ 29 закрывается, а ключ 2 6 открывается и на первый вход сумматора 13 поступает новый уровень напряжения. При этом вследствие открытия входа на блок 25 на вход исполнительного механизма 9 поступает напряжение нового уровня. Есл при этом в интервалах напряжения от и 5 Д° участков уменьщения размытости образа, т.е. резкость изображения не увеличивается, то напряжение на выходе блока 18 не возникает ив течение всего межпотенциального интервала на Выходе сумматора 13 и бяока 25 запоминания будет иметь место колебание напряжения при последующем уровне (фиг. И), например, достигается повьпиение резкости. В этом снова на выходе блока 18 появляется нагфяже ние и закрывает вход блока 25, открывая при этом поступление напряжения с выхода блока 25 на входы блоков 27 и 28, а также на вход блока 31. На выходе блока 31 будет иметь место напряжение всегда, когда достигается наиболь щая резкость изобраясвния при данном ; уровне напряжения выхода блока 26. В блоке 27 гфоисходит запоминание наибольшего нащ)яжения выхода блока 25 за время работы устройства, а в блоке 28 запоминания - наименьшего напряквйия выхода блока 2i5 за время работы. ; В блоке 26 напряжение запоминается следующим образом (фиг. 7). Нормальное положение ключа 64 закрытое. Ключ открывается в том случав, если на выхо де блока 21 сравнения появляется на1ЭЩ)яженке, которое возникает в том случае, если напряжение на его первом вхо- , де превосходит напряжение на его втором входе. Так как первый вход подключен ко входу ключа 64, а второй к выходу блока гапоминанин, то вначале на втором входе образуется нулевое нахфяжение и любое напряжение, поступающее на первьй вход блока 21, открывает ключ 64. Как только на1фяжение поступило на вход бпока запоминания, оно подается и на втсфой вход блока 21 сравнения. Так как нащзяжение первого входа сравнивается .с напряжением второго входа блока сравнения, то на его выходе образуется нулевое нащзяжение и ключ 64 переходит в закрытое состояние. .Поданное ранее напряжение теперь составляет опорное напряжение блока 21 сравнения. Ключ 64 откроется теперь лишь в том случае, если напряжение, поступившее на первый вход блока 21 сравнения, будет больше, чем было запомненное ранее. Таким образом, в блок 21 запом.инания будет болУде всех напряжений, поступивших ранее. Напротив, в блоке 28 запоминания будет запоминаться напряжение только в том случае, если оно будет меньше, чем яоступавшие на его входы ранее напряжения. Происходит это следующим образом. Нормальное положение ключа 74 открытое, а ключа 69 - закрытое. Когда напряжение поступает впервые на вход блока 28 запоминания, оно про-; ходит через открытый ключ 74. Ключ 74 сразу же переходит в зеисрытое состояние под действием напряжения выхода блока 28. Ключ 69 открывается в том случае, если напряжение.. поступающее на вход блока 22 сравнения с выхода ключа. 30, будет меньше,, чем напряжение, поступающее на вход схемы сравнения с выхода блока 28 запоминания. Если на выходе блока 25 напряжение не стабильное, т.е. ключ этого блока не закрыт вследствие, отсутствия напряжений на вы гходе блока 18, то отсутствие напряжения на выходе блока 18 соответствует закрытому положению ключа 30, т.е. это равносильно тому, что ключ входа блока 28 также находится в закрытом состоянии. Если на вход блока 28 поступит напряжение, которое меньше минимального напряжения, поступавшего на вход этого блока до сих пор, то это напряжение поступит в блок 28 и запомнится. График изменений на1фяжений на выходах блоков 27 и 28 и ключа 30 представлен на фиг. 12. Таким. образом, напряжение на выходе блока 27 запоминания и напряжение на выходе блока 28 запоминания будут показьшать степень глубинного сканирования образа, т.е. наличие участков оптической контрастнос ти при изменении рассл-ояния между проектирующими изображение линзами. При этом нагфяжение на выходе блока 28 пропорционально минимальному расстоя- нию между линзами, а напряжение на выходе блока 27 - максимальное рассто ние. Если напряжение на выходе блока 2 равно напряжению на вьрсоде блока 28, то сканируемый в глубину образ является плоским, т.е. имеет одну область кон трастности. Дискретные уровни глубинного сканирования образа, представленные на фиг. 1 параллельными линиями, моделируемые совместной работой сумматора 14 и блока запоминания 26, могут варыфовать в зависимости от сигналов на в,ходах сумматора 14 и веса его третьего входа, включенного в обратную связь бл ка 26. При отсутствии сигналов на первом входе сумматора 14 при каждом акт генерации пейсмекерного потенциала уровень дискретного сканирования (напряжение на выходе блока 26} снижается о . ратно пропорционально весу.обратной свя зи. Вес третьего входа сумматора 14 задается меньше единицы, например, 0,9 Снижеш|;е напряжения на выходе блок 26 может быть также осуществлено подачей напряжения на второй (инверт1фующий) вход сумматора 14. Устройство позволяет модулировать также некоччэрые )асстройства аккомодации, например, эквивалентные близорукости, дальнозоркости и уменьшение диапазона ясного видения, что достигается огра шчениемдиапазона задания уровней дискретного скшшрования. Анализ работы устройства показывает, что комбинация задания дискретного уровня глубинного сканирова ния и последующей плавной подстройки является более; экономным механизмом, чем если бы этот процесс .осуществлялся только за счет одной плавной подстройки По-видимому, в естественных условиях кривизна хрусталика имеет также нескол ко дискретных уровней измене1шй. В пол ЗУ этого могут свидетельствовать особенности шшиарныч мышц, в которых комбинируется строение, свойственное гладким мьоицам с инервапией более близкой If инервации скелетных. Если это действительно, так, то возрастное нарушение аккомодации глаза должно на. чинаться с сужения уровней дискретизации глубинного, скан1фовакия как за счет уменьшения эластичности хрусталика, так и за счет общей тенденции а возрастной патологии к сбою и нарушению ритмообразовательных функций, наиболее тонкого механизма управления нервными процессами. Насколько это справедливо в настоящее время трудно сказать однозначно. Однако-известное сужение диапазона ясного втшепия, наблюдающееся и в молодом возрасте, как результат сильной усталости, естественно не может быть объяснено снижением эластичности хрусталика глаза и быстрое восстановление его (диапазона) свидетельствует о том, что здесь имеются тонкие и весьма функционально ранимые механизмы управления, к которым по своему характеру относятся ритмы. Процессы зрительной аккомодации являются одним из многих механизмов обеспечения глубинного сканирования образа и, естественно, весь щэоцесс глубинного сканирования, без которого невозможно даже представить распознавание трехмерных зрительных образов, не может быть обеспечен только щ)оцессами аккомодации. Поэтому 1федлагаемое решение можно рассматривать как первый шаг в задаче моделирования глубинного сканирования зрительных образов. Формула изобретения Устройство для моделирования зрительной аккомодации, содержащее источник напряжения, выход которого подключен к первым входам первого и второго сумматоров и к первым входам первого и второго интеграторов, вторые и третьи входы первозто и второго сумматоров и первого и второго интеграторов соединены с группой входов устройства, вход первого сумматора через первый ключ подключен к первому входу первого блока сравнения, выход которого соединен с управляЕсидим входом первого ключа, с управляющим входом первого блока запоминания напряжения к с первым управляющим входом первого юггегратора, выход которого подключен к второму входу первого блока сравнения и к утфавляющему входу второго интегратора, выход котсфого соединен с первым входом второго блока сравнения, второй вход которого подключен к выходу вторснг-о сумматора, выход второго блока сравнения сое- динон с эторым управляющим входом nep вого. интегратора, выход первого блока запоминания напряжения подключен к пер вому входу третьего сумматора, вход левого блока запоминания напряжения подключен к выходу четвертого сумматора, второй блок запоминаний напряжения, третий интегратор, пятый и шестой сумматоры, преобразователь частоты в напряжение, элемент задержки и сервопривод, отличающееся тем, что, с целиью расширения функциональных возможностей за счет модел|фования щюцесса глубинного сканирований зрительного образа, в него введены пять блоков сравнения, два ключа, два блока запоминания напряжения, четвертый ннтегратор, преобразователь напряжения в частоту, блок ироещфующих линз и светоприемник, выходы которого подключены к инвертирующим входам пятого сумматора, прямой вход которого подключен к первому входу устройства, выход пятого сумматора соединен с первым прямым входом шестого сумматора и через последовательно соединенные преобразователь напряжения в частоту, элемент задержки, преобразователь частоты в нагцэяжение с инвертирующим входом шесто го сумматора, второй прямой вход которого подключен к второму входу устройства, выход Шестого сумматора соединен с первым входом третьего блока сравнения и с первым входом четвертого блока сравнения, выход которого подключен к управляющему входу четвертого интегратора, выход которого соединен с входом пятого блока сравнения, выход которого подключен к управляющему входу третьего интегратора, выход которого соединен с вторыми входами четвертого и пятого блоков сравнения и с трет им входом третьего сумматора, выход кспророго подключен к входу второго блока запоминания напряжения, выход которого / соединен с входом сервопривода и с входом второго ключа, выход которого подключен к первым входам шестого и седьмого блоков сравнения, к входам третьего и четвертого блоков запоминания напр51жения, выход седьмого блока сравнения соединен с первым управляющим входом четвертого блока запоминания напряжения, выход которого подключен к второму входу седьмого блока сравнения и к второму входу четвертого блока запоминания напряжения, третий управляющий; вход которого подключен к третьему входу устройства и к первому управляющему входу третьего блока запоминания напряжения, выход которого подключен к второму входу шестого блока сравнения, выход которого соединен с вторым; управляющим входом шестого блока запоминания напряжешш, четвертый вход устройства подключен к второму входу третьего блока сравнения, выход KOTqporo соединен с управляющим входом второго ключа и через третий ключ с управляющим входом второго блока запоминания напряжения, выход первого блока сравнения подключен к управляющему входу третьего ключа, сервопривод соединен с блоком проецирующих линз, котфый оптически связан со светоприемником, пятый и шестой входы устройства подключены к входам третьего и четвертого интеграторов соответственно. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке № 2886631/18-24, кл. q 06 q 7/60, 26.08.80. 2,Автчрское свидетельство СССР по заявке № 3217446/18-24, кл. q Об q Т/бО, 1981 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования пейсмекерного нейрона | 1981 |

|

SU982028A2 |

| Устройство для моделирования пейсмекерного нейрона | 1980 |

|

SU881783A1 |

| Устройство для моделирования прослеживающих движений глаза | 1980 |

|

SU877577A1 |

| Устройство для моделирования нейронных ансамблей | 1982 |

|

SU1064285A1 |

| Устройство для моделирования условно-рефлекторных связей | 1980 |

|

SU957236A1 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| Время-импульсное множительное устройство | 1982 |

|

SU1048489A1 |

| РЕГУЛЯТОР | 1990 |

|

RU2015520C1 |

| Устройство для моделирования электрокардиограммы | 1980 |

|

SU942065A1 |

| Датчик случайных чисел | 1982 |

|

SU1083189A2 |

50

5

S

48

15(16)

60

6J

61

фиеб

tl

69

66

67

фиг.7

тг

гг f

70

т

фи9.8

и

/3 tJlf

u. ,-

u(

П

фаг. 11 i

Ute. Оз1

Hie.Un

Un

изо

gjui.n

UM

Usa

Un

Авторы

Даты

1982-08-30—Публикация

1980-11-26—Подача