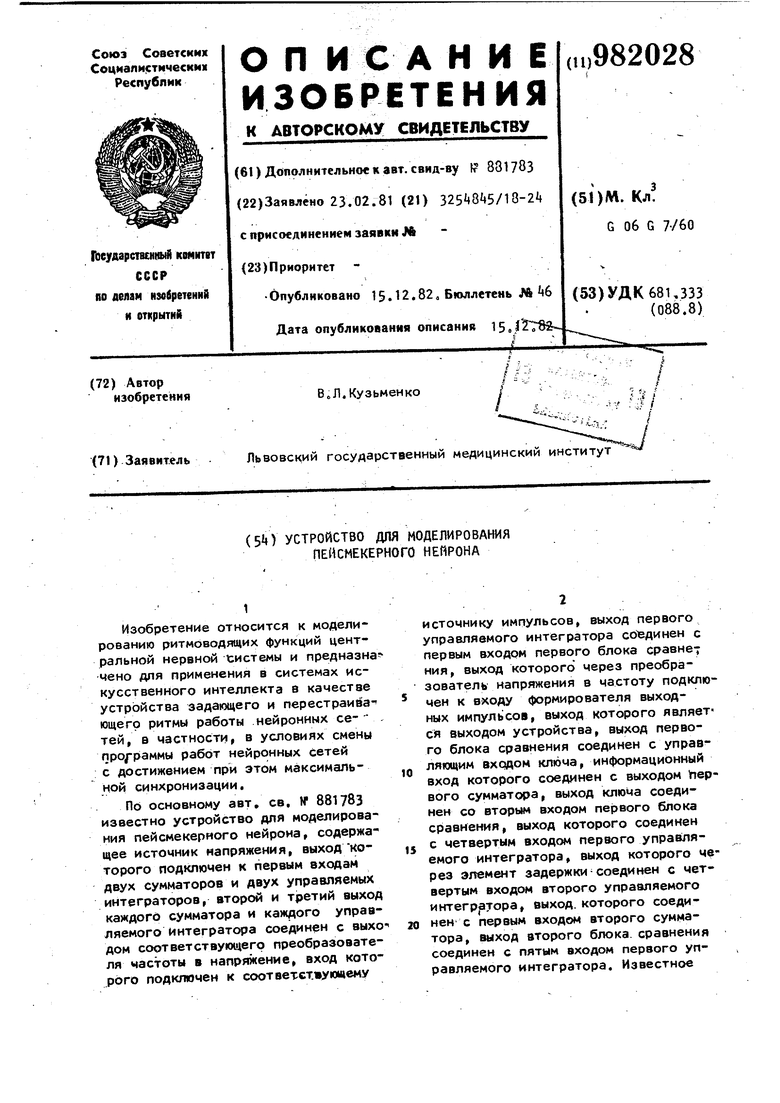

(Б) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ЛЕЙСМЕКЕРНОГО НЕЙРОНА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования пейсмекерного нейрона | 1980 |

|

SU881783A1 |

| Устройство для моделирования нейронных ансамблей | 1982 |

|

SU1064285A1 |

| Устройство для моделирования зрительной аккомодации | 1980 |

|

SU955119A1 |

| Устройство для моделирования условно-рефлекторных связей | 1980 |

|

SU957236A1 |

| Устройство для моделированияНЕйРОНА | 1979 |

|

SU853632A1 |

| Устройство для моделирования ритмов гормональной регуляции | 1980 |

|

SU934508A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ ПОМЕХ | 1988 |

|

SU1841099A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ВЕЩЕСТВ С ПОМОЩЬЮ УЛЬТРАЗВУКОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2169906C2 |

| Устройство для моделирования нейрона | 1974 |

|

SU512479A1 |

1

Изобретение относится к моделированию ритмоводящих функций центральной нервной 1систены и предназна чено для применения в системах искусственного интеллекта в качестве устройства задающего и перестраийающего ритмы работы нейронных се- тей, в частности, в условиях смены npoj-раммы работ нейронных сетей с достижением при этом максимальной синхронизации.

Пс основному авт, св. № 881783 известно устройство для моделирования пейсмекерного нейрона, содержа щее источник напряжения, выходкоторого подключен к первым входам двух сумматоров и двух управляемых интеграторов, второй и третий выход каждого сумматора и каждого управляемого Интегратора соединен с выхо дом соответствующего преобразователя частоты в напряжение, вход которого подключен к соответствующему

источнику импульсов, выход первого управляемого интегратора соединен с первым входом первого блока сравнения, выход которого через преобразователь напряжения в частоту подключен к входу формирователя выходных импульсов, выход которого является выходом устройства, выход первого блока сравнения соединен с управляющим входом ключа, информационный

10 вход которого соединен с выходом первого сумматора, выход ключа соединен со вторым входом первого блока сравнения, выход которого соединен с четвертым входом первого управля15емого интегратора, выход которого через элемент задержки соединен с четвертым входом второго управляемого интегратора, выход, которого соединен с первым входом второго сумма20тора, выход второго блока, сравнения соединен с пятым входом первого управляемого интегратора. Известное

устройство работает в двух режимах, В автономном режиме, при отсутствии информационных сигналов на входах преобразователей частоты а напряжение, на выходе устройства образуется простая дискретная последовательност сформированных в залпы (пачки) импульсов, характеристика которой, продолжительность пачк, число импульсов в пачке, интервал между пачка- ми зависит от постоянных величин, как веса входов и входного напряжения. При подаче информационных сигналов на входы устройства фоновая последовательность перестраивается в сложный ритм пачек импульсов, характер которого зависит от пространственно-временной характеристики входных си гналов„ Устройство может применяться как для управления ритмом работы нейронных сетей, так и для кодирования входной информации 1

Однако для управления сложным комплексом нейронных сетей и синхронизации их работы необходимо располагать ритмозадающими механизмами сложной периодической последовательности, которая легко бы перестраивалась без больших информационных затрат, т,е„ простыми сигналами В этом устройстве такая перестройка возможна лишь при условиях подами на входы устройства сигналов, меняющихся в определенной последовательности, что влечет а собой- информационные и материальные затраты, уменьшить которые возможно за смет расширения автономного режима работы устройства.

Цель изобретения - повышение точности моделирования ритмозадающих функций центральной нервной системы за счет моделирования сложных периодических последовательностей пейомекерного нейрона в автономном режиме его работы

Указанная цель достигается тем, что в устройство дополнительно введены блок запоминания, второй ключ, третий сумматор, второй элемент задержки и комму lOp, сигнальный .выход которого подключен к управляющему входу второго ключа, выход которого соединен с первым входом тре тьего сумматора, выход которого подключен к информационному входу благ: ка запоминания, выход которого соединен с:информационным входом комMyTatopa и через второй элемент задержки - с вторым входом третьего

сумматора, информационные выходы коммутатора подключены соответственно к дополнительным информационным входам первого и второго сумматоров и первого и второго управляемых интеграторов, информационный вход второго ключа соединен с выходом источника питания, первый управляющий вход блока запоминания подключен к выходу первого блока сравнения, второй управляющий вход блока запоминания и коммутирующие входы коммутатора соединены с соответствующими управляющими входами устройства

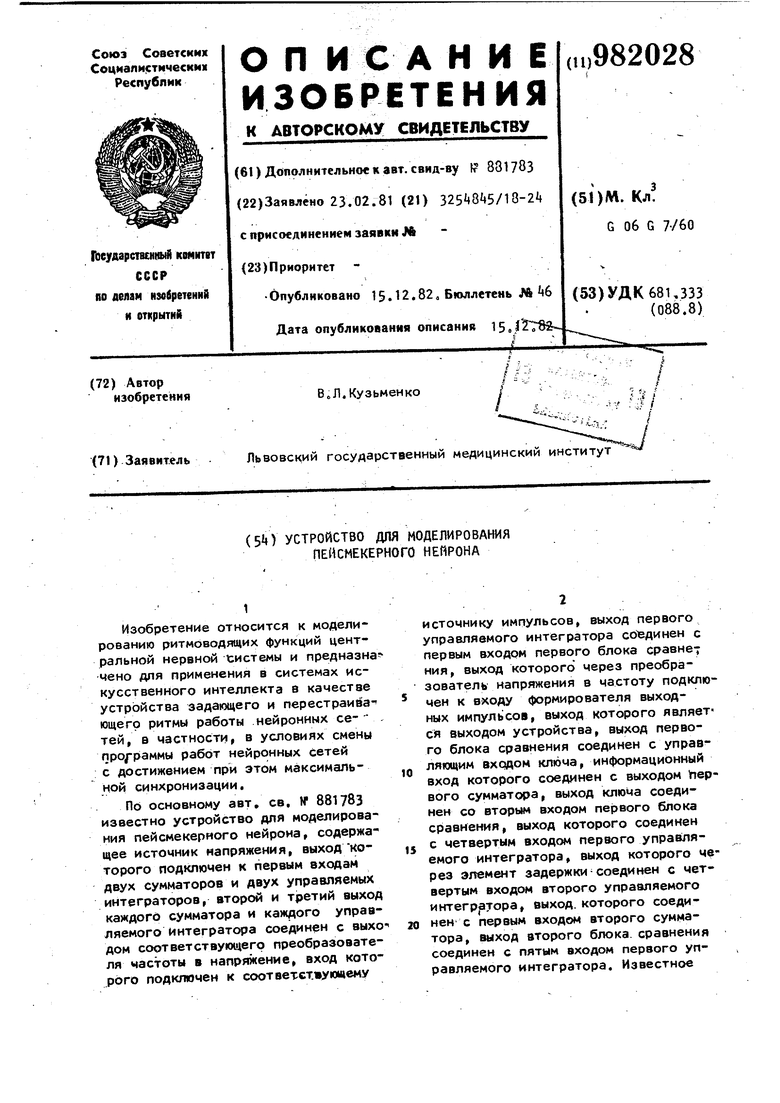

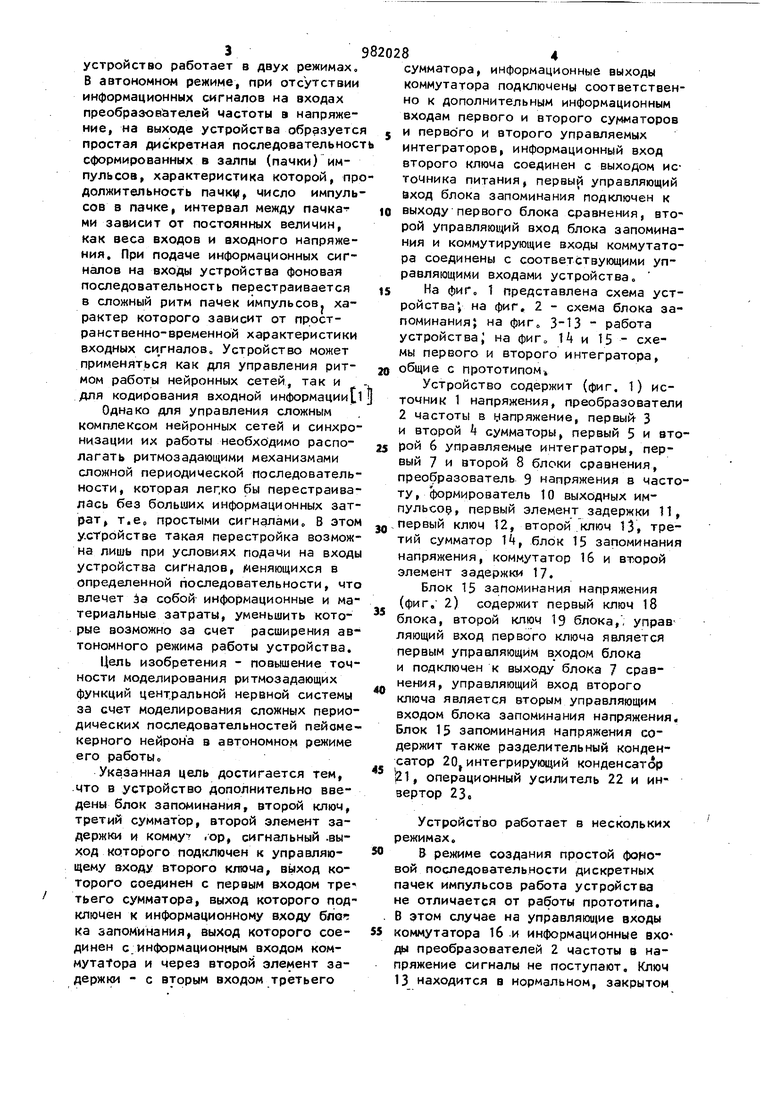

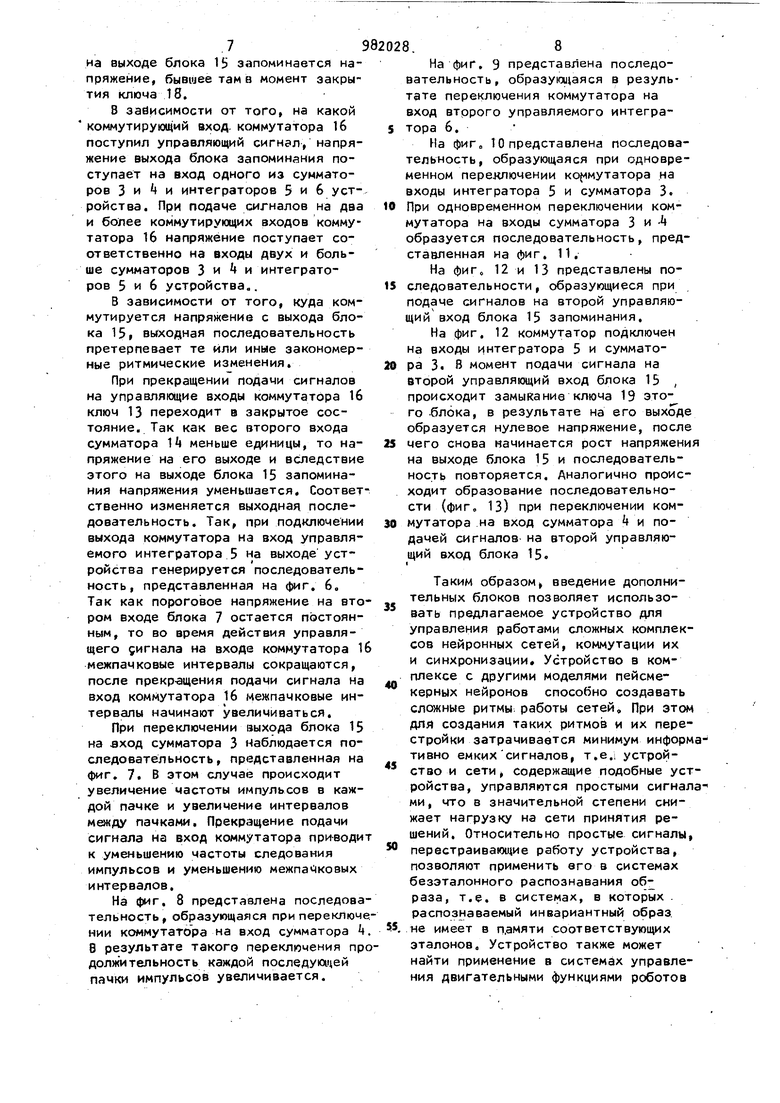

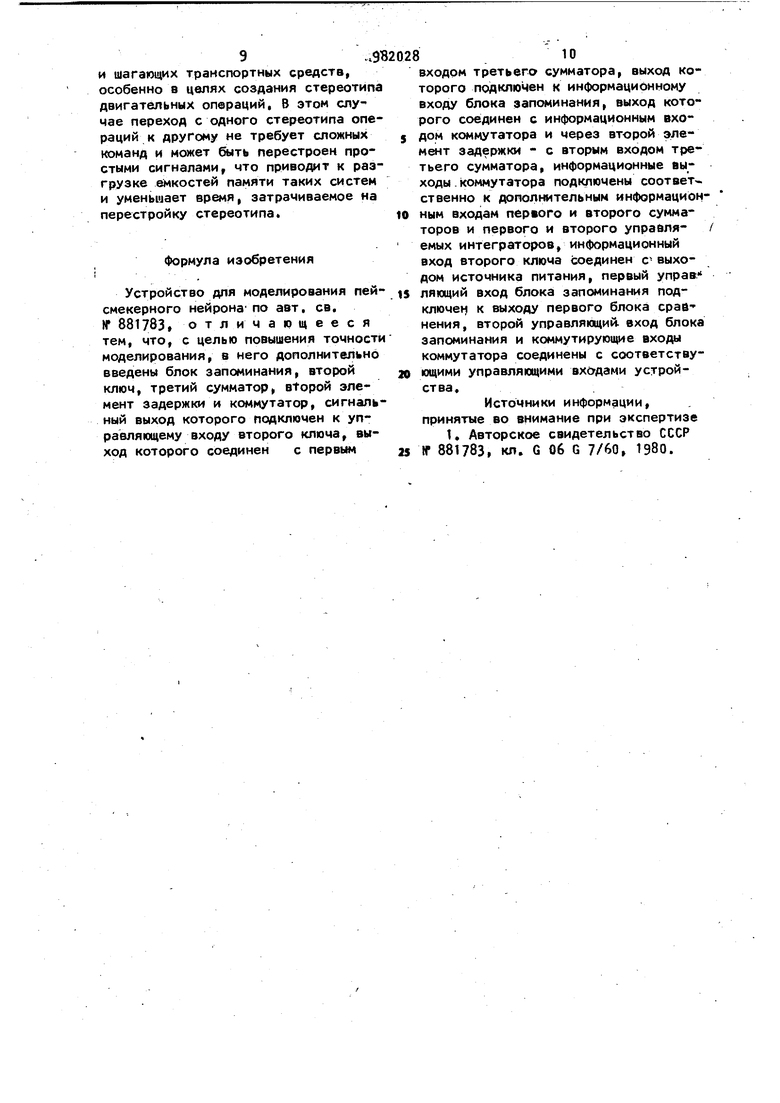

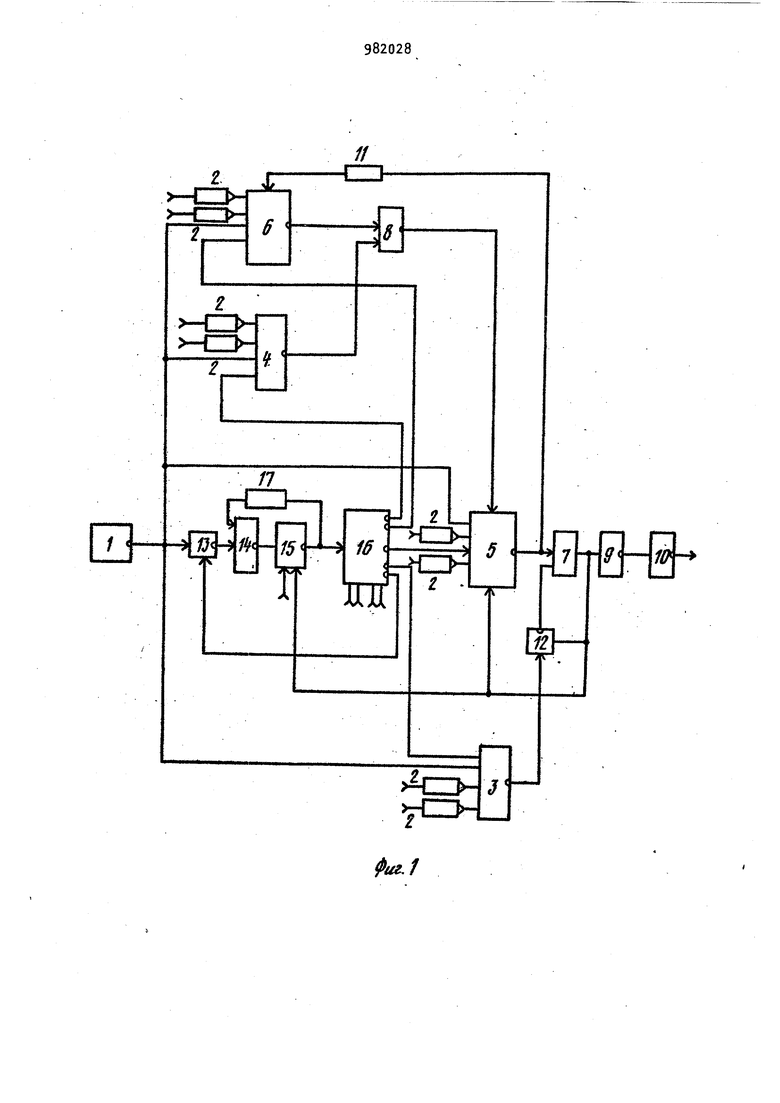

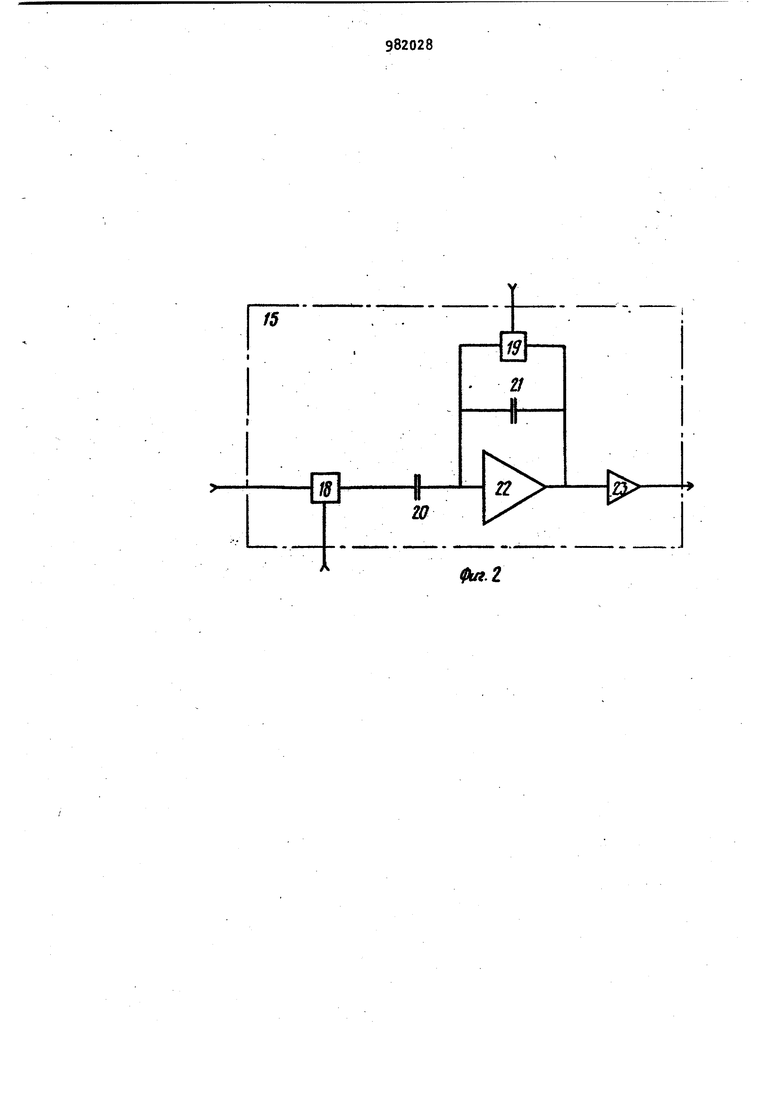

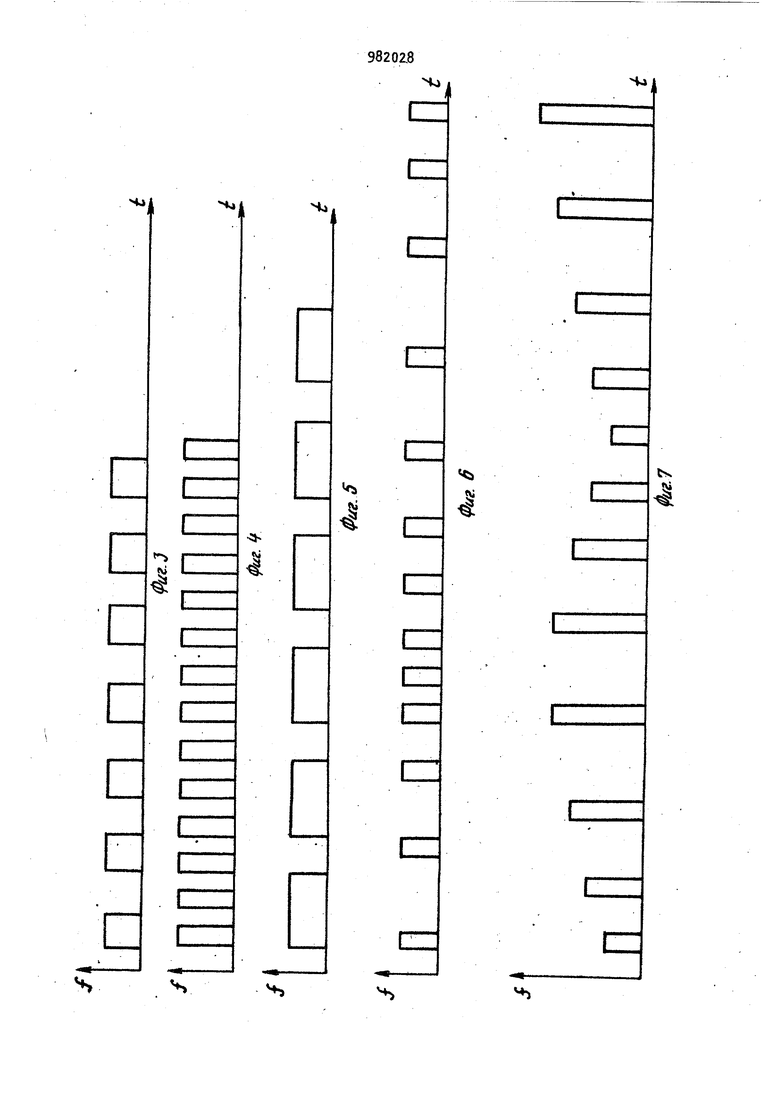

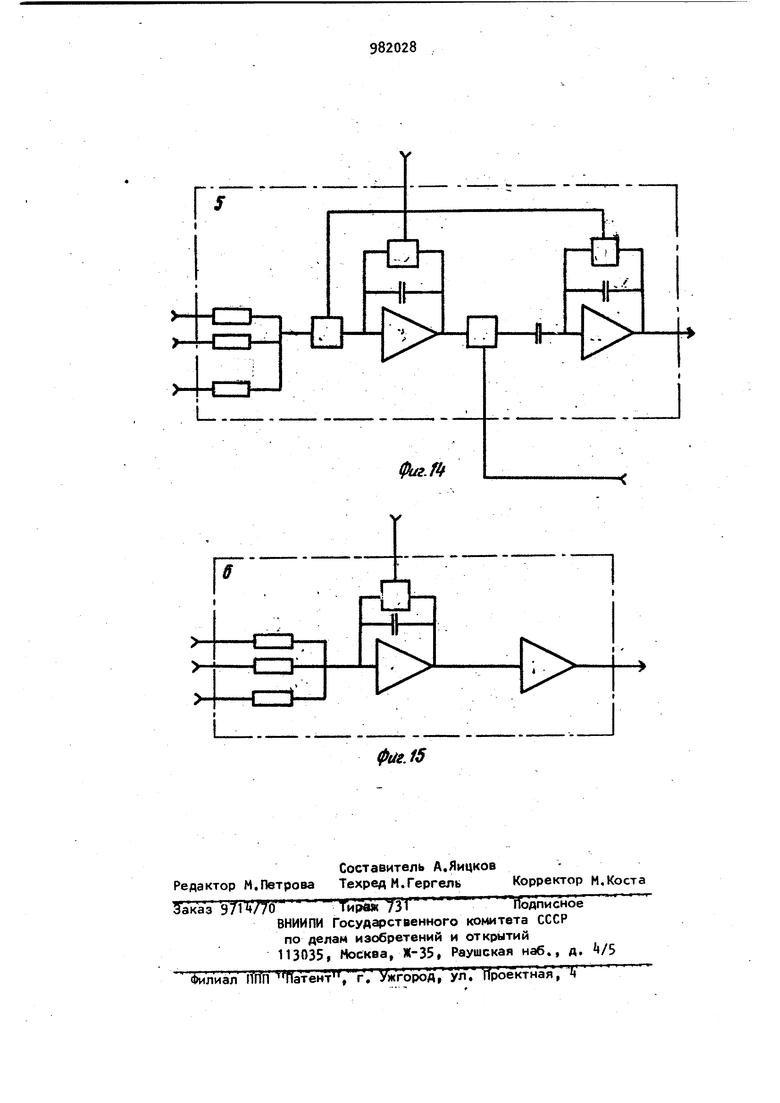

На фиг. 1 представлена схема устройства; на фиг, 2 - схема блока запоминания} на фиг, 3-13 - работа устройства; на фиг„ 14 и 15 - схемы первого и второго интегратора, общие с прототипомi

Устройство содержит (фиг. 1) источник 1 напряжения, преобразователи 2 частоты в уапряжение, первый- 3 и второй k сумматоры, первый 5 и второй 6 управляемые интеграторы, первый 7 и второй В блоки сравнения, преобразователь 9 напряжения в частоту , формирователь 10 выходных импульсор, первый элемент задержки 11, ,первый ключ 12, второй .ключ 13| третий сумматор 14, блок 15 запоминания напряжения, коммутатор 16 и элемент задержки 17.

Блок 15 запоминания напряжения (фиг, 2) содержит первый ключ 18 блока, второй ключ 19 блока,; управ ляющий вход первого ключа является первым управляющим входом блока и подключен к выходу блока 7 сравнения, управляющий вход второго ключа является вторым управляющим входом блока запоминания напряжения. Блок 15 запоминания напряжения содержит также разделительный конденсатор 20. интегрирующий конденсатор , операционный усилитель 22 и инвертор 23с

Устройство работает а нескольких режимах,

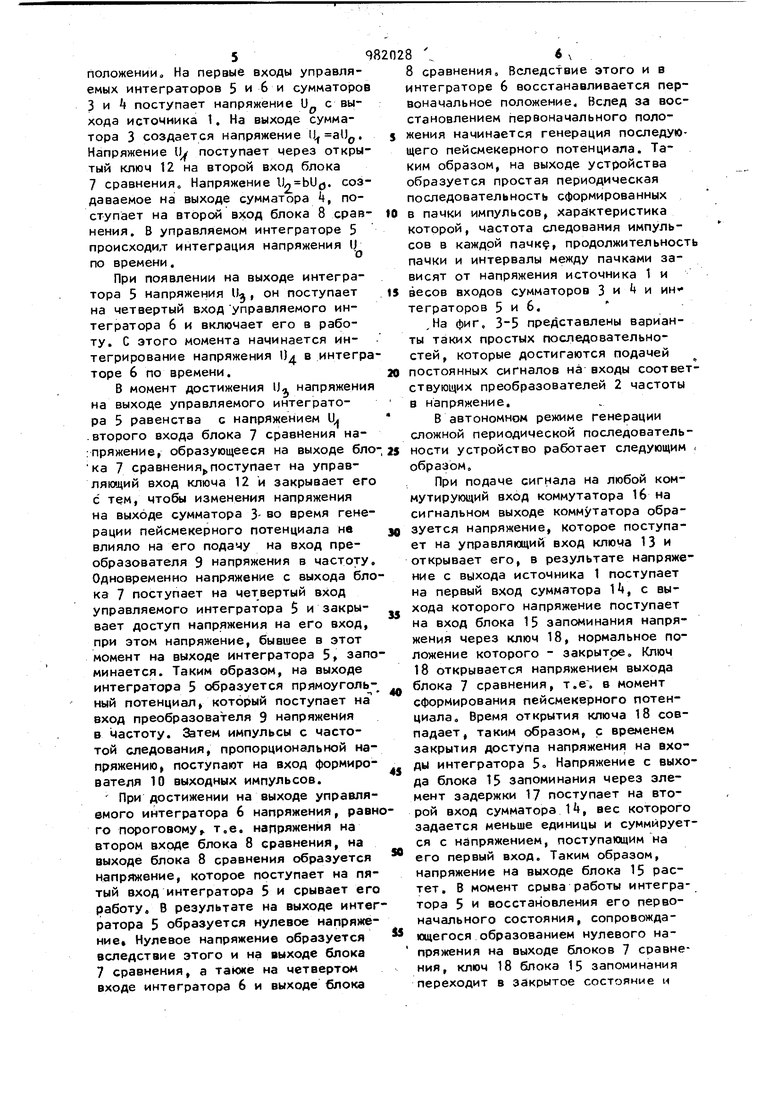

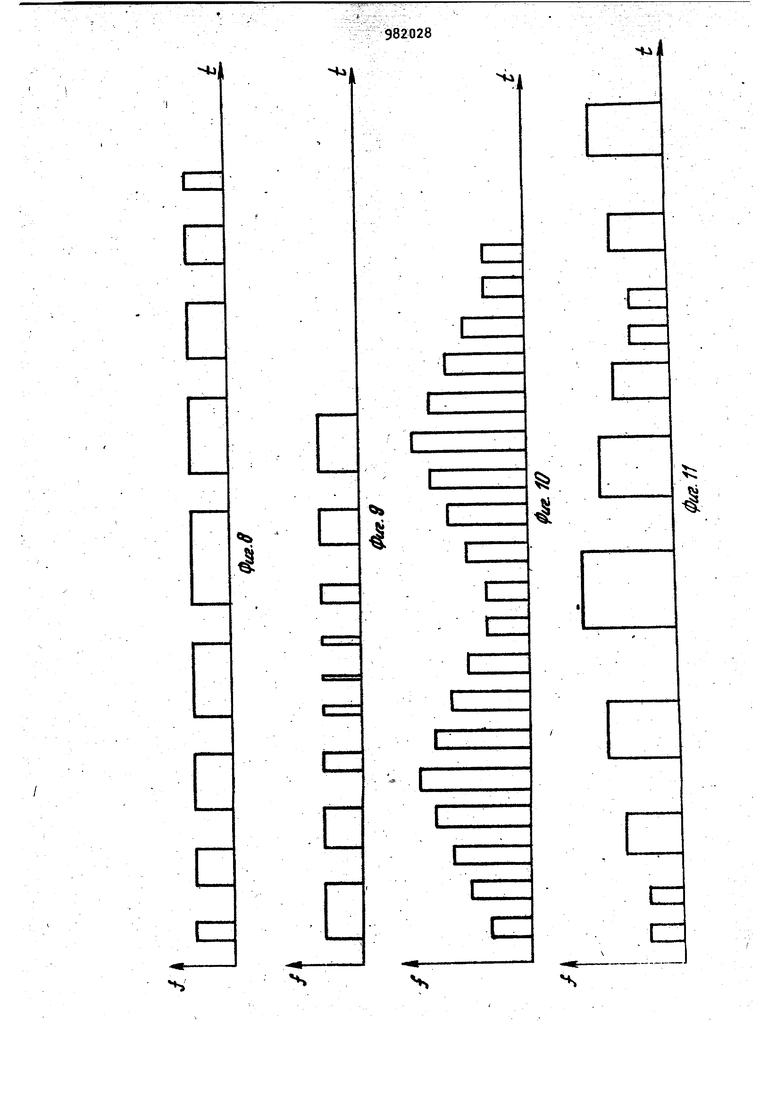

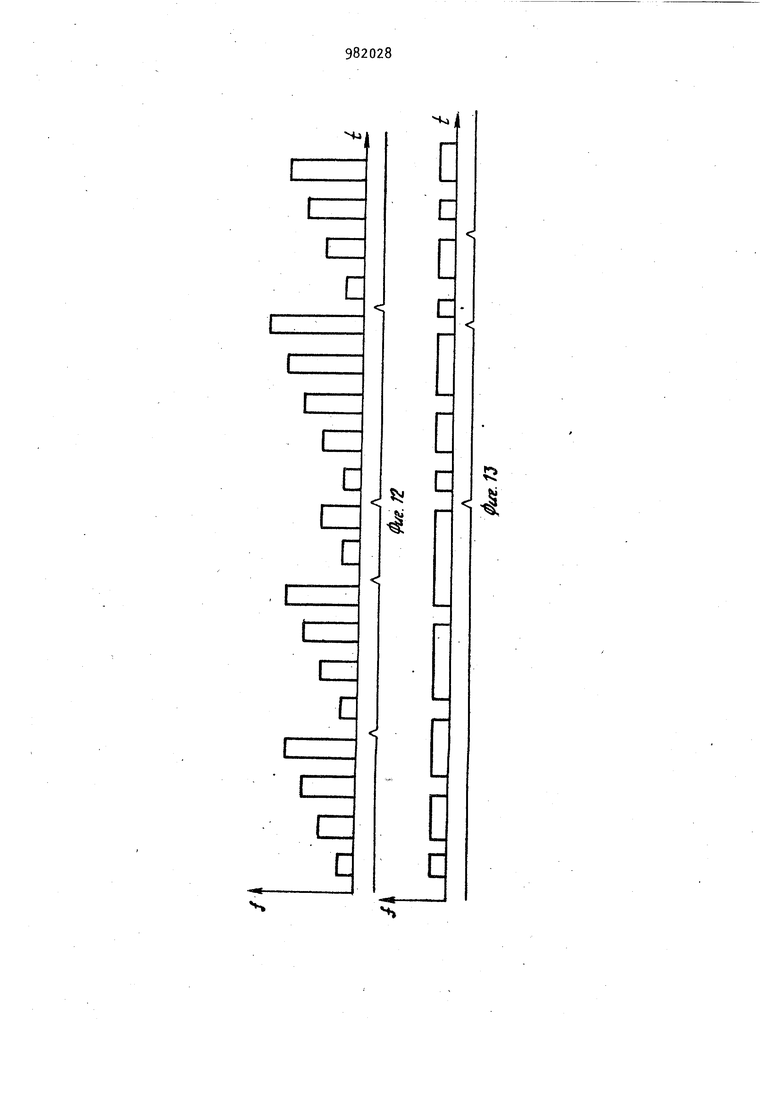

В режиме создания простой фоновой последовательности дискретных пачек импульсов работа устройства не отличается от работы прототипа, В этом случае на управляющие входы коммутатора 16 и информационные входа преобразователей 2 частоты в напряжение сигналы не поступают. Ключ 13 находится в нормальном, закрытом положении. На первые входы управляемых интеграторов 5 и 6 и сумматоро 3 и поступает напряжение U., с выхода источника 1. На выходе сумматора 3 создается напряжение 1) aUp. Напряжение 1) поступает через откры тый ключ 12 на второй вход блока 7 сравнения. Напряжение 1)(). соз даваемое на выходе сумматора k, поступает на второй вход блока 8 срав нения. В управляемом интеграторе 5 происходи,т интеграция напряжения по времени. При появлении на выходе интегратора 5 напряжения U, он поступает на четвертый вход управляемого интегратора 6 и включает его в работу. С этого момента начинается интегрирование напряжения } в интегр торе 6 по времени. В момент достижения Ij напряжени на выходе управляемого интегратора 5 равенства с напряжением U| . второго входа блока 7 сравнения на:пряжение, образующееся на выходе бл ка 7 сравнения поступает на управляющий вход ключа 12 и закрывает его с тем, чтобы изменения напряжения на выходе сумматора 3- во время генерации пейсмекерного потенциала не влияло на его подачу на вход преобразователя 9 напряжения в частоту. Одновременно напряжение с выхода бло ка 7 поступает на четвертый вход управляемого интегратора 5 и закрывает доступ напряжения на его вход, при этом напряжение, бывшее в этот момент на выходе интегратора 5, запо минается. Таким образом, на выходе интегратора 5 образуется прямоугольный потенциал, кото| ый поступает на вход преобразователя 9 напряжения в частоту. Затем импульсы с частотой следования, пропорциональной напряжению, поступают на вход формирователя 10 выходных импульсов. При достижении на выходе управляемого интегратора 6 напряжения, равн го пороговому т.е. напряжения на втором входе блока 8 сравнения, на выходе блока 8 сравнения образуется напряжение, которое поступает на пятый вход интегратора 5 и срывает его работу, В результате на выходе интег ратора 5 образуется нулевое напряжение Нулевое напряжение образуется вследствие этого и на выходе блока 7 сравнения, а также на четвертом входе интегратора 6 и выходе блока 8 сравнения. Вследствие этого и в интеграторе 6 восстанавливается первоначальное положение. Вслед за восстановлением первоначального положения начинается генерация последующего пейсмекерного потенциала. Таким образом, на выходе устройства образуется простая периодическая последовательность сформированных в пачки импульсов, характеристика которой, частота следования импульсов в каждой пачк, продолжительность пачки и интервалы между пачками зависят от напряжения источника 1 и весов входов сумматоров 3 и + и ин теграторов 5 и 6. ,На фиг, 3-5 представлены варианты таких простых последовательностей, которые достигаются подачей постоянных сигналов на входы соответствующих преобразователей 2 частоты в напряжение. В автономном режиме генерации сложной перисдической последовательности устройство работает следующим образом. При подаче сигнала на любой коммутирующий вход коммутатора 16 на сигнальном выходе коммутатора образуется напряжение, которое поступает на управляющий вход ключа 13 и открывает его, в результате напряжение с выхода источника 1 поступает на первый вход сумматора Т, с выхода которого напряжение поступает на вход блока 15 запоминания напряжения через ключ 18, нормальное положение которого - закрытое. Ключ 18 открывается напряжением выхода блока 7 сравнения, т.е . в момент сформирования пейсмекерного потенциала. Время открытия ключа 18 совпадает, таким образом, с временем закрытия доступа напряжения на входы интегратора 5. Напряжение с выхода блока 15 запоминания через элемент задержки 17 поступает на второй вход сумматора 1, вес которого задается меньше единицы и суммируется с напряжением, поступающим на его первый вход. Таким образом, напряжение на выходе блока 15 растет, В момент срыва работы интегратора 5 и восстановления его первоначального состояния, сопровождающегося образованием нулевого напряжения на выходе блоков 7 сравнения, ключ 18 блока 15 запоминания переходит в закрытое состояние и 7 на выходе блока 15 запоминается напряжение, быв1иее там в момент закрытия ключа 18. 8 зайисимости от того, на какой коммутирующий вход коммутатора 16 поступил управляющий сигнал, напряжение выхода блока запоминания поступает на вход одного из сумматоров 3 и и интеграторов 5 и 6 устроиства. При подаче сигналов на два и более коммутирующих входов коммутатора 16 напряжение поступает соответственно на входы двух и больше сумматоров 3 и 4 и интеграторов 5 и 6 устройства,. В зависимости от того, куда коммутируется напряжение с выхода блока 15, вы ходная последовательность претерпевает те или иные закономерные ритмические изменения. При прекращении поДачи сигналов на управлякмдие входы коммутатора 16 ключ 13 переходит в закрытое состояние. Так как вес второго входа сумматора Ц меньше единицы, то напряжение на его выходе и вследствие этого на выходе блока 15 запоминания напряжения уменьшается. Соответ ственно изменяется выходная последовательность. Так, при подключении выхода коммутатора на вход управляемого интегратора 5 на выходе устройства генерируется последовательность, представленная на фиг. 6. Так как пороговое напряжение на вто ром входе блока 7 остается постоянным, то во время действия управлящего сигнала на входе коммутатора 1 межпачковые интервалы сокращаются, после прекращения подачи сигнала на вход коммутатора 16 межпачковые интервалы начинают увеличиваться. При переключении выхода блока 15 на вход сумматора 3 наблюдается последовательность, представленная на фиг. 7. В этом случае происходит увеличение частоты импульсов в каждой пачке и увеличение интервалов мзкду пачками. Прекращение подачи сигнала на вход коммутатора при-води к уменьшению частоты следования импульсов и уменьшению межпа ковых интервалов. На фиг. 8 представлена последова тельность, образующаяся при перекЛюч НИИ коммутатора на вход сумматора i 8 результате такого переключения пр должительность каждой последующей пачки импульсов увеличивается. На фиг. 9 представлена последовательность, образующаяся в результате переключения коммутатора на вход втррого управляемого интегратора 6. На фиг„ 10 представлена последовательность, образующаяся при одновременном переключении ко{ мутатора на входы интегратора 5 и сумматора 3. При одновременном переключении коммутатора на входы сумматора 3 и образуется последовательность, представленная на фиг, 11, На фиг о 12 и 13 представлены последовательности, образующиеся при подаче сигналов на второй управляющий вход блока 15 запоминания. На фиг. 12 Коммутатор подключен на входы интегратора 5 и сумматора 3. В момент подачи сигнала на второй управляющий вход блока 15 , происходит замыкание ключа 19 этого -блока, в результате на его выходе образуется нулевое напряжение, после чего снова начинается рост напряжения на выходе блока 15 и последовательность повторяется. Аналогично происходит образование последовательности (фиго 13) при переключении коммутатора на вход сумматора 4 и подачей сигналов на второй управляющий вход блока 15« Таким образом, введение дополнительных блоков позволяет использовать предлагаемое устройство для управления работами сложных комплексов нейронных сетей, коммутации их и синхронизации. Устройство в комплексе с другими моделями пейсмекерных нейронов способно создавать сложные ритмы работы сетей. При этом для создания таких ритмов и их перестройки затрачивается минимум информативно емкихсигналов, т.е.; устройство и сети, содержащие подобные устройства, управляются простыми сигнала ми, что в значительной степени снижает нагрузку на сети принятия решений. Относительно простые сигналы, перестраиваюи ие работу устройства, позволяют применить его в системах безэталонного распознавания образа, т.е. в системах, в которых . распознаваемый инвариантный образ не имеет в п.амяти соответствующих эталонов. Устройство также может найти применение в системах управления двигательными функциями роботов

и шагающих траиспортных средств, особенно в целях создания стереотипа двигательных операций, В этом слу чае переход с одного стереотипа операций к другому не требует сложных команд и может быть перестроен простыми сигналами г что приводит к разгрузке емкостей памяти таких систем и уменьшает время, затрачиваемое на перестройку стереотипа.

Формула изобретения

Устройство для моделирования пейсмекерного нейрона по авт. св. VF 881783 отличающееся тем, что, с целью повышения точности моделирования, в него дополнительно введены блок запоминания, второй ключ, третий сумматор, вtopoй элемент задержки и коммутатор, сигнальный выход которого подключен к управляющему входу второго ключа, выход которого соединен с первым

входом третьего сумматора, выход которого подключен к информационному входу блока запоминания, выход которого соединен с информационным входом коммутатора и через второй элемент задержки - с вторым входом третьего сумматора, информационные выходы . коммутатора подключены соответ ственно к дополнительным информационным входам первого и второго сумматоров и первого и второго упра&ля- / емых интеграторов, информационный вход второго ключа соединен с выходом источника питания, первый управ.

ляющий вход блока запоминания подключен к выходу первого блока срав- нения, второй управляющий, вход блока запоминания и коммутируюиие входы коммутатора соединены с соответствующими управляющими входами устройства

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР

tr 881783, кл. G Об G 7/60, 1980.

-ЕШ л rCb-i n n - ;

J

fS

2/

4w

«te.Z

4u

Ns)

ts.

4

tvi

I

SJ

HJ

fe

4

a

X

NJ

п

с

фаг. 15

Авторы

Даты

1982-12-15—Публикация

1981-02-23—Подача